TDM控制模塊是VoIP網關系統設計中的重要部分,是連接來自PSTNPublic Switched TelephoneNetwork)串行的TDM數據格式和并行的Wishbone數據格式的橋梁,實現兩邊數據跨時鐘域無丟失的轉換。為滿足高速數據轉換的要求,采用了Wishbone總線,將多個IP核集成為VoIP網關系統。

Wishbone最先是由Silicore公司提出,現在已被移交給OpenCores組織維護。Wishbone總線規范是一種片上系統IP核互連體系結構,定義了一種IP核之間共公的邏輯接口,可用于軟核、固核和硬核,對開發工具和目標硬件沒有特殊要求,并且幾乎兼容已有所有的綜合工具,可以用多種硬件描述語言來實現。

TDM控制模塊的設計

● TDM在VoIP語音網關系統中的作用

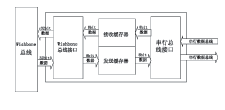

TDM控制模塊同時接收來自ISDN(綜合業務數字網)、E1專線或者語音編碼器等不同信源的串行語音數據。如圖1,VoIP語音網關的基本功能是完成以太網數據與外部語音設備數據的轉換,TDM接口與以太網接口分別為外部語音設備的數據、以太網上數據與網關系統的通信橋梁。該網關SoC系統的處理器采用的是同濟大學微電子中心自主沿發的高性能低功耗的32位嵌入式CPU BC320。

圖1 TDM控制模塊的作用

● 時分復用原理與TDM數據頻率

時分復用是把對信道的使用時間劃分為多個時間幀,進一步把時間幀劃分為n個時間隙(時間間隔)。每一個時間隙分配給一個子信道,從而實現在一個信道上同時傳輸多路信號。時分復用循環使用時間幀,各路信號循環順序插入時間幀中的時間隙傳輸。TDM控制模塊的主要作用就是復用多路信號與解復用混合有多路信號的 TDM數據,如圖2所示。

圖2 時分復用的時隙

本設計的串行語音數據針對E1專線標準,E1主要應用于歐洲,中國也采用該標準。E1標準的數據率為2.048Mb/s,每一個時間幀包括30個B子信道,一個D子信道和一個同步子信道,共32個子信道。以語音模擬信道為例,信道帶寬限制為3.4kHz,根據奈圭斯特定律,子信道采樣速率至少是信號最高頻率的兩倍,通常選擇采樣速率為8kHz。因此,整個TDM信道的比特速率可以達到:

8kb/s×8×32=2048kb/s=2.048 Mb/s,即E1標準規定的TDM數據率。

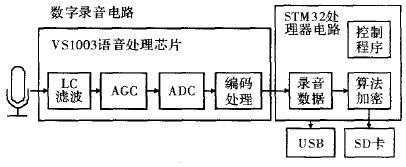

● 模塊設計

模塊的主要功能是完成多路數據的復用和復用數據的分解,其關鍵部分就是復用和分解。本設計采用緩存器輔助完成復用和分解,實現兩種協議數據跨時鐘域的轉換。本設計模塊主要分三部分,見圖3。

圖3 TDM接口控制模塊的基本結構

串行數據接口主要負責串行數據與8位寬并行數據的轉換,因為存放數據的FIFO是以8bit為一地址空間的。轉換由設計的狀態機來控制:接收 (receive)操作、發送(transmit)操作和等待,接收就是將串行數據轉換成8bit位寬數據的過程,發送與之相反。由于語音數據要求雙工機制,由時鐘高低電平來作為發送和接收狀態的切換信號,即當時鐘為低時由發送狀態轉為接收狀態,當時鐘為高時,由接收狀態切換為發送狀態,這樣可以看作接收與發送是同時進行的。

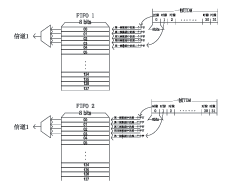

發送、接收緩存器不僅包括用于暫時存儲數據的FIFO,而且還設計有狀態機來控制接收、發送數據流。由于跨時鐘域,由雙口RAM組成的FIFO可能會帶來地址比較沖突的問題,本設計采用乒乓機制來完成FIFO,當一個緩存器進行讀操作時,另一個緩存器則進行寫操作,兩者的切換由硬件來完成。以下以接收緩存器為例(數據方向從TDM串行數據到Wishbone總線并行數據)來描述本設計。緩存器的大小設計為包含四幀TDM數據,因此每個FIFO的大小為 8bit×32×4=1024bit,如圖4。選用乒乓FIFO以及FIFO大小設計的原因如下。

圖4 乒乓FIFO

串行數據的時鐘相對于Wishbone總線的時鐘要慢,當兩時鐘域上的數據相互轉換時,Wishbone總線可以在很短時間內讀寫FIFO,而串行總線需要相對較長的時間讀寫相同數據量。盡管如此,在Wishbone總線時鐘頻率相對較慢時,Wishbone總線很可能在下一批串行數據寫進FIFO前不能完全讀空FIFO。以接收緩存器為例,如果不考慮處理器(BC320)中斷響應時間和從RAM讀數據的時間(待處理的數據都要先暫存在Wishbone 總線上掛的RAM中),從Wishbone總線讀空一個FIFO中的四幀數據需要時間為:

1/25M x 32 x 4 = 5.12 x 10-6 s= 5.12us

25M是本設計在FPGA開發板進行測試時所采用的時鐘頻率,即測試系統時Wishbone總線上的時鐘頻率。 而在另一邊串行數據,當四幀寫滿FIFO后,第五幀的第一個字節數據開始寫入FIFO的準備時間為:

1/24M x 8 = 4 x 10-6?s = 4us

FIFO中的四幀數據被讀空時間大于第五幀的第一個字節寫入FIFO的準備時間,FIFO的寫滿與讀空都是有硬件產生信號標識,此時FIFO讀空信號標識未產生,不能對同一FIFO進行寫操作,導致待寫數據丟失。因此選用兩個FIFO采用乒乓機制來切換讀寫操作,如圖4所示。

在解復用時,數據的地址恢復很重要,一個TDM數據幀含有32個時隙,每一時隙中的數據均來自不同的信道源,本模塊要將復用在一路的TDM數據恢復出32 路。TDM數據的每個時隙含8個bit,而Wishbone總線的數據位寬是32位,因此需要四幀的TDM數據才能拼接成一路完整32位寬數據。相鄰時隙數據由于來自不同信道源,暫存在FIFO中的地址不能相鄰,前一時隙中數據和后一時隙中數據在地址空間上相差4(如圖4),這樣從初始地址開始,每相鄰四個地址對應的數據拼接成一路完整的信號,在Wish

bone總線讀取FIFO中數據時的地址是按順序的。

本文著重討論了接收緩存器的設計,發送緩存器與之類似,這里就不再贅述。

Wishbone接口連接TDM控制模塊與Wishbone總線,它的主要功能是設計正確的狀態機產生有效控制信號來同步數據交換。

驗證與結論

用Verilog語言描述完成TDM控制模塊的設計,并以VoIP語音網關系統為驗證平臺,利用Candence公司的NC-verilog仿真器進行代碼仿真。仿真波形表明,處理器(BC320)對FIFO寫滿產生信號標識的反應時間大約為60個Wishbone總線時鐘周期,這一時間加上 Wishbone總線讀空第一個FIFO所用時間后,串行語音數據仍在寫進另一個FIFO,Wishbone總線有足夠的空閑等待這個FIFO寫滿標示信號的產生,不會有任何數據丟失。

VoIP語音網關系統在型號為Virtex-II Pro FF1152的FPGA開發板上進行了硬件驗證,TDM控制模塊外接型號為Le88221的SLIC(用戶線接口電路)芯片作為語音信源,利用 Chipscope在線掃描TDM控制模塊內部、Wishbone總線和處理器(BC320)寄存器的信號變化,并用示波器對SLIC芯片信號進行捕捉。從觀察的信號來看,所設計的TDM控制模塊能夠與系統的其他IP模塊,尤其是處理器(BC320)和以太網模塊正確有效地協同工作,模塊的功能達到設計要求。

責任編輯:gt

-

處理器

+關注

關注

68文章

19178瀏覽量

229202 -

FPGA

+關注

關注

1626文章

21678瀏覽量

602047 -

開發板

+關注

關注

25文章

4959瀏覽量

97217

發布評論請先 登錄

相關推薦

一個簡單的8位處理器完整設計過程及verilog代碼

TMS320C6678處理器的VLFFT該怎么演示?

Cortex-M3處理器是什么

RK3399處理器與AR9201處理器有哪些不同之處呢

ARM Cortex-M4處理器的參數傳遞機制是怎樣的

Sitara AM62處理器的資料分享

Verilog HDL語言實現時序邏輯電路

蘋果a6處理器怎么樣_a6處理器參數

麒麟9000處理器和高通驍龍875處理器相比如何?

ADuCM320:精密模擬微控制器,14位模擬I/O, 帶MDIO接口、ARM Cortex-M3處理器

基于BC320處理器和Verilog語言實現TDM控制模塊的設計

基于BC320處理器和Verilog語言實現TDM控制模塊的設計

評論