1 概述

隨著微電子技術(shù)的快速發(fā)展,可編程芯片的處理能力也在不斷加強(qiáng),尤其是DSP芯片正在朝著高速,多指令并行執(zhí)行的方向發(fā)展。DSP處理能力的增強(qiáng),使得原來運(yùn)算量很大的算法可以用軟件的方式快速實(shí)現(xiàn)。由于軟件處理的靈活性,這給整體的無線電體系結(jié)構(gòu)帶來了深刻的變化。

軟件無線電是指一種基于可編程的,具有一定靈活性的高速信號(hào)處理平臺(tái)。處理平臺(tái)上的設(shè)備都可以進(jìn)行重新配置,將通用化、模塊化、標(biāo)準(zhǔn)化的算法單元用軟件方式實(shí)現(xiàn),根據(jù)系統(tǒng)的實(shí)際需要,在軟件中添加各種不同算法,可以完成特定的功能,因而可以跨越多種通信標(biāo)準(zhǔn)。當(dāng)需要從一種標(biāo)準(zhǔn)切換至另一種標(biāo)準(zhǔn)時(shí),處理器能夠動(dòng)態(tài)的在軟件的主要部分切換[1“5]。

2 系統(tǒng)結(jié)構(gòu)設(shè)計(jì)

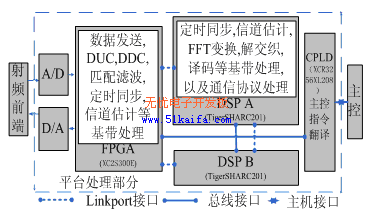

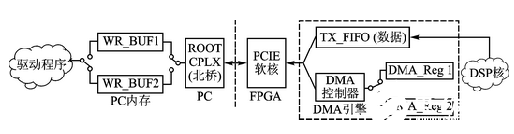

本平臺(tái)主要針對(duì)寬帶無線數(shù)字通信系統(tǒng)物理層的中頻和基帶單元的數(shù)字信號(hào)處理,如圖1所示,平臺(tái)上有兩個(gè)DSP(ADI,TigerSHARC201),一個(gè)FPGA(Xilinx XC2S300E)和一個(gè)CPLD(Xilinx XCR3256XL208)。依據(jù)信號(hào)處理各模塊的運(yùn)算特點(diǎn),以及器件特點(diǎn),我們將不同的模塊選擇在不同的器件中完成。FPGA設(shè)置靈活,但是主頻很難做高,通常低于120MHz,適合于處理可并行計(jì)算的模塊;而DSP主頻很高,主要以串行方式執(zhí)行指令,且DSP支持C語言,所以便于處理通信協(xié)議。基于以上特點(diǎn),F(xiàn)PGA適合處理發(fā)送端數(shù)據(jù)以及數(shù)字上變頻(DUC);在接收端適合處理數(shù)字下變頻(DDC),匹配濾波器,定時(shí)同步等其它基帶處理模塊。DSP適合定時(shí)同步,信道估計(jì),F(xiàn)FT變換,解交織,譯碼等其它基帶處理模塊,以及通信協(xié)議處理。而CPLD由于其器件特性限制,一般用作主控模塊或主控指令翻譯器。

現(xiàn)代寬帶無線數(shù)字通信系統(tǒng)要盡量使用數(shù)字信號(hào)處理方法來增加可靠性,因此要使用寬帶A/D和D/A,但是由于器件性能局限,我們一般情況下選擇在中頻處使用A/D,D/A。本平臺(tái)A/D使用12bit的AD9235,最高采樣率為65MSPS,如果中頻低于65MHz,我們可直接對(duì)中頻信號(hào)進(jìn)行采樣,如果中頻頻率較高,可以采用帶通采樣的方法。D/A使用14bi的AD9857,200MSPS,實(shí)現(xiàn)中頻輸出。

圖1:平臺(tái)結(jié)構(gòu)圖

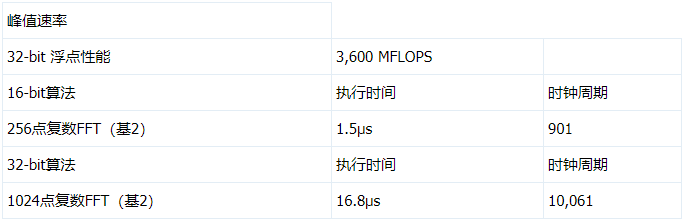

寬帶無線數(shù)字通信系統(tǒng)的一般基帶處理算法中主要分為碼片級(jí)處理和符號(hào)級(jí)處理,同時(shí)還有通信協(xié)議處理。碼片級(jí)信號(hào)處理的特點(diǎn)是運(yùn)算量大,比如定時(shí)同步等,所以在以往的系統(tǒng)中大多采用FPGA或ASIC來實(shí)現(xiàn),但是本平臺(tái)上的高性能DSP中設(shè)置了一些特殊單元,完全可以滿足碼片級(jí)處理的要求,表1為DSP處理能力的峰值指標(biāo),從此表中我們可以看到其強(qiáng)大的處理能力。符號(hào)級(jí)處理比如譯碼等,相對(duì)來說處理量不是很大,此DSP還提供了增強(qiáng)的指令,使得Viterbi和Turbo碼解碼更快。通信協(xié)議處理部分需要很多判斷,跳轉(zhuǎn)等操作,這部分如果使用FPGA或ASIC處理將使系統(tǒng)開發(fā)變得非常慢,而DSP可采用C語言,這點(diǎn)無疑非常適合于通信協(xié)議的處理。

表1:DSP處理能力指標(biāo)

注:此表中是DSP工作在600MHz時(shí)的數(shù)據(jù)

FPGA作為DSP的硬件協(xié)處理器能夠增強(qiáng)功能,改善吞吐量,減小系統(tǒng)成本。本平臺(tái)上的FPGA較小,只有100萬邏輯門,在此平臺(tái)上主要作為DSP的協(xié)處理器。CPLD為主要用于完成主控指令的轉(zhuǎn)換。

2.1 DSP體系結(jié)構(gòu)簡(jiǎn)介

平臺(tái)上使用的高性能DSP TigerSHARC201主頻600MHz,其主要特點(diǎn)是能夠進(jìn)行多指令并行執(zhí)行,芯片內(nèi)部集成了一些專用處理模塊,用以保證一些較為復(fù)雜的運(yùn)算指令也能在一時(shí)鐘周期處理完畢。

TigerSHARC201內(nèi)部主要模塊:(1)兩個(gè)運(yùn)算模塊,可以并行執(zhí)行計(jì)算,且每個(gè)運(yùn)算模塊每周期能完成2條運(yùn)算指令,大大增強(qiáng)了數(shù)字信號(hào)處理能力,支持定點(diǎn)和浮點(diǎn)運(yùn)算;(2)兩個(gè)整數(shù)ALU,能提供強(qiáng)大的地址產(chǎn)生能力和通用的整數(shù)操作;(3)六塊片內(nèi)DRAM共24M bit,每塊4Mbit,用于存儲(chǔ)指令和數(shù)據(jù),這種分塊DRAM結(jié)構(gòu)使得DSP可以在取指的同時(shí)訪問數(shù)據(jù);(4)三條相互獨(dú)立的128bit寬片內(nèi)數(shù)據(jù)總線,使得指令行能包括4個(gè)32bit指令,且提供了許多并行操作以簡(jiǎn)化編程。例如,一條指令行可以讓DSP有條件的在兩個(gè)運(yùn)算模塊中分別執(zhí)行乘,加和減操作,且可以同時(shí)跳轉(zhuǎn)到程序的其它地方。每條片內(nèi)數(shù)據(jù)總線都與六個(gè)片內(nèi)DRAM相連,用以保證片內(nèi)指令和數(shù)據(jù)的并行高效傳輸[6]。

TigerSHARC201外部接口:(1)一個(gè)總線接口,數(shù)據(jù)線可配置為64bit或32bit,地址線32bit;(2)四個(gè)Linkport接口,采用LVDS技術(shù),每個(gè)接口能提供額外的全復(fù)用4bit接收和發(fā)送能力,其最大傳輸速率500Mbytes/s,用于處理器間的點(diǎn)對(duì)點(diǎn)高速數(shù)據(jù)傳輸,為數(shù)據(jù)傳輸提供了又一種途徑,Linkport接口也是本平臺(tái)的最大特點(diǎn)之一[6]。

2.2 數(shù)據(jù)調(diào)度方法

數(shù)據(jù)調(diào)度的原則是:盡量減少芯片間的數(shù)據(jù)傳輸量。因?yàn)樾酒g的數(shù)據(jù)傳輸要走PCB板的數(shù)據(jù)線,其數(shù)據(jù)傳輸速率相對(duì)較低,而且過于頻繁的板級(jí)數(shù)據(jù)傳輸容易造成系統(tǒng)調(diào)度沖突,不便于處理。但是此DSP支持一個(gè)特殊的數(shù)據(jù)傳輸接口——Linkport接口,可以在很大程度上緩解此問題。

使用DSP的Linkport接口分別實(shí)現(xiàn)DSP與DSP,DSP與FPGA之間的點(diǎn)對(duì)點(diǎn)高速數(shù)據(jù)傳輸,這樣可滿足數(shù)據(jù)調(diào)度原則,使得系統(tǒng)總體調(diào)度變得較為簡(jiǎn)單。總線接口只要負(fù)責(zé)控制指令和小量數(shù)據(jù)的傳輸就可以了。如果兩個(gè)DSP要對(duì)同一批數(shù)據(jù)分別進(jìn)行處理,那么這時(shí)候就要走總線接口,使用廣播的方式進(jìn)行數(shù)據(jù)傳遞,即兩個(gè)DSP可以同時(shí)接收數(shù)據(jù),以減少數(shù)據(jù)調(diào)度。平臺(tái)上有兩個(gè)DSP,根據(jù)系統(tǒng)運(yùn)算量需求來確定使用一個(gè)或者兩個(gè)都用。DSP間可以形成了一個(gè)處理鏈,也可以配置成兩個(gè)DSP并行處理。

為了使得平臺(tái)便于調(diào)度,所以可在平臺(tái)上將FPGA或者一個(gè)DSP設(shè)置為從屬器件。在FPGA中設(shè)置控制寄存器和狀態(tài)寄存器,在從屬DSP中設(shè)置控制變量和狀態(tài)變量,DSP通過總線接口來讀寫這些寄存器或者變量以達(dá)到控制從屬器件的目的,這樣做相當(dāng)于硬件平臺(tái)上只有一個(gè)“大腦”,有利于減小硬件平臺(tái)調(diào)度沖突。同時(shí)FPGA還要通過總線接口接受CPLD(即主控)的控制。

2.3 控制信息處理機(jī)制

控制信息處理機(jī)制是指DSP作為硬件平臺(tái)的核心,如何控制其它從屬器件。一般主要有兩種方法:查詢模式和中斷模式。查詢模式是指從屬器件在特定時(shí)刻(一般為某個(gè)模塊處理完畢后)會(huì)主動(dòng)讀取DSP發(fā)送來的并已事先存儲(chǔ)在緩存中的指令,隨后執(zhí)行。中斷模式是指DSP發(fā)送的指令以中斷的形式強(qiáng)制從屬器件立即執(zhí)行,從而控制整個(gè)硬件平臺(tái)。

CPLD主要用來作為主控或者翻譯主控發(fā)來的指令,然后將控制信息傳遞給DSP和FPGA。這里CPLD可以直接通過總線接口控制FPGA,也可以通過DSP間接控制FPGA。

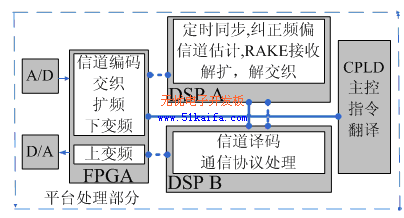

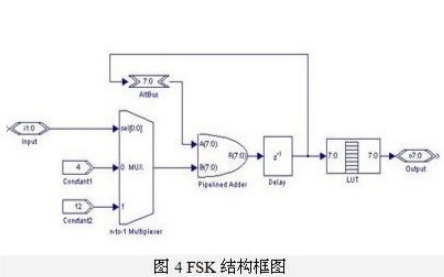

3 應(yīng)用于直接序列擴(kuò)頻系統(tǒng)

首先將各接收模塊信號(hào)運(yùn)算的特點(diǎn)以及FPGA和DSP的特性相結(jié)合,找出比較適合于執(zhí)行此模塊的器件,然后進(jìn)行運(yùn)算量估計(jì),根據(jù)運(yùn)算量估計(jì)結(jié)果考慮使用DSP的數(shù)量以及芯片間的數(shù)據(jù)調(diào)度方式。本平臺(tái)采用了如圖2所示的處理流程,發(fā)送端全部在FPGA內(nèi)部處理。接收端下變頻在FPGA內(nèi)處理,其它模塊全部由DSP處理,兩個(gè)DSP形成一個(gè)處理鏈關(guān)系,

圖2:直擴(kuò)系統(tǒng)處理流程圖

數(shù)據(jù)先進(jìn)入DSP A,然后由Linkport接口傳給DSP B,譯碼完畢后由DSP B經(jīng)過總線接口傳遞給CPLD,通信協(xié)議全部在DSP B內(nèi)部處理。DSPB作為整個(gè)平臺(tái)的處理核心,DSP A和FPGA均為其從屬器件。

3.1 發(fā)送端

因?yàn)榘l(fā)送端數(shù)據(jù)處理量較小,占用系統(tǒng)資源相比于接收處理基本可以忽略。依據(jù)圖1所示處理平臺(tái)結(jié)構(gòu),將原始數(shù)據(jù)直接發(fā)送給FPGA進(jìn)行調(diào)制和上變頻等處理即可[7]。

3.2 接收端

FPGA主要負(fù)責(zé)數(shù)字下變頻,因?yàn)檫@部分的運(yùn)算特點(diǎn)是處理量大,但是不需要繁瑣的調(diào)度。利用本地數(shù)控振蕩器(NCO)產(chǎn)生與輸入中頻信號(hào)頻率相同的正弦和余弦信號(hào),并與輸入信號(hào)相乘,然后對(duì)運(yùn)算結(jié)果做低通濾波,即可完成對(duì)中頻信號(hào)的下變頻操作。具體的參數(shù)由主控通過CPLD發(fā)送指令到FPGA中的控制寄存器來設(shè)定。FPGA中的寄存器又分為兩部分,一部分受CPLD控制,這樣主機(jī)可以通過CPLD發(fā)送命令來控制A/D的采樣率以及選擇數(shù)字濾波器的參數(shù)等,以適應(yīng)不同的通信標(biāo)準(zhǔn);另一部分受DSP控制,執(zhí)行數(shù)據(jù)調(diào)度操作。

DSP主要完成整個(gè)基帶數(shù)字信號(hào)處理,包括定時(shí)同步、糾正頻偏、信道估計(jì)、RAKE接收、數(shù)據(jù)檢測(cè)、解擴(kuò)、解交織、維特比譯碼等模塊。定時(shí)同步部分的特點(diǎn)時(shí)運(yùn)算量比較大,且需要一些跳轉(zhuǎn)等控制。因?yàn)榇薉SP有非常強(qiáng)大的FFT運(yùn)算能力,所以我們采用基于FFT快速相關(guān)的方法進(jìn)行同步。DSP內(nèi)部代碼采用C語言與匯編語言匯合編程的方式,利用兩種語言各自的優(yōu)勢(shì)進(jìn)行互補(bǔ)。

C語言開發(fā)速度很快,可讀性很強(qiáng),而且方便軟件的修改和移植,但是效率較低。匯編語言的效率很高,但是修改和移植能力較差,而且不便于調(diào)度。基于這個(gè)特點(diǎn),我們將程序全部模塊化,標(biāo)準(zhǔn)的算法模塊用匯編語言編寫,如FFT模塊等,整體的程序框架采用C語言,所以定時(shí)同步模塊采用DSP。另外,TigerSHARC201 DSP還支持一些專門用于直擴(kuò)系統(tǒng)的指令,如解擴(kuò)指令,Viterbi和Turbo譯碼專用指令等,所以將基帶處理部分放在DSP內(nèi)處理較為合理。

這樣處理的另外一個(gè)優(yōu)勢(shì)是使得系統(tǒng)兼容性更強(qiáng),在此系統(tǒng)中采用了不同的序列擴(kuò)頻比來抵抗信道衰落造成的影響,大范圍變化的擴(kuò)頻比會(huì)使系統(tǒng)整體調(diào)度發(fā)生很大變化。比如當(dāng)擴(kuò)頻比為16時(shí),所需的RAM較少,這樣片內(nèi)的DRAM就已經(jīng)夠用;而當(dāng)擴(kuò)頻比為10240時(shí),就必須要使用片外RAM,這樣就要用到總線接口,此時(shí)兩種系統(tǒng)的基帶處理模式完全發(fā)生了變化,從而導(dǎo)致系統(tǒng)整體調(diào)度發(fā)生變化。用C語言處理時(shí),可以設(shè)定幾個(gè)不同的工作模式,在處理循環(huán)開始的時(shí)候進(jìn)行切換即可。如果采用了不同的通信標(biāo)準(zhǔn)的話,處理就更為繁瑣一些。

平臺(tái)控制信息和狀態(tài)信息處理機(jī)制都采用查詢模式,即在執(zhí)行完一次循環(huán)后,DSP都會(huì)主動(dòng)去讀取主控發(fā)來的控制指令,隨后讀取FPGA的狀態(tài)信息,最后根據(jù)情況調(diào)整工作模式。

4. 結(jié)束語

本文作者創(chuàng)新點(diǎn)是提出一種使用新的高速串行接口設(shè)計(jì)通用軟件無線電平臺(tái)的方法。平臺(tái)以高性能DSP為數(shù)據(jù)處理核心,采用了一種新的高速串行接口進(jìn)行平臺(tái)數(shù)據(jù)調(diào)度。實(shí)踐證明,這種方法可以避免一些不必要的調(diào)度開銷和沖突,簡(jiǎn)化了系統(tǒng)設(shè)計(jì),縮短了開發(fā)周期。然后將其應(yīng)用于直接序列擴(kuò)頻系統(tǒng),用實(shí)際系統(tǒng)設(shè)計(jì)說明了這種方法的優(yōu)勢(shì)所在。

責(zé)任編輯:gt

-

dsp

+關(guān)注

關(guān)注

552文章

7962瀏覽量

348306 -

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602004 -

cpld

+關(guān)注

關(guān)注

32文章

1247瀏覽量

169226

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

中頻軟件無線電的實(shí)現(xiàn)方案和基于FPGA的通用硬件平臺(tái)

如何利用FPGA設(shè)計(jì)軟件無線電平臺(tái)?

分析一款不錯(cuò)的中頻軟件無線電系統(tǒng)的FPGA實(shí)現(xiàn)方案

怎么實(shí)現(xiàn)一款基于FPGA的軟件無線電平臺(tái)設(shè)計(jì)

如何去設(shè)計(jì)一種軟件無線電平臺(tái)系統(tǒng)?

基于FPGA的軟件無線電平臺(tái)設(shè)計(jì)方案解析

基于FPGA的通用軟件無線電平臺(tái)設(shè)計(jì)

基于FPGA的軟件無線電平臺(tái)設(shè)計(jì)詳細(xì)教程

軟件無線電硬件平臺(tái)的FPGA動(dòng)態(tài)配置

基于Xilinx Virtex6 FPGA的通用軟件無線電平臺(tái)設(shè)計(jì)

如何使用FPGA實(shí)現(xiàn)軟件無線電平臺(tái)的設(shè)計(jì)

基于TigerSHARC201和FPGA實(shí)現(xiàn)軟件無線電平臺(tái)的設(shè)計(jì)

基于TigerSHARC201和FPGA實(shí)現(xiàn)軟件無線電平臺(tái)的設(shè)計(jì)

評(píng)論