問題情景:為了得到連續時間內ADC采集的數據,并在PC上對數據進行分析,需要搭建鏈路實現FPGA到PC的數據傳輸。考慮到ADC采樣頻率較高(10M-100Mb/s),串口通信的速率遠遠達不到要求,考慮使用以太網來實現信息傳輸。

物理鏈路:14位ADC;開發板使用Xilinx Spartan-6 黑金開發板AX545;超五類或六類網線;由于程序只支持千兆以太網傳輸,并且考慮到部分筆記本不攜帶網口,因此使用了USB3.0-千兆網口的網卡;裝有wireshark的電腦。

FPGA部分:采用存儲轉發的思想,即先對ADC采集的數據進行緩存,等到采集的數據滿足一幀的數據長度,再對數據包封裝成幀發送,采用UDP格式進行發送。考慮到ADC時鐘與UDP時鐘不同步,因此先對ADC采集的數據進行一級緩存;由于以太網每次只能發送8位數據,而ADC采集的數據為14位,因此還需要對ADC緩存數據進行轉換,轉換得到的數據進行二級緩存;等到二級緩存達到發送數據的長度,使能UDP傳輸,加入幀頭后發送。

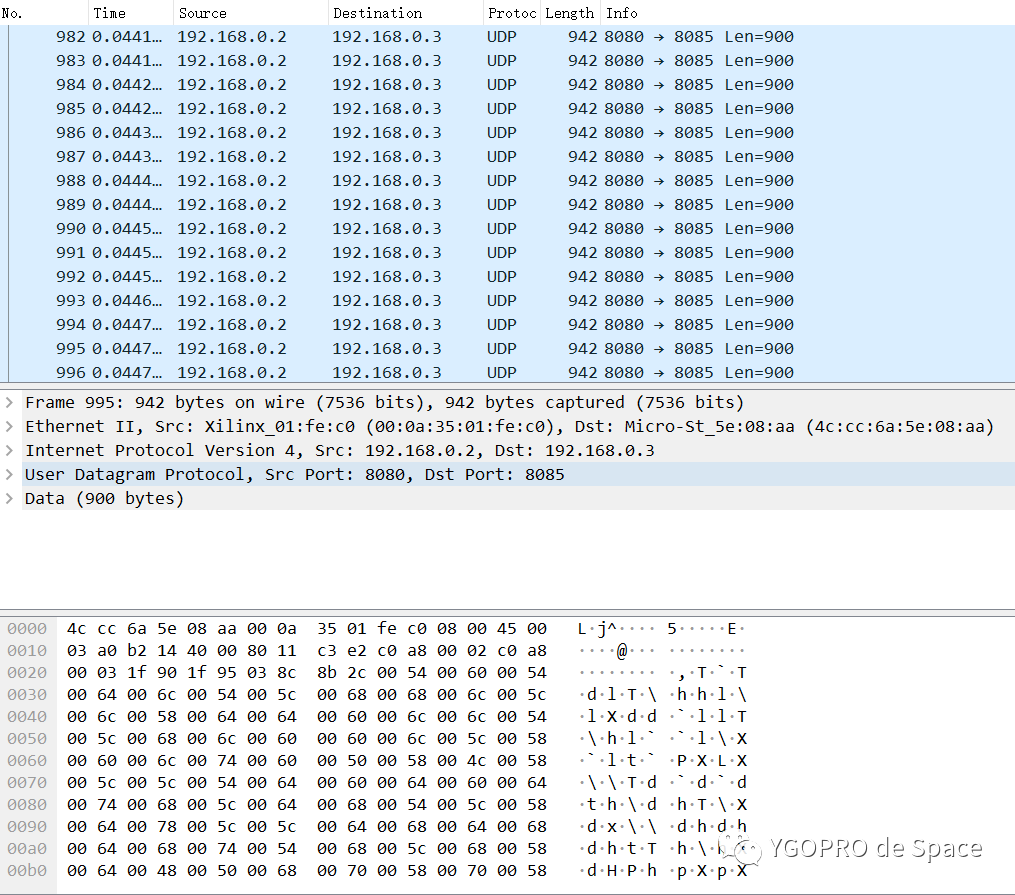

PC端接收:PC端數據接收采用wireshark實現,使用wireshark捕獲UDP包。由于傳輸速率過快,連續時間接收的UDP包過多,因此完成采集后先對采集的數據進行存儲,存為pcap格式為后續處理做準備。存儲的文件較大,達到百兆到G級別。

數據恢復(未找到很好的實現方法):數據保存在UDP包的數據幀部分,格式為十六進制或二進制,需要將數據部分和其他幀結構分離。方法一:利用網絡調試助手(上位機),在wireshark接收UDP包的同時打開上位機,就可以得到不含幀頭部的數據流,而且可以進行保存(此處使用的NetAssist),一個致命的問題是,當數據傳輸速率過快時,利用上位機保存下來的幀并不是連續的,會導致恢復的波形不連續。方法二:wireshark提供追蹤UDP流的功能,可以將所有幀中的數據流進行打印,但問題是得到的pcap文件中幀數據量過大,處理非常慢(嚴重影響使用)。方法三(考慮但未實現):利用MATLAB直接讀取pcap文件,下載pcap2matlab開源文件,利用這一文件解析pcap文件;利用python dpkt包解析pcap文件。如果有合適的解決方法,歡迎交流!

原文標題:FPGA-PC以太網通信

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1626文章

21670瀏覽量

601882 -

以太網

+關注

關注

40文章

5378瀏覽量

171126

原文標題:FPGA-PC以太網通信

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

網絡數據傳輸速率的單位是什么

以太網端口的類型和特性

以太網接口的數據傳輸原理詳解

TIDA-010076-通過單對以太網 (T1) 實現菊花鏈式電源和數據傳輸的PCB layout 設計

光傳送網(OTN)助力實現超高速、高帶寬數據傳輸

手機沒有OTG功能,如何實現數據傳輸?

虹科方案 | 如何破解CAN與車載以太網之間數據傳輸和協議轉換的難題?

搭建鏈路實現FPGA到PC的數據傳輸使用以太網實現信息傳輸

搭建鏈路實現FPGA到PC的數據傳輸使用以太網實現信息傳輸

評論