1 概 述

擴(kuò)展頻譜通信具有抗干擾能力強(qiáng)、隱蔽性好等優(yōu)點(diǎn),已成為通信對(duì)抗與反對(duì)抗中最重要的技術(shù)手段,在軍事通信中日益受到重視,跳頻電臺(tái)就是擴(kuò)頻通信在軍事領(lǐng)域中的重要應(yīng)用。在通信對(duì)抗中如何有效地對(duì)抗跳頻電臺(tái)是目前的一個(gè)熱點(diǎn)問(wèn)題。在通信對(duì)抗的教學(xué)中為了以實(shí)驗(yàn)的形式向人們展示跳頻通信中干擾與抗干擾的原理,并能對(duì)跳頻通信進(jìn)行偵察和實(shí)施多種干擾的效果進(jìn)行比較,為科研中尋找對(duì)跳頻通信的最有效干擾方式提供有效的數(shù)據(jù)和參考,本文給出了一種基于DDS與USB技術(shù)的通信對(duì)抗教學(xué)演示系統(tǒng)中硬件方案的設(shè)計(jì)與實(shí)現(xiàn)。

2 系統(tǒng)整體結(jié)構(gòu)設(shè)計(jì)及原理說(shuō)明

系統(tǒng)主要由控制計(jì)算機(jī)、發(fā)射機(jī)、電子偵察模塊、電子干擾模塊和接收機(jī)等五部分組成,如圖1所示。計(jì)算機(jī)主要是用于控制與協(xié)調(diào)各個(gè)模塊的工作和數(shù)據(jù)傳輸,決定系統(tǒng)各部分的工作模式并對(duì)工作狀態(tài)進(jìn)行實(shí)時(shí)監(jiān)視。

發(fā)射機(jī)在計(jì)算機(jī)指令的控制下,在指定的工作頻段內(nèi)以相應(yīng)的方式發(fā)射跳頻信號(hào)。電子偵察模塊利用高速A/D采樣技術(shù)與高速FFT實(shí)時(shí)處理技術(shù)可以快速地捕捉并計(jì)算出發(fā)射信號(hào)的工作頻率點(diǎn),同時(shí)將偵察到的跳頻數(shù)據(jù)送至電子干擾模塊。接收到偵察數(shù)據(jù)的干擾模塊在計(jì)算機(jī)控制下利用FPGA控制頻率合成器件產(chǎn)生各種調(diào)制信號(hào),選擇不同的干擾方式對(duì)通信電臺(tái)實(shí)時(shí)有效的干擾。干擾信號(hào)與實(shí)際跳頻信號(hào)分別送人合路器中,由合路器送至接收機(jī)比較各種不同干擾方式的實(shí)際效果。

3 器件的選擇

3.1 A/D芯片與FPGA芯片

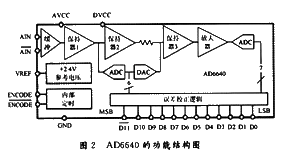

A/D芯片選用的是為寬帶和多信道數(shù)字無(wú)線接收機(jī)系統(tǒng)而推出的12位中頻快速采樣芯片AD6640。

AD6640是一個(gè)高速度、高性能、低功耗,單片式12位AD轉(zhuǎn)換器,內(nèi)含采樣保持電路和基準(zhǔn)源。他由單電源+5 V供電,TTL/CMOS兼容電平輸出,中頻采樣頻率的典型值為70 MHz(多信道時(shí))和200 MHz(單信道時(shí)),采樣速率可達(dá)65 Mb/s,信噪比SNR的典型值為68 dB,SFDR值為80 dB,功耗為710 mW。AD6640采用兩級(jí)子區(qū)式的轉(zhuǎn)換結(jié)構(gòu),既保證了精度又降低了功耗,其功能模塊如圖2所示。從圖2可以看出ADC所有需要的功能,包括輸入緩沖,跟蹤保持放大,數(shù)字糾錯(cuò)以及2.4 V參考電壓都由芯片提供,從而使其設(shè)計(jì)變得更輕松。

FPGA芯片采用的是Altera公司的ACEXlK系列產(chǎn)品的EPlKl00芯片。其特點(diǎn)是將查找表(LUT)和EAB相結(jié)合,提供了高效率而又廉價(jià)的結(jié)構(gòu)。基于LUT的邏輯對(duì)數(shù)據(jù)路徑管理、寄存器強(qiáng)度、數(shù)學(xué)計(jì)算或數(shù)字信號(hào)處理(DSP)的設(shè)計(jì)提供優(yōu)化的性能和效率,而EAB可實(shí)現(xiàn)RAM,ROM,雙口RAM或FIFO功能。這使得ADEXlK適合于復(fù)雜邏輯及存儲(chǔ)器功能,如數(shù)字信號(hào)處理、寬域數(shù)據(jù)路徑管理、數(shù)據(jù)變換和微處理器等各種高性能通信應(yīng)用。基于可重構(gòu)CMOS SRAM單元,ACEX1K結(jié)構(gòu)具有實(shí)現(xiàn)一般門陣列宏功能需要的所有特征,相應(yīng)的多引腳數(shù)提供與系統(tǒng)元器件的有效接口。先進(jìn)的處理功能和2.5 V低電壓要求,使得AC2EX1K器件滿足廉價(jià)、高容量的應(yīng)用需要。

3.2 DDS芯片

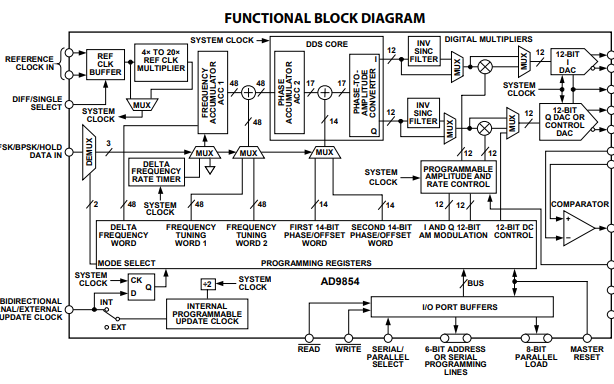

DDS芯片選用的是美國(guó)的Analog Device Inc(ADI)公司生產(chǎn)的DDS器件AD9854。AD9854數(shù)字頻率合成器是一個(gè)采用了先進(jìn)的DDS技術(shù)的高集成器件。

他具有一對(duì)內(nèi)部高速、高性能的正交D/A轉(zhuǎn)換器和比較器,可實(shí)現(xiàn)數(shù)字合成正交的I和Q路輸出。當(dāng)輸入一準(zhǔn)確的參考頻率,AD9854即可產(chǎn)生一高穩(wěn)定的頻率、相位、幅度可編程的正弦和余弦信號(hào)。AD9854的DDS核心具有48 b的頻率分辨率。14 b相位截?cái)啾WC了優(yōu)良的SFDR指標(biāo)。AD9854的電路工藝使同步正交信號(hào)輸出的頻率最高達(dá)到150 MHz,平均每秒產(chǎn)生1百萬(wàn)新頻率。AD9854中4~20整數(shù)倍的可編程參考頻率累加器能使外部輸入的低速時(shí)鐘轉(zhuǎn)變成內(nèi)部高速時(shí)鐘(最高300 MHz)。

AD9854能實(shí)現(xiàn)除了基本的FSK以外的增強(qiáng)頻譜特性的Ramped FSK。該器件采用了先進(jìn)的35μmC2MOS技術(shù)使該器件只需要+3.3 V的電源供應(yīng)。

系統(tǒng)所用的DAC為ADI公司的AD5344,他是一種低功耗12 b數(shù)模轉(zhuǎn)換器。該芯片可應(yīng)用于便攜式電池電源儀器、可編程電壓和電流源、可編程衰減器、工業(yè)處理控制器以及數(shù)字放大和補(bǔ)償調(diào)節(jié)等方面。圖3為其內(nèi)部結(jié)構(gòu)原理圖。AD5344有4路12 b DAC,可在2.5~5.5 V之間正常工作,在外接+3 V電壓時(shí)典型電流值為500μA,并且具備進(jìn)一步將電流降至80 nA的節(jié)電模式。他的輸出緩存可將輸出驅(qū)動(dòng)到兩個(gè)電源軌道之上。通過(guò)A0和A1可控制選擇哪一路輸出。

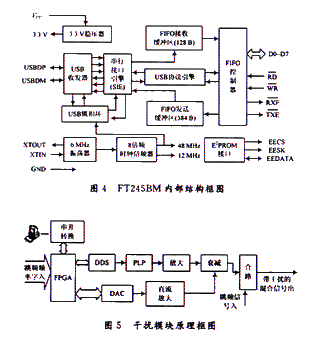

在控制模塊中LISB芯片選用的是FTDI公司的FT245BM。該芯片是FTDI公司早期生產(chǎn)的一種較通用的支持USB 1.1標(biāo)準(zhǔn)的專用芯片,其優(yōu)點(diǎn)在于芯片通用性好,無(wú)需固件配置,控制時(shí)序簡(jiǎn)單,而且廠家提供了完備的各類庫(kù)函數(shù)供編程使用,極大地縮短了開(kāi)發(fā)周期。

FT245BM內(nèi)部結(jié)構(gòu)框圖如圖4所示,F(xiàn)T245BM內(nèi)部主要由USB收發(fā)器、串行接口引擎(SIE)、USB協(xié)議引擎和先進(jìn)先出(FIFO)控制器等構(gòu)成。他的一個(gè)比較明顯的優(yōu)點(diǎn)就是,內(nèi)部集成的模塊功能完備,不需要在使用時(shí)重新對(duì)其進(jìn)行配置。在接收到主機(jī)發(fā)出的控制命令后,USB收發(fā)器自動(dòng)執(zhí)行命令,并通過(guò)串行接口引擎完成USB數(shù)據(jù)的串/并雙向轉(zhuǎn)換。USB協(xié)議引擎按照USB 1.1的規(guī)范來(lái)完成對(duì)FIFO控制器的管理,F(xiàn)IFO控制器通過(guò)其兩個(gè)握手信號(hào)的輸出端口RXF#和TXE#來(lái)引導(dǎo)外部主控制器對(duì)USB芯片的讀寫控制。

4 系統(tǒng)的設(shè)計(jì)實(shí)現(xiàn)

4.1 干擾模塊的設(shè)計(jì)

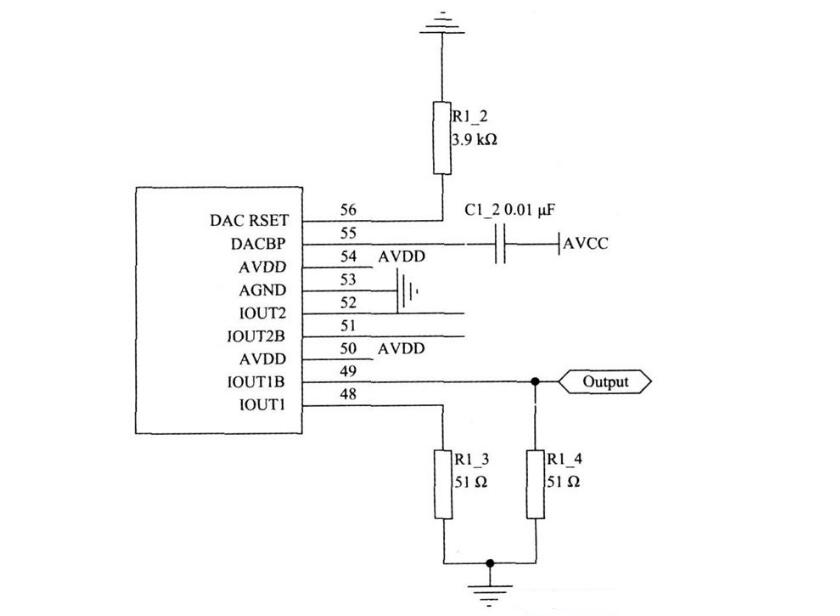

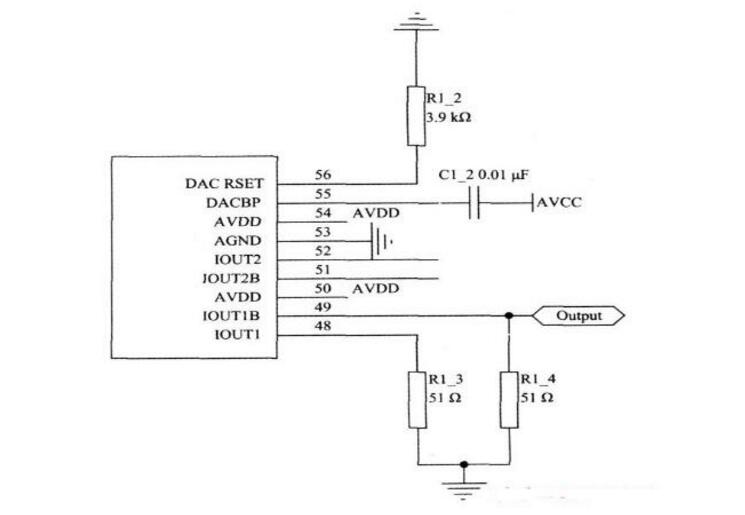

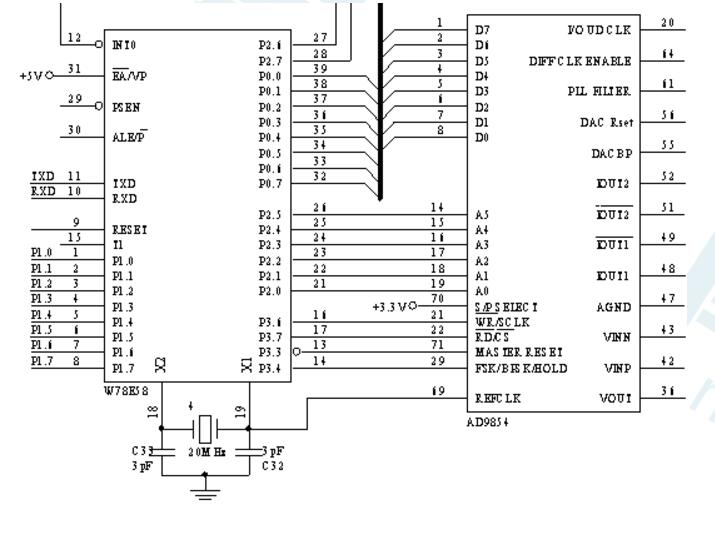

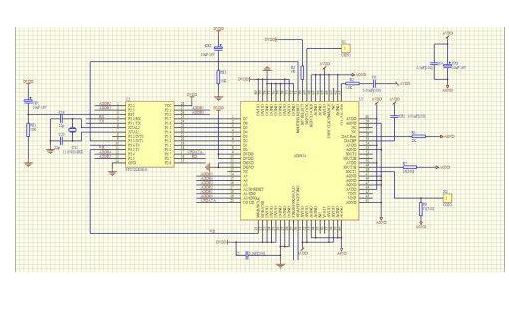

干擾模塊原理圖如圖5所示。在干擾模塊的設(shè)計(jì)中,選用了常用的DDS芯片AD9854與FPGA相結(jié)合的方式來(lái)產(chǎn)生干擾頻率。為了實(shí)現(xiàn)干擾信號(hào)功率的可控制,擬在DDS輸出的信號(hào)加上衰減器。采用計(jì)算機(jī)通過(guò)USB芯片來(lái)控制干擾模式的選擇和干擾信號(hào)參數(shù)的選擇。DDS產(chǎn)生的信號(hào)先通過(guò)低通濾波再放大,目的是為抑制雜散信號(hào)。

在跟蹤式干擾中,F(xiàn)PGA接收電子偵察所獲得的通信信號(hào),引導(dǎo)DDS產(chǎn)生同頻的干擾信號(hào)。在非跟蹤式干擾中,由計(jì)算機(jī)控制產(chǎn)生單頻干擾、掃頻干擾以及隨機(jī)調(diào)頻噪聲等樣式的干擾信號(hào),這些干擾信號(hào)和原跳頻信號(hào)在合路器合路輸出,送給跳頻接收機(jī),以此來(lái)檢驗(yàn)跳頻通信對(duì)這些干擾樣式的抗干擾能力。

4.2 控制模塊的設(shè)計(jì)

在系統(tǒng)的整體設(shè)計(jì)過(guò)程中,非常重要的部分就是對(duì)于整個(gè)實(shí)驗(yàn)系統(tǒng)的控制。系統(tǒng)的整體控制模塊原理框圖如圖6所示。

從圖中可以看出,干擾模塊中的FPGA芯片,在系統(tǒng)控制中起著核心作用。在該模塊中,F(xiàn)PGA主要完成4個(gè)方面的任務(wù):

(1)實(shí)現(xiàn)與電子偵察模塊的實(shí)時(shí)通信,不斷地接收偵察模塊送來(lái)的跳頻信號(hào)信息,并立即做出相應(yīng)的反應(yīng)。

(2)實(shí)現(xiàn)與計(jì)算機(jī)主機(jī)的通信,控制USB芯片的讀寫程序,隨時(shí)接收主機(jī)發(fā)出的控制指令,并完成相應(yīng)的功能。

(3)實(shí)現(xiàn)對(duì)DDS芯片的控制,根據(jù)需要選擇DDS不同的工作模式。

(4)實(shí)現(xiàn)對(duì)衰減器的控制,根據(jù)主機(jī)的命令選擇不同的頻率幅度。

5 結(jié) 語(yǔ)

通過(guò)對(duì)實(shí)際硬件電路的分析與調(diào)試,系統(tǒng)實(shí)現(xiàn)了計(jì)算機(jī)對(duì)USB芯片的控制、FPGA對(duì)DDS芯片的控制、偵察模塊與干擾模塊的互連通信以及各類干擾方式的可控實(shí)現(xiàn)。在進(jìn)行實(shí)際試驗(yàn)時(shí),通過(guò)對(duì)不同干擾方式的效果進(jìn)行比較,還可以選擇出對(duì)跳頻電臺(tái)通信最有效的干擾方式,并且對(duì)今后研究實(shí)戰(zhàn)形式的跳頻偵察干擾系統(tǒng)具有一定的實(shí)際參考意義。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601806 -

芯片

+關(guān)注

關(guān)注

453文章

50387瀏覽量

421783 -

頻率合成器

+關(guān)注

關(guān)注

5文章

218瀏覽量

32331

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

低相噪毫米波頻率合成器設(shè)計(jì)

詳解頻率合成器高性能架構(gòu)的實(shí)現(xiàn)

如何利用FPGA設(shè)計(jì)PLL頻率合成器?

什么是頻率合成器

頻率合成器,頻率合成器原理及作用是什么?

集成鎖相環(huán)頻率合成器,什么是集成鎖相環(huán)頻率合成器

AD9854驅(qū)動(dòng)程序設(shè)計(jì)

ad9854調(diào)試使用心得

基于AD9854的信號(hào)發(fā)生器設(shè)計(jì)

基于AD9854產(chǎn)生MSK調(diào)制信號(hào)詳細(xì)說(shuō)明

ad9854應(yīng)用電路圖大全(五款ad9854信號(hào)發(fā)生/頻率發(fā)生器/正交信號(hào)源電路)

stm32驅(qū)動(dòng)ad9854程序分享_ad9854構(gòu)成信號(hào)發(fā)生器電路

AD9854數(shù)字合成器的詳細(xì)英文數(shù)據(jù)手冊(cè)免費(fèi)下載

AD9854直接數(shù)字頻率合成器的掃頻程序和工程文件免費(fèi)下載

基于EPlKl00芯片和AD9854頻率合成器實(shí)現(xiàn)通信對(duì)抗教學(xué)演示系統(tǒng)的設(shè)計(jì)

基于EPlKl00芯片和AD9854頻率合成器實(shí)現(xiàn)通信對(duì)抗教學(xué)演示系統(tǒng)的設(shè)計(jì)

評(píng)論