假如顯示終端為數字微鏡DMD(Digital MicromirrorDevice)顯示器。該顯示器將計算機每個像素點的圖像信號經過數字光處理DLP(Digital Light Processing)后,存入SDRAM雙向緩存器,當一幀圖像接收完畢時,內部數據處理電路同時激發各像素點對應的微鏡運動,完成一幀圖像的顯示。DMD顯示器峰值數字驅動電壓不超過33.5V,電磁輻射很低,且各微鏡片同時驅動,形成相互干擾的向外輻射信號,解碼難度極大,從而使其成為無信息泄漏的顯示器。此時,視頻電纜的輻射在整個視頻通路的輻射中就占主導地位。如果在視頻信號經過視頻電纜傳輸到顯示器之前就對其進行處理,則可以有效地降低電磁輻射和信息泄漏。

1 視頻信息泄漏機理及解決方案

1.1 視頻信息傳輸過程中泄漏機理

在計算機視頻通路中,信息的傳送主要為并行傳送和串行傳送兩種方式。目前常見的視頻信息都為串行傳輸,在串行傳輸的信號波長與其視頻電纜物理長度可比的情況下,視頻電纜起著天線作用,容易產生高強度的有用信息的電磁泄漏,這樣就可以較為容易地對串行信號實現時分接收、頻分接收和方位接收。所以串行視頻信息很容易被竊取及復現。

在并行傳輸方式下,由于數據線間隔很小且發射信號頻率相同或相似,所以截獲難度要大得多。但將R、G、B三路串行模擬視頻信號分別轉化為數字信號后,若不經處理就直接進行傳輸,此時同時傳輸的仍是一個像素的不同位信息,因此,從像素角度來考慮,仍為串行傳輸。若傳輸的圖像僅有黑白兩種顏色,則此時并行傳輸電纜上某一時刻的數據為全“1”或全“0”,即并行電纜中各信號線具有相同的波形,也就不需對各信號線分別接收,此時視頻電纜類似于串行傳輸方式,有效信息就很容易被竊取。

1.2 基于像素的并行傳輸方式

為了有效地減少視頻信號被截獲的可能性,在視頻信號送至視頻電纜中傳輸之前就對其進行一定的格式轉換,使得在并行電纜上能同時傳輸多個像素,實現真正意義上的并行,即基于像素的并行傳輸。在這種并行傳輸方式下,即使接收方能接收到輻射信息,由于無法分辨各像素的順序,也就不能復現信息。

本文設計的防信息泄漏系統就是通過對視頻信號的格式轉換處理,實現多個像素的同時傳輸。圖1為視頻信息格式轉換原理示意圖,輸入數據為串行模擬視頻信號經過A/D轉換后得到的數字視頻信號,系統接收信息時,其順序是按單個像素依次接收的,此時數據為“像素包”格式。通過格式轉換模塊處理之后,這些以“像素包”格式接收到的視頻信號數據被轉換成為按照“位平面”格式排列的輸出數據。此時并行電纜上傳輸的就是多個像素的數據。“位平面”格式的視頻數據傳輸至顯示端后再通過格式轉換模塊還原為“像素包”格式。

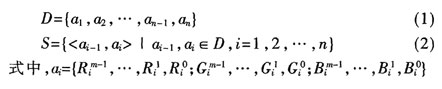

順序接收到的“像素包”格式的數據可以用以下的集合方式予以描述:若系統接收到n個像素,則用D表示接收到的這一組視頻信號,S表示D中各元素間的先后順序關系,信號色彩數為23m種,即R、G、B三種顏色分別具有2m級灰度,則:

同樣,轉換為“位平面”格式后的輸出數據亦可以用同樣的集合方式進行描述:E表示格式轉換后的一幀圖像的數據,F表示E中各元素間的先后順序關系,則:

將視頻信息由集合D所表述的形式轉換成由集合E所表述的形式,就是傳輸數據格式轉換所要完成的工作,即要求首先輸出所有像素的第一位二進制數據,然后輸出所有像素的第二位二進制數據,直到最后輸出每個像素的最后一位二進制數據。因此,“位平面”數據是n個像素點的三種顏色的、具有相同“權值”的數據的集合。

2 系統硬件設計

2.1 總體方案設計

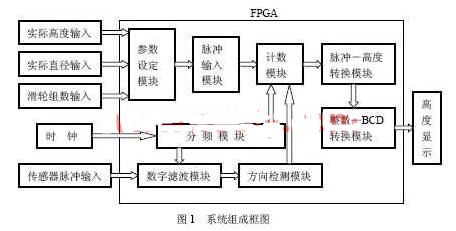

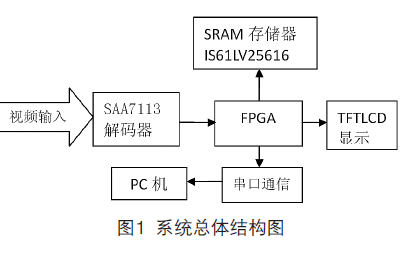

根據上面提出的像素并行傳輸的原理,設計基于FPGA的防視頻信息泄漏系統。圖2為該系統硬件設計框圖,整個系統由采集端適配卡和顯示端適配卡組成。

高速視頻專用A/D轉換器采用AD公司的高性能AD9883A,主要特點是:

(1)高達300MHz的帶寬和140MSPS的轉換率。

(2)三路獨立的0~1.0V的輸入信號范圍,非常適合采樣視頻信號。

(3)提供I2C總線接口等,以適應多種應用。

高速視頻專用D/A轉換器采用AD公司的高性能ADV7125,主要特點是:

(1)高達330M的吞吐量。

(2)三路獨立的8位DA轉換器。

(3)TTL兼容輸入信號,便于電路設計。

(4)單電源5V或3.3V供電,廣泛應用于數字視頻系統、高分辨率彩色圖像顯示系統。

系統工作原理是:將來自顯卡的視頻信號輸入至采集端適配卡,采集端適配卡上的A/D轉換器將R、G、B三路模擬視頻信號分別轉換成三路并行8位數字信號,同時也對行、場同步進行相位修復和幅度補償,使之變為標準的行、場同步信號,然后將該信號送至FPGA中,同時在狀態機的控制下將以像素為單位的視頻信息轉換為“位平面”格式。信號處理完后通過并行傳輸電纜傳輸至顯示端適配卡,而顯示端適配卡則負責將“位平面”信息還原為像素格式,并通過D/A轉換器將三路共24bit數字視頻信號還原成模擬信號送給顯示設備進行顯示。

2.2 電磁兼容設計

2.2.1 信號完整性設計

系統中數字視頻信號對傳輸時延要求較高,在布線時,其走線的路徑要大體一致并且盡量短,以實現對傳輸時延的要求;合理安排去耦電容的擺放位置,盡可能接近所要進行去耦的電源;AD9883A芯片和ADV7125芯片周圍電路的布線要盡可能短,周圍的元器件要盡可能安排緊湊,以減小電流環路面積,從而減小靜電干擾;放置過孔時,注意不要過密,以免損壞鏡像層;適配卡所用的電阻、電容、電感和IC芯片均為表面帖裝元件,有利于抑制電磁干擾。

2.2.2 電源完整性設計

系統所用的A/D轉換器芯片、D/A轉換器芯片對電源有嚴格的要求,除了要有模擬電源和數字電源之分外,AD9883A還要有PLL電路的專門電源,而FPGA電源要有內核電源和數字輸出引腳的電源。因此,整個系統的電源設計是一個很大問題。這里用兩片LT1764作為FPGA的兩種電源,用兩片TPS76333作為AD9883A的兩種電源,一片TPS76333作為ADV7125的電源。兩塊適配卡均 采用四層板結構,頂層和底層作為信號的走線層,中間層分別是地層和電源層,以確保系統在高速運行時有良好的電源環境。

3系統邏輯實現及仿真

FPGA芯片采用Altera公司Cyclone系列芯片EP1C6Q240C8。Cyclone系列芯片是基于1.5V,0.13μm工藝,具有時鐘鎖相環(PLL)和專用DDR接口,支持多種I/O標準的芯片。其內部嵌入了許多專用硬核模塊,被廣泛地用于可編程片上系統(SOPC)中。

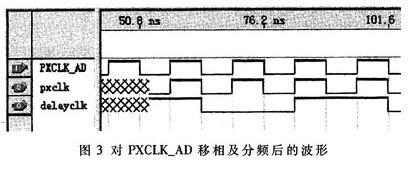

本系統對高速圖像信號進行處理,工作時鐘近100MHz。為了獲得更好的布線效果和系統性能,時鐘信號必須經過鎖相環到達全局時鐘布線網絡。本設計利用Altera公司的Maga Wizard設置Cyc lone PLL參數生成IPcore,解決了信號時延的問題,同時也滿足了讀取視頻信號時所需的建立、保持時間要求。圖3為使用FPGA內部PLL對輸入的點頻時鐘PXCLK_AD進行相移后的波形,圖中,pxclk與點頻同頻,經相位修復及幅度補償后用作系統基準時鐘,delayclk為點頻三分頻,用作延時時鐘。

3.1 視頻信息格式轉換模塊

在采集端適配卡中,視頻信息由“像素包”格式轉換為“位平面”格式,可由一個n×m矩陣轉換電路完成,其輸入數據總線寬度為m位,輸出數據總線寬度為n位。系統工作時,每次要連續進行n次輸入,即讀入n個像素的數據,再連續進行m次輸出,即把這些數據寫到m個位平面所對應的各自的存儲位置。格式轉換電路原理如圖4所示,采用一個n×m的D觸發器陣列,再加上相應的輸入和輸出鎖存電路及狀態機控制電路,即可實現nxm數據格式轉換。

當第i個像素輸入時,輸入數據狀態機觸發第i行D觸發器,第i個像素的第j位灰度信息就被存儲在第i行的第m-1-j個D觸發器中(i=1,2,…,n,j=0,1,…,m-1),n個像素全部輸入完畢后,n×m位二進制信息就全部存儲在n×m個D觸發器中。此時,第i行D觸發器中存儲的是第i個像素的m位灰度信息,即“像素包”格式信息,第j列D觸發器中存儲的是n個像素的第m-1-j位灰度信息,即“位平面”格式信息。輸出數據狀態機按一定順序輸出某一列D觸發器中數據,即可實現“位平面”數據的輸出。視頻信息由“位平面”格式轉換為“像素包”格式原理與上述矩陣電路相似,限于篇幅在此不再介紹。

在分辨率為1024×768、刷新率為75Hz的情況下,點頻為78.75MHz,由于數據傳輸的速度與傳輸位數成反比,若n

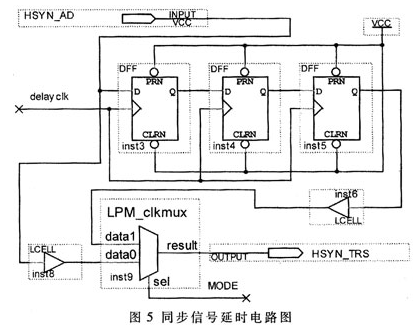

3.2 同步信號延時模塊

同步信號是一定頻率的脈沖串,與視頻信號存在嚴格的同步關系,其頻率與顯卡設定的顯示分辨率和屏幕刷新率有關。在進行視頻信息格式轉換過程中,視頻信息共延時了約九個點頻周期。為了使視頻信息進入顯示設備時與行、場同步信號間的相互時序關系仍能夠保持完好,行、場同步信號均需通過延時模塊進行處理。圖5為采集端適配卡中行同步信號延時電路圖。本系統由兩塊適配卡組成,兩塊適配卡中行、場信號延時電路相似。

3.3 系統頂層模塊

整個防視頻信息泄漏系統設計完成后,其頂層模塊如圖6和圖7所示。圖中,SCI、SDA用來初始化AD9883A芯片,DATA_RDY為自定義的視頻信息轉換完畢信號。

兩塊適配卡中都有格式轉換電路,視頻信息經過了兩次格式轉換后,最終還原為初始的“像素包”格式數據。取輸入點頻PXCLK_AD為78.75MHz,運用Quartus II進行綜合及時序仿真后,兩個頂層模塊綜合仿真的結果如圖8所示,圖中,三組數據依次為“像素包”格式、“位平面”格式、“像素包”格式。

從圖8中可以看出視頻信息經過兩次轉換后被還原成原始數據,行、場信號也相應有了一定的延時,且與視頻信息保持了良好的同步性,這說明基于像素的并行傳輸方式是可行的。

在采用DMD顯示器作為終端顯示設備的前提下,以現場可編程門陣列(FPGA)為基礎、以基于像素的并行傳輸方式為核心的計算機防視頻信息泄漏系統能實現多個像素的同時傳輸,接收方極難從接收到的輻射信息中分辨出各像素的顯示順序,也就不能復現信息,從而有效地防止了視頻信息被截獲,增強了信安全性。

責任編輯:gt

-

FPGA

+關注

關注

1626文章

21667瀏覽量

601850 -

顯示器

+關注

關注

21文章

4948瀏覽量

139823 -

計算機

+關注

關注

19文章

7421瀏覽量

87718

發布評論請先 登錄

相關推薦

基于EP1C6Q240C8的FPGA芯片實現電子測試系統的設計

FPGA EP1C6Q240C8 外圍電路圖阿

基于PCI 總線的高速數據采集系統的設計與實現

求助:FPGA ep1c6q240c8如何連接外部雙口RAM?

有誰用過EP1C6Q240C8N這個型號的芯片嗎?

計算機信息泄漏

基于USB的CAN適配卡的設計與實現

計算機視頻信息泄漏中的紅信號鑒別研究

基于數字濾波的計算機視頻信息防泄漏研究

EP1C6Q240C8實現LCD滾屏

如何使用EP1C6T144C8設計進行FPGA的視頻圖像處理系統詳細資料概述

基于EP1C6Q240C8芯片和適配卡實現計算機防視頻信息泄漏系統的方案

基于EP1C6Q240C8芯片和適配卡實現計算機防視頻信息泄漏系統的方案

評論