如果說上期SkrSkr隊伍的設計像是德智體美勞全面發展的“五好學生”,那么冠軍隊伍的設計則更像是“不偏科的特長生”。

作品跳出前兩屆Top3隊伍的設計思路,充分結合FPGA數據流架構的優勢,逐步優化設計,最終在幀率上達到212fps,首次參賽一舉奪魁。

作品全HLS設計,采用PYNQ框架,其提高幀率的優化流程在其他HLS設計中亦值得借鑒。

01

從2018年設立DAC-SDC開始,每年都會吸引全球百支知名研究團隊參與角逐,與計算機視覺類的國際知名目標檢測比賽不同,DAC-SDC對高精度、高效率的追求不僅僅停留在算法層面,其更注重考察基于軟硬件協同的系統構建能力,即參賽設計不僅要提高復雜場景中小物體精準檢測的能力,還需要考慮整個硬件系統在圖像處理速度和功耗方面的要求。而且隨著技術迭代速度的加快,該賽項的平臺和要求也在不斷改進。2018、2019年該賽項由Nvidia、Xilinx 和 DJI 大疆創新贊助,賽項分為GPU和FPGA兩個方向。2020年只保留了FPGA方向。從選用平臺的角度來對比,2018年以Zynq7020作為目標平臺;2019年選用邏輯資源較多的ZU3作為目標平臺,邏輯資源的增加提升了大賽的可發揮空間。2020年仍延用19年的目標平臺Ultra96。關于賽事詳情請參考 快訊|中國團隊包攬頂會DAC-SDC競賽冠亞軍

2018年比賽情況

TX2 GPU和Zynq7020 的對比結果顯示,在同等精度條件下FPGA的處理速度較低,但FPGA平臺所需的功耗僅為GPU平臺的不到1/4。在2018年的設計中,Top3均采用了“自頂向下”的DNN設計思路(沿用目標檢測常規算法),而后再考慮算法在硬件層面的優化。其中FPGA組的冠軍來自清華大學汪玉教授團隊,其采用了深鑒科技的硬件加速器架構 DPU、全棧式工具鏈 DNNDK 和深度壓縮技術的基礎上,從算法、軟件和硬件對整個目標檢測系統進行了全棧式的協同優化。通過采用硬件友好的 SSD 網絡和多線程優化技術,結合深度壓縮和定點訓練,在保證識別精度的前提下,滿足了低功耗和實時性的要求。

2019年比賽情況

FPGA組升級到邏輯資源較多的ZU3(Ultra96)平臺。與2018年相比,在精度和速度方面的表現均有一定的提升。特別值得一提的是,2019年 GPU和FPGA的冠軍來自同一團隊,其由UIUC Deming Chen教授課題組聯合了 IBM、Inspirit IoT和新加坡 ADSC 的研究人員組成。該網絡架構采用“自底向上”的DNN設計思路,以硬件資源限制為約束進行網絡結構搜索得到架構的優化設計,而后將其部署在目標平臺上。因此,冠軍團隊的工作實質上是同一網絡架構(SkyNet)在不同平臺的優化設計實現。

縱觀前兩年的工作,2018年解決的問題主要集中在限定資源條件下如何部署DNN模型;2019年冠軍組的工作則體現了限定資源條件下如何搜索最優模型架構。上述工作更多考慮的是算法的本身和資源的約束,而沒有充分發揮FPGA平臺自身優勢。

02

我們的工作

基本設計思路

我們團隊主要從FPGA的架構特點入手對任務處理進行優化設計。FPGA的優勢在于其靈活、高效地并行化設計架構,適于處理流式、計算密集型任務,適于不同字節寬度的調節等。針對本賽項待處理的目標檢測任務特點,我們選用了卷積神經網絡算法,其中包含多層結構,需要依次計算各層,且計算密集。結合待處理任務的特點,為了充分發揮FPGA的優勢,我們提出了以下設計思路:

l 算法設計優化:壓縮神經網絡的參數量,且采用低bit量化技術,使得參數量較少且每個參數所需要的儲存空間減少,從而使所有的參數能夠置于FPGA片內BRAM中,減少加速過程中參數頻繁調入/出帶來的開銷。

l 硬件設計優化:基于FPGA資源構建高效流水結構,將卷積神經網絡中的所有層都置于片上,使得所有層能夠以流水線的形式并行進行計算;設計高效的低bit的矩陣計算單元,在有限資源的約束下最大化并行度。

基于上述設計構想,數據輸入加速器能直接輸出計算結果,中間結果不必搬運到外部RAM,減少了不必要的時延和能耗。低bit計算減少了單個計算單元的資源開銷,從而提高了整體并行度,進而提高了整個神經網絡計算的速率。

設計方案

1、目標檢測算法的設計

基于上述基本設計思想,我們自行構建了適于Ultra96平臺資源限定條件的網絡模型。其中主干網絡選用類VGG架構,為了降低所需的參數量和計算量,我們嚴格控制了各層濾波器的數量,后端采用類yolo 架構設計,整個網絡模型如下圖2所示。與2019年的第一名相比,我們的算法雖然精度略低,但計算量和參數量都有大幅度地降低。

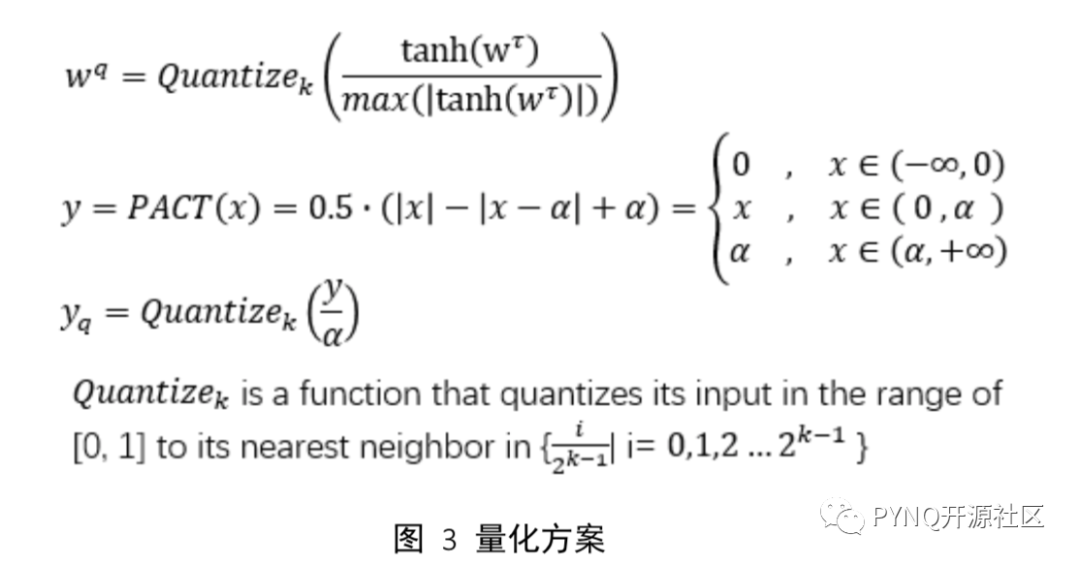

2、網絡量化設計

量化技術是整個解決方案中重要的一個環節。我們量化了整個神經網絡,包括權值量化,激活量化等。量化方法如下:

我們對所有的權值(W)和激活后的數據進行了歸一化處理,使得所有的數據在尺度上是統一的。而后將權值和特征圖數據都量化到了4bit,雖然算法精度上有所降低,平均IoU從0.701降低了到0.649,但所需參數的儲存空間降為原來的八分之一。我們只需要花費0.105 MB片上空間就能將所有參數置于片上,而Ultra 96 v2板上FPGA芯片中共有0.95 MB BRAM空間。

3、 自定義數據流的AI加速器設計

根據待處理任務特點,我們基于目標平臺(Ultra96)資源特點,設計和實現一套“硬件函數庫”,將pytorch中的CNN算法映射到FPGA中(如下圖5)。其中,我們將pytorch中的卷積計算(Conv2d_Q)拆分成兩個部分——滑動窗口單元(SWU)和矩陣向量乘單元(MVU),SWU負責將卷積計算展開為矩陣向量計算,MVU則負責接收SWU輸出的數據流并計算。為減少片上存儲空間(緩存)使用量,我們將原CNN算法中的批正則化層(BatchNorm2d)與激活量化層(ReLu_Q)合為一個模塊Bn_Relu進行處理。為了便于構建流水處理架構,原pytorch中采用的四個層(卷積層、批正則化層、激活量化層和池化層)就變為我們定義的新四層(SWU層、MVU層、Bn_Relu層和MaxPool層),且每層中的Bn_Relu和MaxPool是可選的(圖中用虛線框標出),每層都有獨立緩存空間存儲對應層參數。同時,為了提高效率,每層內部也最大程度展開為流水形式。

我們將所有層都置于片上,當上一層有計算輸出時,下一層立即開始計算,各層同時運行。通過計算量分配各層所需要的邏輯資源,使得每層的時延趨向一致,使加速器運行效率最大化。

系統框架及優化設計

基于上述設計思想,最終實現的系統框圖如下。其中,我們采用DMA搬運數據,CPU負責任務調度工作。為了實現加速器IP與CPU之間的并行,我們在外部RAM中開辟了兩塊緩沖區輪流為加速器提供圖片數據。

由于計時規則在五月份做出了調整,將讀入圖片的時間和功耗也計入在內,而我們在五月版提交代碼的速度瓶頸主要卡在讀圖(Load image)時延。針對這個問題,我們對于系統待處理的任務重新進行了更為細致的優化部署。由于待處理任務分為四個部分:Load image、Resize image(簡寫為Resize)、Compute CNN(簡寫為CNN)、Calculate bounding box(簡寫為Calc bbox)。我們分別在PS端進行多核并行優化處理,在PS-PL端進行了負載均衡處理,從而優化了任務在PS和PL端的部署,該過程對最終成績中FPS提升貢獻很大。

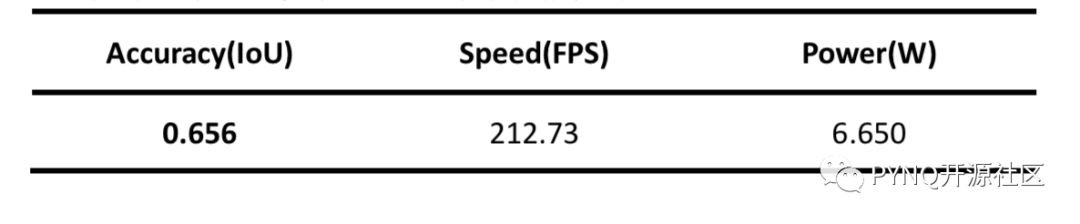

我們的成績

基于上述設計,最終的實現的加速方案性能如下:

。

跟前兩年的結果相比,雖然我們的精度(IoU)略有損失,但在速度方面我們有了大幅度地提升。

03

總結

上述是我們在2020DAC-SDC中所做的一些努力。這是我們團隊第一次參加DAC-SDC國際大賽,從關注該賽項到今天,我們一邊摸索一邊前進,很感謝組委會提供了這樣的平臺給我們實踐鍛煉和摸索提升的機會。身處計算機體系結構發展的黃金時代是我們這代人的幸運,相信未來系統設計必然將向著更精準、更高效、更低耗的方向邁進,我們也希望能夠通過努力與各位同仁共同見證這個時代的輝煌。同時,我們的設計也已經開源在:https://github.com/heheda365/ultra_net

04

團隊介紹

2020DAC-SDC Top-3的BJUT_Runner團隊來自北京工業大學信息學部張文博老師和包振山老師帶領的異構計算研究小組。參加本次比賽的團隊成員包括:詹康(圖中右下)、郭俊南和宋秉彥(圖中左下)。受2020年新型冠狀病毒疫情(COVID-19)影響,在整個參賽環節,團隊成員一直采用在線研討方式進行溝通(下圖為本組指導教師和所有成員在線合影)。

原文標題:打破常規,深度結合FPGA架構優勢|2020DAC- SDC冠軍作品開源與技術分享

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601867 -

dac

+關注

關注

43文章

2271瀏覽量

190841 -

開源

+關注

關注

3文章

3252瀏覽量

42407

原文標題:打破常規,深度結合FPGA架構優勢|2020DAC- SDC冠軍作品開源與技術分享

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ARM開發板與FPGA的結合應用

理解ECU數據流的分析方法

請問TLV320AIC3254EVM-K怎么讀取音頻數據流?

FPGA在圖像處理領域的優勢有哪些?

淺談國產異構雙核RISC-V+FPGA處理器AG32VF407的優勢和應用場景

統一日志數據流圖

FPGA在自動駕駛領域有哪些優勢?

使用CYUSB3014實現USB3VISION,不能成功發送DSI數據流是怎么回事?

ESP32如何在不漏數據的情況下采集數據流?

珠海鏨芯實現28納米FPGA流片

2020DAC- SDC冠軍作品分享,充分結合FPGA數據流架構的優勢

2020DAC- SDC冠軍作品分享,充分結合FPGA數據流架構的優勢

評論