芯片前端工程中,測試驗證的核心理念:以提高覆蓋率為核心。設計工程師需要關心的主要有行覆蓋率(Block),條件覆蓋率(Expression),翻轉覆蓋率(Toggle),狀態機覆蓋率。本文從ASIC設計的角度上來討論,如何寫出高覆蓋率的Verilog代碼。assign慎用按位運算邏輯,& | ^ ^~和三目運算符,慎用。使用這樣的描述方式本身功能并沒有什么問題,而且寫起來很爽,但是在很多情況下覆蓋率是真的不好收。

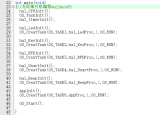

assign mult_a[3:0] = ({4{mult0_vld}} & mult_a0) | ({4{mult1_vld}} & mult_a1) | ({4{mult2_vld}} & mult_a2)

用或門和與門實現的一個選擇器的功能,前提是vld不能同時有效,相對于下面第二種寫法可能會節省一點門。但是問題我們在收集Expression時需要分析每一個條件是否跑到0/1,上面一共有六個信號,所以0、1隨機組合的情況就有2的6次方種,mult_a0作為數據端,如果沒有出現過全0的情況,通過定向case可以覆蓋到,但如果是參數作為選擇器的輸入端,那么參數本身就是有永遠不為0的情況,定向case也無法通過。

所以這個時候就只能把它waive(放棄)/exclude(排除)掉,并解釋原因。如果只有幾條這樣的寫法還好,如果有成百上千條,那么就需要重復上面的操作上千次。單純的體力活,沒有任何技術含量。但是直接換一種寫法。

always @(*)begin if(mult0_vld) mult_a[3:0] = mult_a0; else if(mult1_vld) mult_a[3:0] = mult_a1; else // if(mult2_vld) mult_a[3:0] = mult_a2;end

這樣寫覆蓋率只會檢查行覆蓋率,基本上哪一行沒跑到一目了然,也并不需要多余的體力勞動。代碼可讀性也很高。第二種可能會消耗更多的邏輯,但是對于整體的系統而言,也是不值一提的。換句話說,扣這一毛兩毛的,要抓大頭。if-else括號中的條件不要太多

always @(*)begin if(data_vld && mode_sel && enable_flag && (data_num[3:0] 》 4‘d7) && (ram_addr[4:0] 》 4’d15) && 。。。)end else 。。。

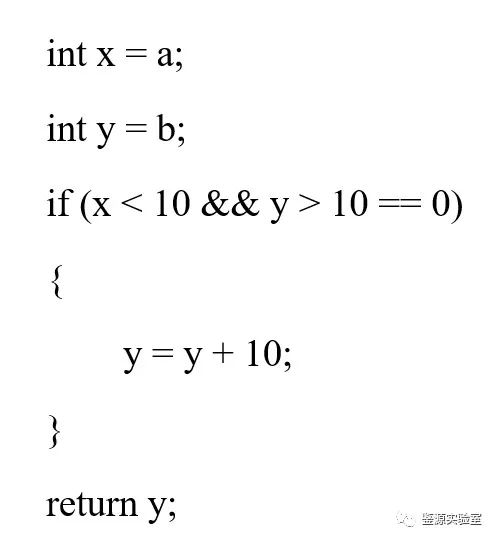

當然最開始的時候肯定不是這樣的設計,造成如此冗長的邏輯,大概率是后期調試打的補丁,可以把一些條件拿出來專門做一個信號,會讓條件覆蓋率分析容易很多,不然這么長的選擇,真不是給人看的。cur_state不可能同時出現在兩個狀態上在控制上用狀態機中,假如有這樣的邏輯。

assign enable = ((cur_state != STATE_A) && (next_state == STATE_A)) || ((cur_state != STATE_B) && (next_state == STATE_B))

這樣的寫法目的是在狀態跳轉時產生一個脈沖信號,不過在條件覆蓋率中會檢查這兩個選擇條件,cur_state != STATE_A為0與cur_state != STATE_B為0同時滿足的情況。仔細想一下,cur_state != STATE_A為0就代表cur_state現在就是STATE_A狀態,cur_state != STATE_B為0就是代表cur_state現在就是STATE_B狀態,那么,cur_state怎么可能同時為兩個狀態呢。這樣的情況要么就拆開寫要么就別寫。case語句的default分支考慮周全

always @(*)begin case(in[1:0]) 2‘d0 : data[1:0] = 2’d0; 2‘d1 : data[1:0] = 2’d1; 2‘d2 : data[1:0] = 2’d2; default : data[1:0] = 2‘d3; endcase end

case語句不寫default分支會產生鎖存器,如果case中的所有情況都達到,就可以不用寫default分支,但在ASIC設計中可能工具會報lint,所以這樣的寫法是最完美的。這樣的寫法對于in這個變量如果有規定取值范圍,哪一個值沒取到也一目了然。教科書式的反面教材

always @(*)begin if(start) cnt 《= ’d0; else if(((para == 3) && (cnt != 3)) || ((para == 4) && (cnt != 7)) || ((para == 5) && (cnt != 15)) || ((para == 6) && (cnt != 31))) cnt 《= cnt + 1‘d1;。。.end

這樣的寫法我愿稱之為教科書式的反面教材。首先,計數器的常規套路是給一個使能進行計數,記到一個值然后給清零,上面這樣的寫法是直接給一個使能信號清零,然后用未記到想要的最大值來做使能。第二點是,這樣的寫法和上面cur_state同時出現在兩個狀態上,是一樣的。else if里面的條件進行條件覆蓋率檢查,會出現cnt != 3 cnt != 7 cnt != 15 cnt != 31 兩兩之間或者及以上同時為0的隨機組合,那么cnt一個時刻只能是一個值,必不可能滿足同時等于多個值的情況。參數的取值范圍一個參數的取值范圍是0,1,2三個值,你做了一個這樣的vld

assign data_vld = (param == 0) || (param == 1) || (param == 2);

條件覆蓋率檢查會出現,上面三個條件都為0的情況,但是這個參數配置只有這三個值,不可能去其他值,也是一個典型的情況。換一種寫法。最后很多的代碼寫法,工具有smart exclude也會自動waive一些分支,不過工具也沒那么smart,還是需要自己在編碼的時候注意,盡量避免很多體力活。評論區支持互動回復蓋樓了,關于這個問題你還有什么想法,歡迎評論區留言交流。

編輯:jq

-

芯片

+關注

關注

454文章

50460瀏覽量

421965 -

asic

+關注

關注

34文章

1195瀏覽量

120346 -

鎖存器

+關注

關注

8文章

905瀏覽量

41448 -

選擇器

+關注

關注

0文章

106瀏覽量

14523

原文標題:如何寫出高覆蓋率的Verilog代碼?

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何寫出穩定的單片機代碼

Verilog硬件描述語言參考手冊

synopsys 的design ware:DW_fpv_div,浮點數除法器,默認32位下,想提升覆蓋率(TMAX),如果用功能case去提升覆蓋率呢?

怎么樣提高verilog代碼編寫水平?

FPGA Verilog HDL代碼如何debug?

利用靜態檢查工具完善功能安全中測試覆蓋率

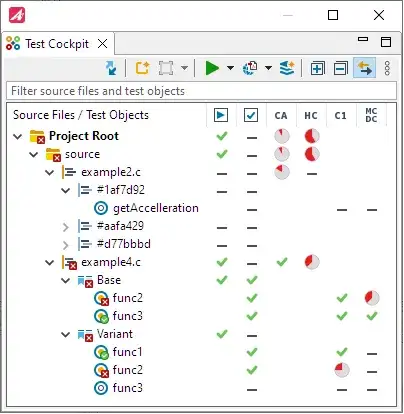

單元測試工具TESSY 新版本亮點速覽:提供測試駕駛艙視圖、超級覆蓋率、代碼訪問分析、增強覆蓋率審查

如何將SystemVerilog斷言屬性和覆蓋屬性置于在設計上?

verilog function函數的用法

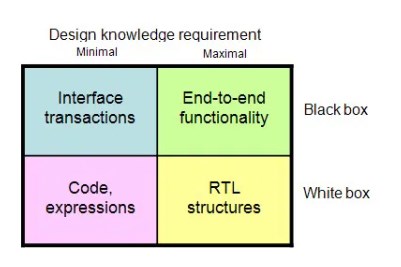

軟件代碼結構化覆蓋測試-MC/DC覆蓋

怎么才能寫出高覆蓋率的Verilog代碼?

怎么才能寫出高覆蓋率的Verilog代碼?

評論