Verdi是用來仿真以及debug波形的工具,但它不能夠用來編譯verilog和systemverilog文件,所以需要借助第三方EDA工具去做編譯的工作。

這里主要分享一下使用questasim和verdi的聯合仿真。

由于verdi工具支持FSDB格式的波形文件,所以在仿真時要把文件的信號轉存到FSDB格式的波形文件中,這里需要借助一個共享的庫文件:novas_fli.so.它通常位于目錄:

《VERDI_HOME》/share/PLI/MODELSIM/${PLATFORM}。

首先需要把上面的庫文件路徑添加到系統的環境變量LD_LIBRARY_PATH 中,如下:

setenv LD_LIBRARY_PATH ${VERDI_HOME}/share/PLI/MODELSIM/${PLATFORM}:$LD_LIBRARY_PATH

然后在仿真的時候,命令行中添加如下:

vsim -pli novas_fli.so work.test do dump_fsdb_questa.tcl +fsdb+autofluash

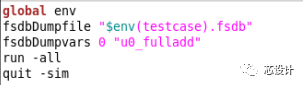

dump_fsdb_questa.tcl的內容如下:

fsdbDumpfile “test.fsdb”fsdbDumpvars 0 “test”run

02

舉例說明

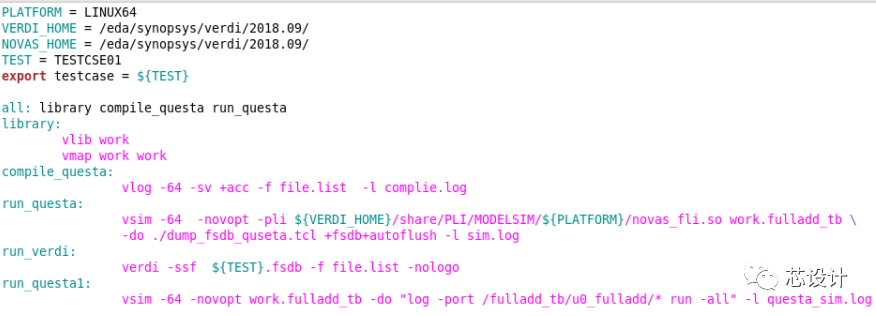

比如要驗證一個簡單的全加器,其Makefile的自動化腳本如下:

在dump_fsdb_questa.tcl的內容如下:

在terminal中輸入下面指令(運行編譯和仿真):

make all

編譯仿真通過后,會在在當前的工作目錄中生成:TESTCASE01.fsdb文件。

之后在terminal中輸入下面指令(打開波形文件):

make run_verdi

本篇文章主要分享了如何通過自動化腳本的方式實現Questasim和Verdi的聯合仿真教程。

原文標題:Questasim和Verdi的聯合仿真教程

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

仿真

+關注

關注

50文章

4041瀏覽量

133414 -

eda

+關注

關注

71文章

2708瀏覽量

172876 -

Verdi

+關注

關注

0文章

22瀏覽量

8760 -

questasim

+關注

關注

0文章

5瀏覽量

7483

原文標題:Questasim和Verdi的聯合仿真教程

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用OpenSCAD腳本自動化電容式觸摸傳感器PCB設計

開關電源自動化測試設備:如何實現自動化測試?

機械自動化和電氣自動化區別是什么

機械自動化是自動化的一種嗎

如何實現PLC的自動化控制邏輯

機械制造與自動化是自動化類嗎

工業自動化和自動化區別是什么

自動化構建環境在FPGA設計中的應用

電源測試怎么自動化?電源模塊自動化測試系統如何實現?

如何通過自動化腳本實現Questasim和Verdi的聯合仿真

如何通過自動化腳本實現Questasim和Verdi的聯合仿真

評論