嵌入式系統就:是一個具有特定功能或用途的計算機軟硬件結合體,或指裝入另一個設備并且控制該設備的專用計算機系統 嵌入式系統的最大特點是其具有目的性和針對性,即每一套嵌入式系統的開發都有其特殊的應用場合與特定功能。嵌人式系統包含硬件和軟件兩部分。硬件架構以嵌入式處理器為中心,配置存儲器、I/O設備、通信模塊等;軟件部分以軟件開發平臺為核心,向上提供應用編程接口API,向下屏蔽具體硬件特性的板級支持包BSP。嵌入式系統中,軟件和硬件緊密配合,協調工作,共同完成系統預定的功能。

擴頻通信是當今國際上高新技術熱點之一,其理論基礎是香農(C.E.Shannon)的信道容量公式。該公式表明,在高斯信道中,當傳輸系統的信號噪聲功率比SNR下降時,可用增加系統傳輸帶寬W的辦法來保持信道容量C不變;對于任意給定的信號噪聲功率比,可以用增大傳輸帶寬來獲得較低的信息差錯率。擴頻技術正是利用這一原理,用高速率擴頻碼來達到擴展待傳輸數字信息帶寬的目的。擴頻通信系統的帶寬比常規通信體制大幾百倍至幾千倍,故在相同信噪比的條件下,具有較強的抗噪聲干擾能力。

1 基于嵌入式系統的數字擴頻收發信機的硬件設計

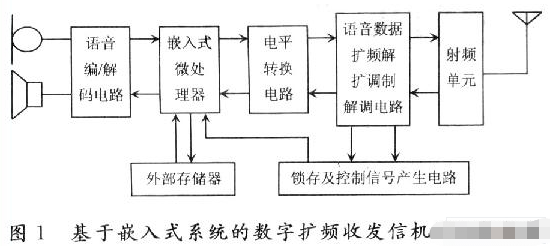

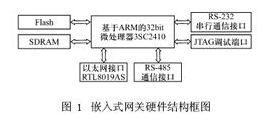

設計的基于嵌入式系統的數字擴頻收發信機結構框圖如圖1所示。

該數字擴頻收發信機是雙通道的(圖中只畫出單一通道)。通道由語音編解碼電路、嵌入式微處理器、電平轉換電路、語音數據擴頻解擴調制解調電路、鎖存及控制信號產生電路、外部存儲器和射頻單元電路組成。

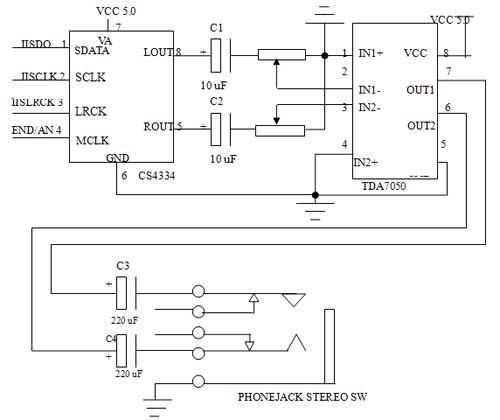

語音編解碼電路采用PHLIPS半導體公司生產的低功耗立體聲音頻編解碼芯片UDAl344TS。該芯片3.O V電源供電,可工作在L3微控制器模式,也可工作在靜態引腳工作模式,通過模式控制引腳MCl(8腳)、MC2(21腳)設置為靜態引腳工作模式(均為高電平),在該模式下,可控制的特征有系統時鐘選擇、數據輸入/輸出格式設置、重低音和靜音控制以及ADC控制,這些特征是由引腳MPl(9引腳)、MP2(13引腳)、MP3(14引腳)、MP4(15引腳)、MP5(20引腳)控制的。

嵌入式微處理器選用SAMSUNG公司為手持設備設計的低功耗、高集成度基于ARlM920T核的微處理器S3C2410X。該處理器集成了16 KB指令和16 KB數據緩存、MMU、外部存儲器控制器、LCD控制器、NAND FLASH控制器、4個DMA通道、3個UART通道、1個I2C總線控制器、1個I2S總線控制器、4個PWM定時器和一個內部定時器、通用I/O口、實時時鐘、8通道10位ADC和觸摸屏接口、USB主/從接口、SD/MMC卡接口等。

語音數據擴頻解擴調制解調電路選用Zilog公司研制的可編程單片直接序列擴頻收發芯片Z87200。該芯片包括發送部分、接收部分和控制部分,它將擴頻通信收發主要電路的各個部分都集成于一塊100個管腳的芯片中。發送部分包括了發送數據的白化處理、串并變換、差分編碼、PN碼產生、擴頻、QPSK/BPSK調制及發定時控制,完成由數據輸入到已調中頻信號輸出的擴頻、調制處理。接收部分包括中頻到基帶的數字下變換、PN碼產生、數字匹配濾波、解擴、相關峰檢測、差分解調、并串轉換、去白化處理、數控振蕩器及位定時處理等,完成由數字中頻信號輸入到數據輸出的全過程解調解擴處理。此外,Z87200還設置了86 B的片內寄存器,用于對芯片功能的編程設置,使得對擴頻系統的設置具有靈活性,芯片具有通用性,可與計算機或單片微處理器連接,完成對內部寄存器的編程控制。

電平轉換電路采用MAXIM公司的雙向8通道電平轉換芯片MAX3001E。由于嵌入式微處理器S3C2410X工作電壓通常是3.3 V,而直序擴頻收發器Z87200工作電壓通常是5 V,所以可采用多個MAX3001E來連接這兩個芯片,以實現它們之間。的邏輯電平轉換。

鎖存及控制信號產生電路采用74LV373鎖存器和復雜可編程邏輯器件EPM7128SLC84-15。在通過接口控制單元向直序擴頻收發器Z87200讀寫數據時,為了確保數據的穩定,采用74LV373鎖存器對要讀寫的數據先進行鎖存,然后才完成數據的讀寫。EPM7128SLC84-15是ALTERA公司生產的一款MAX7000S系列的CPLD器件,用VHDL編程設計一個8位同步移位寄存器和一個9位同步計數器,在.Max +PlusⅡ開發平臺上進行編譯仿真后下載在CPLD器件EPM7128SLC84-15上。由于直序擴頻收發器Z87200被設置為突發工作模式,為方便數據處理,可設置突發塊的長度為8符號/幀,配合使用9位計數器和8位移位寄存器,每移位9次可得到真正需要的8位語音數據。

射頻單元采用北京迅通科技公司的PTR8000(以nRF905作為數據無線傳輸芯片)高性能嵌入式無線模塊,它專為點對多點無線通信設計,內置數據協議和CRC檢錯,可工作在430/868/915 MHz,工作電壓在1.9~3.6 V之間,最大發射功率+10 dBM,高抗干擾GFSK調制,可跳頻,數據速率50 Kb/s,獨特的載波監測輸出,地址匹配輸出,地址就緒輸出。由于與RF協議相關的高速信號處理部分已經嵌入在模塊內部,PTR8000可與各種單片機配合使用,也可以與DSP等高速處理器配合使用;PTR8000提供一個SPI接口,速率由微控制器自己設定的接口速度決定,在RX(接收)模式中,地址匹配(AM)和數據準備就緒(DR)信號通知MCU一個有效的地址和數據包已經各自完成,微控制器即可通過SPI讀取接收的數據。在TX(發送)模式中,PTRR8000自動產生前導碼和CRC校驗碼,數據準備就緒(DR)信號通知MCu數據傳輸完成。

外部存儲器由一塊8 MB的SDRAM(采用HY57V641620)和一塊2 MB的FLASH(采用HY29LVl60)構成,主要用于存放程序和數據。

2 軟件設計

嵌入式系統的軟件開發采用武漢創維特信息技術有限公司的ADT IDE集成開發環境,它提供高效、清晰、可視化的嵌入式軟件開發平臺,包括一整套完備的面向嵌入式系統的開發和調試工具:編輯器、編譯器、鏈接器、工程管理器以及調試器等,它運行于WindowsNT/95/98/2000/XP,采用類似Visual Studio界面風格,支持中、英文版本。

在用戶的應用程序之前,需要由專門的一段代碼完成對系統的初始化,即系統啟動加載程序。當ARM微處理器上電或者復位之后,處理器從0x0取值,在這個地址處安排的程序就是系統啟動加載程序。由于這類代碼直接面對處理器內核和硬件控制器進行編程,故采用匯編語言,其任務包括建立異常向量表、重構異常向量表、初始化存儲器系統、初始化堆棧、初始化應用程序執行環境、屏蔽所有中斷和呼叫主應用程序。

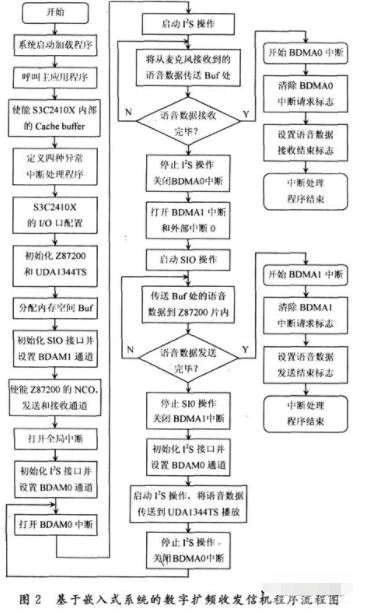

收發機系統的主程序主要完成芯片的初始化、接口的配置、語音數據流控制和中斷處理等工作,使得收發機系統在嵌入式微處理器的控制下能有效地完成語音的錄人、發送、接收和播放全過程,基于嵌入式系統的數字擴頻收發信機程序流程圖如圖2所示。

3 實驗結果

用匯編語言編寫系統啟動加載程序,用c語言編寫嵌入式微處理器的數字擴頻收發信機程序,在ADTIDE集成開發環境下添加源代碼,保存后加入到工程中進行設置和編譯,通過后經過JTAG簡易調試器,將應用程序燒錄到FLASH中,下載到SDRAM中。將語音編解碼電路、嵌入式微處理器S3C2410X、電平轉換電路、語音數據擴頻解擴調制解調電路、鎖存及控制信號產生電路、外部存儲器和射頻單元電路正確焊接在PCB板上,上電,運行程序。

在發送端,話音通過麥克風送人語音編解碼芯片UDAl344TS,經過語音編碼處理后,產生I2-bus格式的串行語音數據通過標準I2S語音接口傳送到嵌入式微處理器S3C2410X。S3C2410X將得到的8位語音數據存儲到預先分配好的數據區,接著將該數據通過同步串行接口SIO一位一位地發送到語音數據擴頻解擴調制解調芯片Z87200片內進行擴頻、BPSK調制等一系列處理后,得到8位數字中頻語音信號;最后,通過射頻單元PTR8000無線發送出去。

在接收端,通過射頻單元PTR8000無線接收到8位數字中頻語音信號,送入z87200片內進行解擴、解調等一系列處理,得到串行語音數據信號;該信號被送入CPLD器件EPM7128SLC84-15的8位同步移位寄存器;CPLD每得到一個8位語音數據就將該數據鎖存并產生一個外部中斷,通知嵌入式微處理器S3C2410X將這8位語音數據讀走;最后在S3C2410X的控制下將語音數據通過I2S接口傳送給語音編解碼芯片UDAl344TS,解碼處理后通過揚聲器播放出來。

發送通道實現了話音錄人、擴頻和BPSK調制、無線發送;接收通道實現了無線接收、BPSK解調、解擴和播放。兩通道可同時進行;在無線傳輸時,采用PTR8000高性能嵌人式無線模塊,最大傳輸速率可達20 Kb/s,最遠傳輸距離可達1 km左右。

4 結 語

闡述了嵌入式系統和擴頻通信的含義,以嵌入式微處理器S3C2410X為核心,利用Z87200,UDAl344TS,PTR8000等模塊設計出了數字擴頻收發信機。該文創新點是將嵌入式技術和擴頻技術融合在一起,同時采用ADT IDE集成開發環境調試嵌入式系統軟件,用嵌入式微處理器對系統其他芯片進行編程控制,因而具有很好的靈活性和通用性;根據所提出的設計思路,可方便地設計其他無線通信系統,有廣闊的應用前景和很好的經濟效益。

責任編輯:gt

-

微處理器

+關注

關注

11文章

2247瀏覽量

82311 -

通信系統

+關注

關注

6文章

1174瀏覽量

53285

發布評論請先 登錄

相關推薦

擴頻通信技術教程

sec s3c2410x b/d 的驅動

擴頻通信系統簡介

S3C2410X微處理器電子資料

S3C2410X中文數據手冊

什么是擴頻通信,擴頻通信的定義

微處理器S3C44B0X音頻文件播放

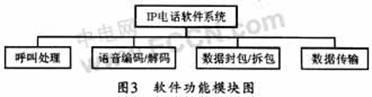

ARM9微處理器S3C2410的IP電話通信設計

FFT-s3c2410說明書

s3c2410芯片手冊s3c2410中文手冊32位RISC微處

S3C2410X微處理器與SPI接口在觸摸屏驅動程序中的應用

基于Linux操作系統和S3C2410微處理器實現GPS實時導航系統的設計

基于S3C2410微處理器和Linux實現嵌入式網關的設計

基于S3C2410X微處理器實現擴頻通信系統的設計

基于S3C2410X微處理器實現擴頻通信系統的設計

評論