航天工程領(lǐng)域中,星地通訊等遠(yuǎn)距離遙測遙控是嵌入式衛(wèi)星數(shù)管計算機(jī)重要功能之一,利用三線制同步串行遙測遙控通道對指令和數(shù)據(jù)進(jìn)行收發(fā)操作是通信鏈路的重要環(huán)節(jié)。

目前許多處理器芯片都已集成了同步串行接口,但基于三線制同步串行接口的處理器并不多。利用傳統(tǒng)設(shè)計方法所實(shí)現(xiàn)的三線制同步通信硬件電路接口雖然能滿足一般工程設(shè)計要求,但在“低成本、小體積、低功耗和靈活性”設(shè)計理念的推動下,傳統(tǒng)設(shè)計顯然弊大于利。采用可編程邏輯器件CPLD/FPGA技術(shù),對三線制同步串行通信接口電路進(jìn)行結(jié)構(gòu)設(shè)計與實(shí)現(xiàn),可以大幅度減小系統(tǒng)體積,降低功耗,提高設(shè)計的靈活度。同時,還可以在其中增加其他邏輯功能模塊,并能很方便地應(yīng)用到相關(guān)的嵌入式系統(tǒng)中。

1 三線制同步串行通信機(jī)理

三線制同步串行通信時,發(fā)送端和接收端必須使用共同的時鐘源才能保持它們之間的準(zhǔn)確同步。為達(dá)到準(zhǔn)確同步的目的,其中一個方法就是采用編碼和解碼的原理,即在發(fā)送端利用編碼器把要發(fā)送的數(shù)據(jù)和發(fā)送時鐘組合在一起,通過傳輸線發(fā)送到接收端,在接收端再用解碼器從數(shù)據(jù)流中分離出接收時鐘。常用的編碼解碼器有曼徹斯特編碼解碼及NRZ-L碼。本文中收發(fā)信號采用的碼型是NRZ-L碼。

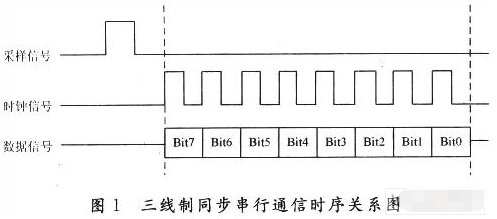

三線制同步串行通信主要包括三個信號:采樣信號(也叫幀同步信號)、時鐘信號和串行數(shù)據(jù)信號,其時序邏輯關(guān)系如圖1所示。

從圖1可看出,數(shù)據(jù)接收或發(fā)送時,首先幀同步信號先觸發(fā)一個瞬時啟動脈沖,之后保持低電平有效,時鐘信號緊隨其后,數(shù)據(jù)在時鐘信號的上升沿保持穩(wěn)定,并開始采樣和傳輸,每個時鐘周期收發(fā)一位字符數(shù)據(jù),串行數(shù)據(jù)成批連續(xù)發(fā)送和接收。

2 三線制同步串行通信控制器接口結(jié)構(gòu)設(shè)計

2.1 基于傳統(tǒng)設(shè)計的硬件電路接口實(shí)現(xiàn)

在三線制同步串行通信控制器接口的傳統(tǒng)硬件電路設(shè)計中,需使用多片元器件來實(shí)現(xiàn)其功能,包括:異步四位計數(shù)器、移位寄存器、8位D觸發(fā)器、與門、與非門和反相器等主要功能器件,接口電路原理圖在ProteI 99 SE中實(shí)現(xiàn)。

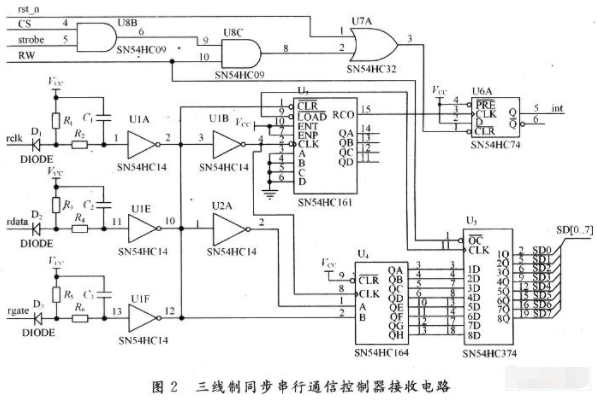

三線制同步串行通信控制器接收接口硬件電路如圖2所示。

![]()

從圖2中可看到,通過復(fù)位信號rst n、片選信號CS、門控信號strobe和讀寫信號RW等的不同組合,實(shí)現(xiàn)邏輯控制功能。通過異步四位計數(shù)器SN54HC161的計數(shù)功能,使得移位寄存器SN54HC164順利進(jìn)行數(shù)據(jù)的串/并轉(zhuǎn)換,將8位并行數(shù)據(jù)通過8位D觸發(fā)器SN54HC374鎖存在內(nèi)部總線上等待系統(tǒng)接收。在輸出端,通過雙D觸發(fā)器SN54HC74產(chǎn)生中斷信號int,通知系統(tǒng)內(nèi)的微處理器進(jìn)行數(shù)據(jù)接收操作。

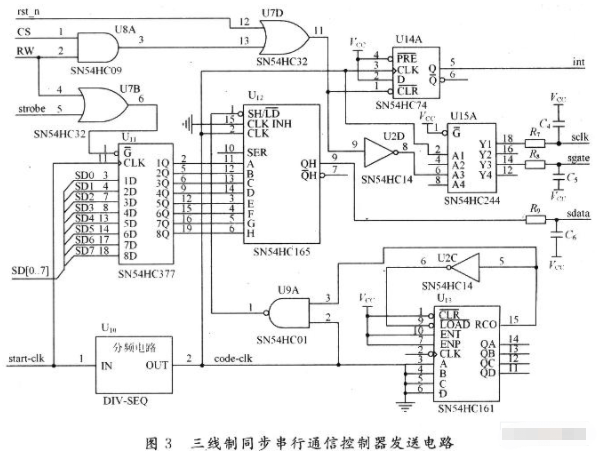

三線制同步串行通信控制器發(fā)送接口硬件電路如圖3所示。

![]()

從圖3可知,系統(tǒng)時鐘start-clk通過分頻電路模塊產(chǎn)生發(fā)送時鐘原始信號code-clk,用于電路的時鐘狀態(tài)控制。系統(tǒng)內(nèi)的微處理器將要發(fā)送的8位并行數(shù)據(jù)通過8位D觸發(fā)器SN54HC377,將數(shù)據(jù)鎖存在其Q端口等待發(fā)送,然后在異步四位計數(shù)器SN54HC161的計數(shù)功能控制下,移位寄存器SN54HC165進(jìn)行數(shù)據(jù)的并/串轉(zhuǎn)換操作。在輸出端,通過雙D觸發(fā)器SN54HC74產(chǎn)生中斷信號,然后開始通過單向總線驅(qū)動器SN54HC244進(jìn)行幀同步信號、時鐘信號及數(shù)據(jù)的發(fā)送操作。

2.2 基于CPLD/FPGA的接口結(jié)構(gòu)設(shè)計

為解決傳統(tǒng)硬件電路元器件多,功耗大,體積大等缺點(diǎn),利用CPLD/FPGA技術(shù),同時結(jié)合VHDL硬件描述語言設(shè)計三線制同步串行通信控制器接口已成為一種必然,結(jié)合三線制同步串行通信機(jī)理,設(shè)計出了基于CPLD/FPGA的三線制同步串行通信控制器接口內(nèi)部結(jié)構(gòu),其功能結(jié)構(gòu)如圖4所示。

整個三線制同步串行通信控制器接口的內(nèi)部結(jié)構(gòu)主要由時鐘分頻模塊、系統(tǒng)接口控制邏輯、數(shù)據(jù)接收模塊、數(shù)據(jù)發(fā)送模塊等四大模塊構(gòu)成。

時鐘分頻模塊主要用于數(shù)據(jù)收/發(fā)模塊產(chǎn)生同步時鐘信號。系統(tǒng)接口控制邏輯主要用于各種邏輯功能信號的控制,同時還可以接收_中斷仲裁邏輯模塊產(chǎn)生的中斷信號,控制數(shù)據(jù)的接收或者發(fā)送操作。數(shù)據(jù)接收模塊是三線制同步串行通信控制器接口進(jìn)行數(shù)據(jù)接收的核心部分,其模塊結(jié)構(gòu)如圖5所示。

數(shù)據(jù)接收流程:在幀同步脈沖信號觸發(fā)下,串行數(shù)據(jù)在時鐘信號rclk上升沿到來時保持穩(wěn)定,并通過rdata信號線進(jìn)入數(shù)據(jù)接收模塊。在該模塊內(nèi)部,串行數(shù)據(jù)經(jīng)過串/并變換,接收FIFO作為數(shù)據(jù)緩沖器,將接收到的數(shù)據(jù)鎖存在VHDL程序指定的兩個地址寄存器中,一個地址單元存儲數(shù)據(jù)的高八位,另外一個地址單元存儲數(shù)據(jù)的低八位,當(dāng)數(shù)據(jù)存滿這兩個地址單元后,接口向系統(tǒng)發(fā)出一個“接收緩存滿”的接收中斷標(biāo)志int,系統(tǒng)微處理器響應(yīng)后,數(shù)據(jù)被全部取出,并行數(shù)據(jù)被送往系統(tǒng)的數(shù)據(jù)總線上,重復(fù)進(jìn)行相同操作,直至連續(xù)接收完所有數(shù)據(jù),數(shù)據(jù)接收過程結(jié)束。

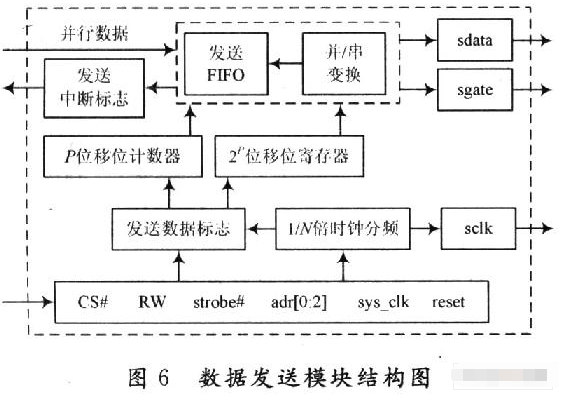

數(shù)據(jù)發(fā)送模塊也是三線制同步串行通信接口進(jìn)行數(shù)據(jù)發(fā)送的核心部分,其模塊結(jié)構(gòu)如圖6所示。

數(shù)據(jù)發(fā)送流程:在sgate幀同步脈沖信號觸發(fā)下,系統(tǒng)數(shù)據(jù)總線上的并行數(shù)據(jù)在時鐘信號sclk上升沿到來時保持穩(wěn)定,并通過數(shù)據(jù)發(fā)送模塊開始數(shù)據(jù)發(fā)送。在模塊內(nèi)部,首先發(fā)送FIFO數(shù)據(jù)緩沖器,當(dāng)并行數(shù)據(jù)存滿該緩存單元后,數(shù)據(jù)發(fā)送模塊向系統(tǒng)發(fā)出一個“發(fā)送緩存滿”的發(fā)送中斷標(biāo)志int,系統(tǒng)微處理器響應(yīng)后,并行數(shù)據(jù)從發(fā)送FIFO內(nèi)讀出,經(jīng)過并/串變換成串行數(shù)據(jù),最高位MSB最前,最低位LSB最后,并被送往發(fā)送數(shù)據(jù)信號線Sdata上,發(fā)送至外圍設(shè)備接口,重復(fù)進(jìn)行相同操作,直至發(fā)送完畢所有數(shù)據(jù),數(shù)據(jù)發(fā)送過程結(jié)束。

3 結(jié) 語

本文在介紹了三線制同步串行通信機(jī)制基礎(chǔ)上,首先對三線制同步串行通信接口進(jìn)行了硬件電路設(shè)計,然后針對傳統(tǒng)電路設(shè)計方式的不足,構(gòu)建了基于CPLD/FPGA的三線制同步串行通信控制器接口結(jié)構(gòu),詳述了各個功能模塊及其工作原理,設(shè)計合理,并且滿足了實(shí)際應(yīng)用要求。目前,此接口結(jié)構(gòu)模塊已作為FPGA設(shè)計中的關(guān)鍵子模塊被成功應(yīng)用于某航天項目及其配套的硬件測試平臺中。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601851 -

cpld

+關(guān)注

關(guān)注

32文章

1247瀏覽量

169217 -

嵌入式

+關(guān)注

關(guān)注

5068文章

19019瀏覽量

303292

發(fā)布評論請先 登錄

相關(guān)推薦

Xilinx可編程邏輯器件的高級應(yīng)用與設(shè)計技巧絕版教程

可編程邏輯器件

怎么采用可編程邏輯器件設(shè)計數(shù)字系統(tǒng)?

PLD可編程邏輯器件

可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗指導(dǎo)書

什么是PLD(可編程邏輯器件)

EDA技術(shù)與應(yīng)用(可編程邏輯器件)

電可編程邏輯器件EPLD是如何設(shè)計的

可編程邏輯器件測試

采用可編程邏輯器件實(shí)現(xiàn)三線制同步串行通信的應(yīng)用設(shè)計

采用可編程邏輯器件實(shí)現(xiàn)三線制同步串行通信的應(yīng)用設(shè)計

評論