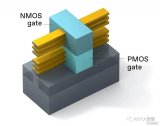

隨著摩爾定律的逐漸失效,縮小芯片尺寸的挑戰日益艱巨。但隨著新工藝和技術接連涌現,芯片設計規模仍在持續拓展。其中一種方式就是采用3DIC,它將硅晶圓或裸晶垂直堆疊到同一個封裝器件中,從而帶來性能、功耗和面積優勢。由于它能夠同時實現極端、異構和同構的集成,3DIC適合支持計算密集型工作負載,并提供了 2D 架構所不具備的密集性和可擴展性。

3DIC設計面臨哪些挑戰?

3DIC給AI、5G、數據中心、大型網絡系統、高性能計算等領域帶來變革的同時,也面臨著不少挑戰。從2D架構升級為3D架構,設計人員往往習慣于沿用自己熟悉的一套既定方法、工具和工作流來開發 SoC。這種思維定式導致設計人員在高度碎片化的環境中創建2.5D和3DIC設計,其中充斥著大量單點工具解決方案。目前,設計人員依然只能執行以人工操作為主的評估,由于缺乏綜合性的分析和反饋,這項任務既繁瑣又易出錯。

另一項挑戰在于,在整個設計流程中,各參與團隊的工作流效率和效力,這涉及架構、設計、實施、IP創建/集成、封裝等團隊。比如,在以往的2D環境中,將完成的芯片級設計轉交給封裝團隊,這是一個相對簡單的步驟。然而對于3DIC而言,這一環節有更多的反復,因為得出的設計可能達不到更加嚴格的封裝要求。

擁有超高收斂性環境的一體化3D設計應運而生

現有的各種單點工具只能解決復雜的3DIC設計中細枝末節的難題,更加高效的解決方案是采用統一的平臺,將系統級信號、功耗和散熱分析集成到同一套緊密結合的解決方案中。

新思科技通過3DIC Compiler為多裸晶片集成提供了統一的平臺,為3D可視化、路徑、探索、設計、實現、驗證及簽核提供了一體化的超高收斂性環境。該平臺建立在新思科技Fusion Design Platform高度可擴展的通用數據模型之上。該平臺在提高效率的同時,還可以擴展容量和性能,以支持實現數十億個裸晶間互連。該平臺提供全套自動化功能的同時,還具備電源完整性、注重優化散熱和降噪,從而減少迭代次數。

3DIC Compiler可以讓用戶切實體驗到裸晶芯片在先進節點表現的巨大設計生產力優勢,周轉時間從幾個月縮短為僅僅幾小時。此外,新思科技與Ansys達成合作,以 Ansys芯片封裝協同仿真工具為3DIC Compiler提供內部設計支持,從而提供全面的信號和電源完整性分析。

原文標題:為解決3DIC芯片設計難題,3DIC Compiler應運而生!

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

453文章

50396瀏覽量

421789 -

IC

+關注

關注

36文章

5898瀏覽量

175232

原文標題:為解決3DIC芯片設計難題,3DIC Compiler應運而生!

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯和半導體邀您相約IIC Shenzhen 2024峰會

天馬微電子受邀出席DIC EXPO 2024

新思科技攜手英特爾推出可量產Multi-Die芯片設計解決方案

天馬斬獲“DIC國際顯示技術創新大獎”

新思科技面向英特爾代工推出可量產的多裸晶芯片設計參考流程,加速芯片創新

維信諾斬獲2024 DIC AWARD 7項大獎

全光網應用面臨的挑戰

人工智能芯片在先進封裝面臨的三個關鍵挑戰

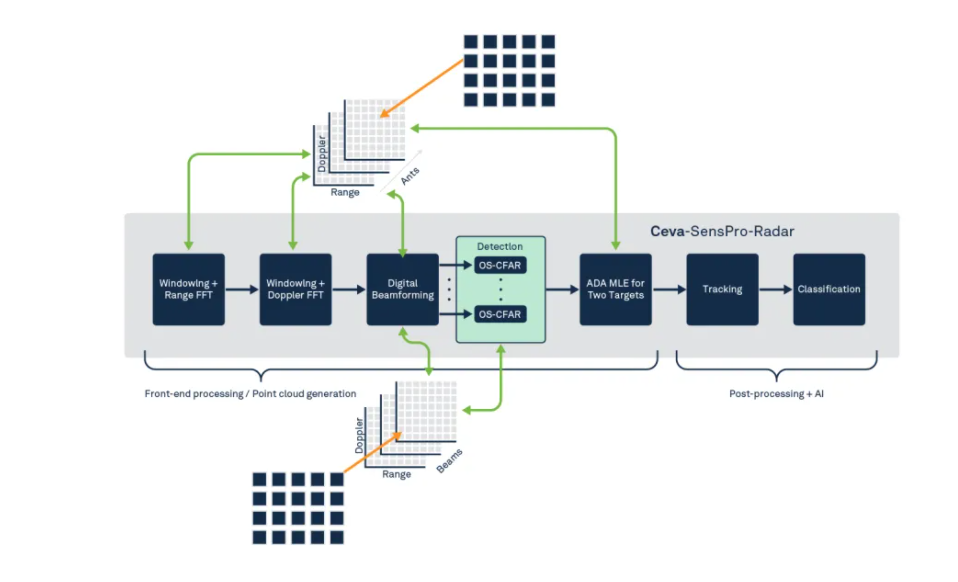

汽車雷達系統設計面臨的挑戰

現在3DIC設計面臨哪些挑戰?

現在3DIC設計面臨哪些挑戰?

評論