串行外圍設備接口SPI(serial peripheralinterface)總線技術是Motorola公司推出的一種微處理器、微控制器及其外設間的一種全/半雙工同步串行數據接口標準,具有連接線少、傳輸效率高等特點,因其硬件功能很強,與SPI有關的軟件就相當簡單,使CPU有更多的時間處理其他事務。

SPI接口一般采用4條連接線:串行時鐘線(SCK)、主機輸出/從機輸入數據線(MOSI)、主機輸入/從機輸出數據線(MISO)和低電平使能的從機選擇線(SS),有的還帶有中斷信號線(INT),半雙工或單向模式則不需要主機輸出/從機輸入數據線(MOSI)。為了在減少引腳的基礎上完成主從機的雙向通訊,本文采用半雙工機制實現了一種3線制雙向SPI總線模塊,即通過使能信號實現數據傳輸的方向控制,因此將主機輸出/從機輸入(MOSI)線和主機輸入/從機輸出線(MISO)線合并為一條雙向信號線。該模塊是某射頻芯片中的接口模塊,其作用是實現基帶芯片對射頻芯片的控制以及數據交換,而且為了便于和射頻電路集成,該模塊最終以硬IP形式實現。

1 SPI總線協議

射頻芯片的SPI接口具有兩個主要特征:Slave工作模式和半雙工方式通訊。

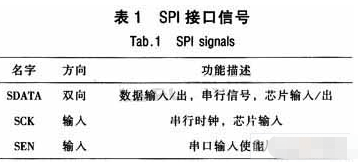

SPI接口信號描述如表1。

接口時序要求如下:

1)輸出時序

當SEN為高電平時,SPI接口處于輸出狀態。每次數據傳輸開始于SCK信號的上升沿。數據傳輸過程中,數據由SCK信號控制,并遵循下列規則:數據傳輸時,低位在前,高位在后;每個輸出數據位在SCK下降沿采樣;當本幀數據輸出達到24 bit時,結束數據輸出;當本幀數據輸出超過24 bit時,則多余位數全為高電平。

2)輸入時序

當SEN為低電平時,SPI接口處于輸入狀態。每次數據傳輸開始于SEN信號的下降沿,結束于其上升沿。數據傳輸過程中命令和數據有SCK和SEN信號控制,并遵循下列規則:數據傳輸時,低位在前,高位在后;每個輸入數據在SCK下降沿移入MOSI;當本幀數據輸入為24 bit時,當SEN轉為高電平時,將已輸入的24 bit數據寫入RF IC內部寄存器;當本幀數據輸入不足24 bit或多于24 bit時,放棄本幀輸入,等待下一幀。

射頻SPI接口的最大特點就是采用半雙工通訊機制,串行數據的輸入/輸出共用一條數據線,因此SPI接口數據通路的設計和普通的4線制SPI接口完全不同。

2 實現方案

2.1 總體結構

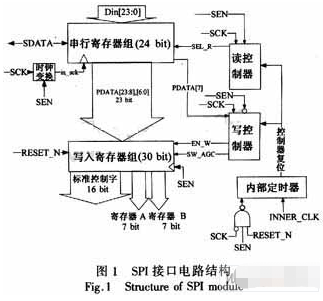

SPI接口電路主要由讀/寫控制器、串行寄存器組、輸出寄存器組和內部定時器四部分構成,如圖1所示。

在SPI接口模塊中,數據交換的核心是串行寄存器組,讀、寫控制器根據外部方向選擇信號SEN交替控制串行寄存器組的輸人和輸出。

2.2 串行寄存器組

串行寄存器的作用是接收射頻芯片內部狀態信息并轉換成24 bit串行數據輸出,以及接收外部串行控制字輸入并轉換成30 bit并行數據輸入射頻芯片,其基本結構如圖2所示。串行寄存器組是半雙工方式SPI接口設計的核心,輸入和輸出數據共享此數據通路,必須保證數據傳輸方向的正確切換。本文采用串行寄存器鏈+輸入選擇器方式實現輸入和輸出數據間的切換。

2.3 讀控制器

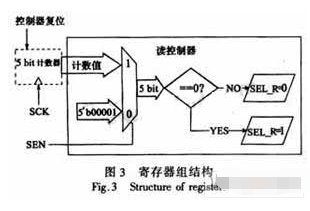

讀控制器的作用是在SEN為高電平的周期內,控制串行寄存器組在第一個SCK上升沿到來時接收指定的24 bit射頻芯片內部信號,并將最低位串行輸出,然后在剩下的23個時鐘周期內將余下的23 bit數據串行輸出,讀控制器結構如圖3所示。

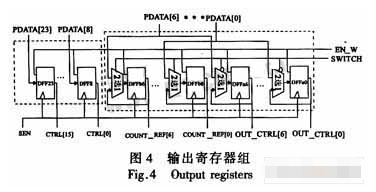

2.4 寫入寄存器組

寫入寄存器的作用是在SEN信號的上升沿接收串行寄存器組的輸出,并將結果寫入射頻芯片的內部模塊。其中射頻芯片比較特殊的要求是根據寫入控制字第7位選擇將串行輸入數據的第0~6 bit數據寫入兩個不同的控制寄存器中的一個,這樣,寫入寄存器組的輸出位數就變成了30 bit,輸入為23 bit。輸出寄存器的結構如圖4所示。

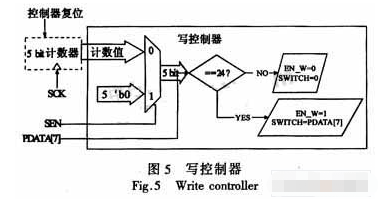

2.5 寫控制器

寫控制器的作用是在SEN信號的低電平周期內,判斷寫入數據是否恰好滿足24 bit以使能輸出寄存器組,另外根據寫入數據的第8位控制低7位數據的寫入方向(寄存器A或寄存器B)。寫控制器的結構如圖5所示。

3 實現結果

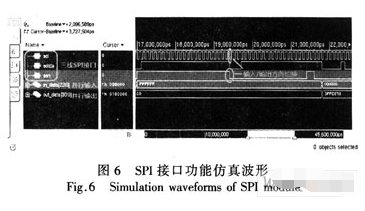

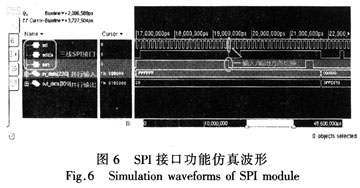

圖6是采用Verilos實現的SPI接口的部分功能仿真波形,測試激勵首先將SPI接口置于發送模式下(SEN為高電平),SPI接口將從內部獲得的信息碼“24’hFFFFFE”正確地串行發出;測試激勵再將SPI接口置于接收模式下(SEN為低電平),SPI接口正確接收外部發送的“24’hFFFFF8”,并轉換成內部的“30’h3FFC078”。為了保證收發方向切換在一個時鐘周期內完成,SEN信號的轉換在接口時鐘的下降沿完成。通過NC-Verilog仿真,SPI接口功能正確,工作時序符合設計要求。

4 結論

本SPI接口模塊已成功應用在一個射頻芯片中,以硬IP的形式集成進射頻模塊中。SPI接口電路在0.18 μm工藝下實現后的版圖總尺寸約為240 μm×460 μm,最高工作頻率原高于10 MHz的設計上限,相應在10 MHz下的功耗約為2 mW。

責任編輯:gt

-

射頻

+關注

關注

102文章

5471瀏覽量

166944 -

微處理器

+關注

關注

11文章

2221瀏覽量

81982 -

總線

+關注

關注

10文章

2817瀏覽量

87707

發布評論請先 登錄

相關推薦

如何采用半雙工機制設計3線制雙向SPI總線模塊?

CH573啟動半雙工模式是否支持硬件單線雙向通訊模式?

STM32F746如何實現半雙工通信的SPI函數?

SPI半雙工模式有沒有什么特別的技巧?

可以在Processor Expert上使用LPSPI組件進行半雙工SPI嗎?

半雙工,半雙工是什么意思

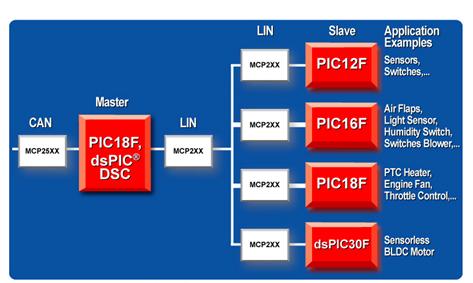

基于MCP200x設計的LIN雙向半雙工通信方案

3線制半雙工SPI接口解決方案

基于半雙工機制實現3線制雙向SPI模塊的設計與應用

基于半雙工機制實現3線制雙向SPI模塊的設計與應用

評論