學(xué)習(xí)內(nèi)容

本文首先介紹Flash和QSPI Flash控制器的相關(guān)內(nèi)容,然后使用 QSPI Flash 控制器,開(kāi)發(fā)板上的 QSPI Flash 進(jìn)行寫、 讀操作。通過(guò)對(duì)比讀出的數(shù)據(jù)是否等于寫入的數(shù)據(jù), 從而驗(yàn)證讀寫操作是否正確。

開(kāi)發(fā)環(huán)境

vivado 18.3&SDK,PYNQ-Z2開(kāi)發(fā)板。

Flash簡(jiǎn)介

Flash存儲(chǔ)器,又叫做閃存,是一種非易失性存儲(chǔ)器。具有操作方便讀寫速度快等優(yōu)點(diǎn)。一般用于存儲(chǔ)操作系統(tǒng)和程序代碼,或者用于數(shù)據(jù)存儲(chǔ)。Flash的存儲(chǔ)單元組織為塊陣列,塊是擦除操作的最小單位,擦除操作將塊內(nèi)的所有為置位為1,頁(yè)是讀寫操作的基本單位。

在對(duì)頁(yè)進(jìn)行寫操作前,要判斷該頁(yè)內(nèi)所有位是否為1。如果全部為1可以寫操作,否則要對(duì)整塊進(jìn)行擦除操作(Flash只能從1反轉(zhuǎn)到0)。Flash在內(nèi)部結(jié)構(gòu)(接口)上主要分為Nor flash 和NAND flash。

Nor Flash :寫入和擦除的速度低;結(jié)構(gòu)復(fù)雜,成本高;存儲(chǔ)容量較小;一般用于存儲(chǔ)Bootloader以及操作系統(tǒng)或者程序代碼,可以在芯片內(nèi)部直接運(yùn)行代碼。NAND Flash :寫入和擦除的速度較快;結(jié)構(gòu)簡(jiǎn)單,成本低;存儲(chǔ)容量較大;一般用于存儲(chǔ)材料和數(shù)據(jù)。

Flash在外部接口上主要分為CFI flash 和SPI(STD/Dual/Quad) flash。CFI flash 讀寫速度快,需要的硬件引腳多且不同容量的硬件不兼容;而SPI(STD/Dual/Quad) flash讀寫速度慢,需要的硬件引腳少且不同容量的硬件兼容。

QSPI Flash簡(jiǎn)介

介紹

Quad-SPI閃存控制器是位于PS內(nèi)的輸入/輸出外設(shè)(IOP)的一部分。它用于訪問(wèn)多位串行閃存設(shè)備,以實(shí)現(xiàn)高吞吐量和低引腳數(shù)應(yīng)用。

控制器可以以三種模式運(yùn)行:I / O模式,線性尋址模式和傳統(tǒng)SPI模式。

在I / O模式下,軟件與閃存設(shè)備協(xié)議緊密交互,所以在該模式下需要對(duì)協(xié)議進(jìn)行詳細(xì)了解。軟件通過(guò)使用四個(gè)TXD寄存器將閃存命令和數(shù)據(jù)寫入控制器。軟件通過(guò)讀取RXD寄存器。

線性尋址模式使用設(shè)備操作的子集來(lái)消除I / O模式讀取閃存所需的軟件開(kāi)銷。也就是說(shuō)線性尋址模式比IO模式要快的多。線性模式采用硬件來(lái)向閃存發(fā)出命令,并控制從flash到AXI接口的數(shù)據(jù)。控制器響應(yīng)AXI接口上的存儲(chǔ)器請(qǐng)求,就好像閃存是ROM存儲(chǔ)器。

在傳統(tǒng)模式下,QSPI控制器充當(dāng)普通的SPI控制器。

控制器可以與一或兩個(gè)閃存設(shè)備接口。可以并行連接兩個(gè)設(shè)備以實(shí)現(xiàn)8位性能,也可以以堆疊的4位布局連接以最大程度地減少引腳數(shù)。

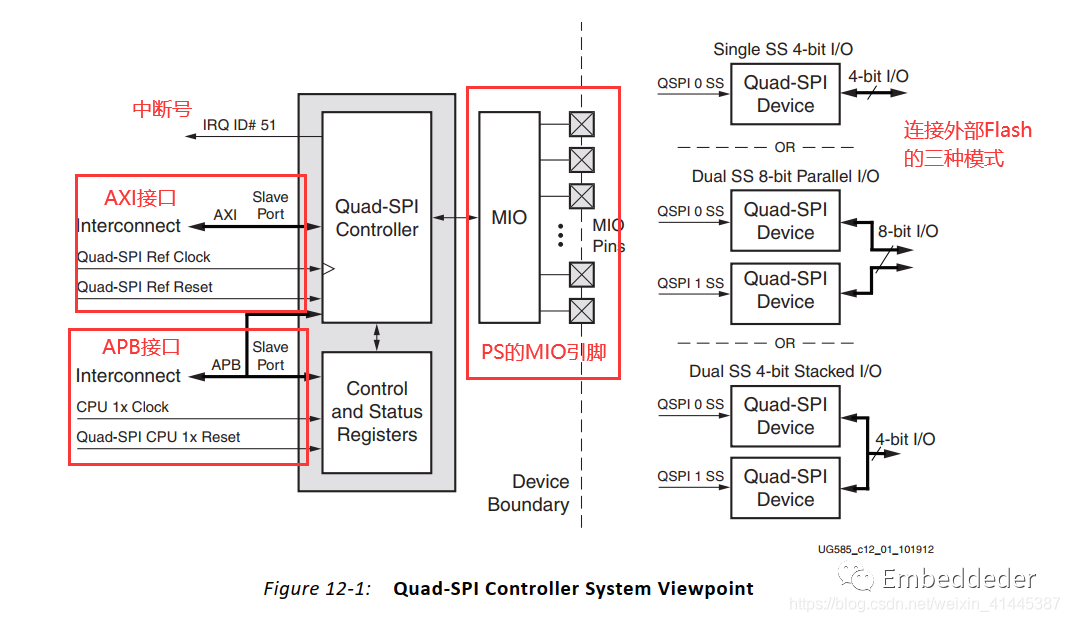

系統(tǒng)框圖

QSPI Flash 控制器的系統(tǒng)框圖如下所示:

從上圖中可知, QSPI Flash 控制器通過(guò) MIO 與外部 Flash 器件連接,支持三種模式:?jiǎn)蝹€(gè)從器件模式、雙從器件并行模式和雙從器件堆疊模式。雙從器件并行模式把每個(gè)flash的IO進(jìn)行單獨(dú)連接,擴(kuò)展成8位用于控制對(duì)不同flash的訪問(wèn)。而雙從器件堆疊模式,使用SS片選信號(hào)進(jìn)行區(qū)分flash的使能,所以想擴(kuò)展 QSPI Flash 的存儲(chǔ)容量,可以使用雙從器件并行模式。

當(dāng)使用單個(gè)設(shè)備時(shí),直接存儲(chǔ)器讀取的地址映射從FC00_0000開(kāi)始,最大為FCFF_FFFF(16 MB)。兩臺(tái)設(shè)備系統(tǒng)的地址映射取決于存儲(chǔ)設(shè)備和I / O配置。

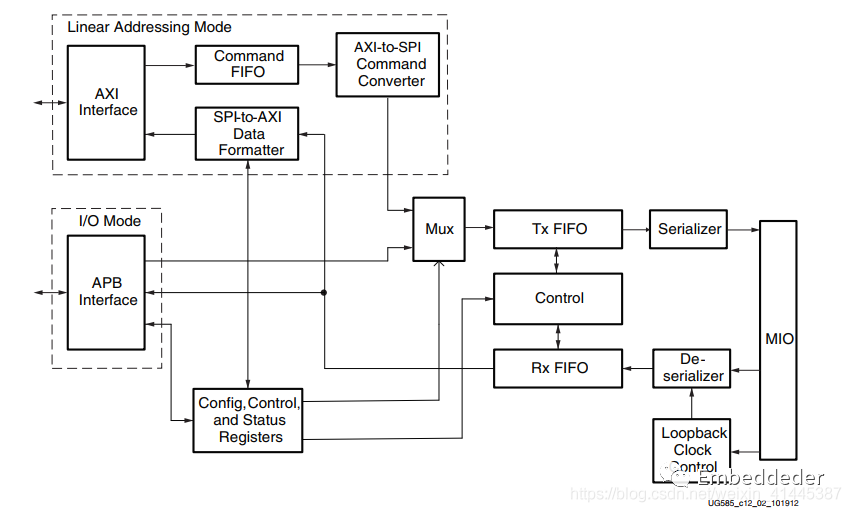

QSPI Flash 控制器內(nèi)部框圖

由上圖可知,在線性地址模式下,使用的是AXI的接口進(jìn)行數(shù)據(jù)交互的,首先由AXI總線讀取到響應(yīng)的指令,并存到Command FIFO,然后使用AXI to SPI的命令轉(zhuǎn)化器傳輸?shù)竭x擇器。在IO模式下,使用的是APB接口直接把接收到的信號(hào)傳輸給選擇器進(jìn)行選擇。

然后選擇器進(jìn)行功能選擇后傳輸?shù)絋xFIFO,接著把Tx FIFO的數(shù)據(jù)進(jìn)行串行化,然后通過(guò)MIO引腳發(fā)送。接收部分原理相反,而且可以看出在線性地址模式下,接收信號(hào)的轉(zhuǎn)換使用的是數(shù)據(jù)轉(zhuǎn)換器。所以在線性地址模式下,只支持讀取數(shù)據(jù),不支持發(fā)送數(shù)據(jù)。

流程控制

在數(shù)據(jù)傳輸期間,I / O模式具有不同的流控制模式。用戶可以在自動(dòng)和手動(dòng)模式之間進(jìn)行選擇,該模式由config_reg.MANSTARTEN(Man_start_com)控制。在自動(dòng)模式下,包括芯片選擇控制在內(nèi)的整個(gè)傳輸過(guò)程都在硬件中完成。

無(wú)需軟件干預(yù)。在手動(dòng)模式下,用戶控制數(shù)據(jù)傳輸?shù)拈_(kāi)始。在這種情況下,軟件要么將整個(gè)傳輸序列寫入TxFIFO,要么直到TxFIFO已滿。在手動(dòng)模式下,用戶除了控制傳輸開(kāi)始之外,還可以選擇控制芯片選擇。從命令開(kāi)始,軟件再次將傳輸序列寫入TxFIFO,直到TxFIFO已滿。然后,軟件拉高CS,然后手動(dòng)啟動(dòng)進(jìn)行硬件管理。

編程指南

在xilinx給出的UG585指導(dǎo)手冊(cè)中,對(duì)QSPI Flash 控制器編程設(shè)計(jì)進(jìn)行了指導(dǎo)開(kāi)發(fā),用戶可以根據(jù)自己的設(shè)計(jì)需要參考指導(dǎo)手冊(cè)中的編程順序?qū)崿F(xiàn)自己的應(yīng)用功能。

啟動(dòng)順序

配置時(shí)鐘。

配置發(fā)送/接收信號(hào)。(以上兩步在vivado底層搭建中已經(jīng)完成設(shè)計(jì))

配置控制器

該步驟適用于線性尋址和I / O模式。它配置了控制器的波特率,F(xiàn)IFO,flash模式,時(shí)鐘相位/極性和對(duì)環(huán)回延遲進(jìn)行編程。

配置控制器。寫入qspi.Config_reg寄存器。a. 設(shè)置波特率[BAUD_RATE_DIV]。b. 選擇主模式,[MODE_SEL] = 1。C. 選擇flash模式(不是傳統(tǒng)SPI),[LEG_FLSH] = 1。d. 選擇Little Endian,[endian] = 0。e. 將FIFO寬度設(shè)置為32位[FIFO_WIDTH]。F. 設(shè)置時(shí)鐘相位[CLK_PH]和極性[CLK_POL]。

啟用回送時(shí)鐘。如果使用回送時(shí)鐘,確保將qspi.Config_reg [BAUD_RATE_DIV]設(shè)置為0b00,并使用以下設(shè)置配置qspi.LPBK_DLY_ADJ(回送延遲調(diào)整)寄存器:a. 設(shè)置為選擇內(nèi)部時(shí)鐘。qspi.LPBK_DLY_ADJ [USE_LPBK] = 1。b. 將時(shí)鐘延遲設(shè)置為0。qspi.LPBK_DLY_ADJ [DLY0] = 0b00。c. 設(shè)置時(shí)鐘延遲1. qspi.LPBK_DLY_ADJ [DLY1] = 0b00。

線性尋址模式

線性尋址模式下數(shù)據(jù)讀取(存儲(chǔ)器讀取)的操作順序如下:

將手動(dòng)啟動(dòng)啟用設(shè)置為自動(dòng)模式。設(shè)置qspi.Config_reg [Man_start_en] = 0。

使能片選信號(hào)。設(shè)置qspi.Config_reg [PCS] = 0。

將配置寄存器編程為線性尋址模式。

啟用控制器。設(shè)置qspi.En_REG [SPI_EN] = 1。

從線性地址存儲(chǔ)區(qū)讀取數(shù)據(jù)。內(nèi)存范圍取決于大小和設(shè)備數(shù)量。范圍是從0xFC00_0000到0xFDFF_FFFF。

禁用控制器。設(shè)置qspi.En_REG [SPI_EN] = 0。

取消使能片選信號(hào)。設(shè)置qspi.Config_reg [PCS] = 1。

配置I / O模式

使用I / O模式進(jìn)行讀取和寫入編程步驟如下:

啟用手動(dòng)模式。qspi.Config_reg [Man_start_en,Manual_CS] = 1。

配置flash設(shè)備。對(duì)單個(gè)閃存設(shè)備使用qspi.LQSPI_CFG寄存器的重置值。如果是并行雙閃存設(shè)備,則將1寫入TWO_MEM,SEP_BUS位字段。

使能片選。設(shè)置qspi.Config_reg [PCS] = 0。

啟用控制器。設(shè)置qspi.En_REG [SPI_EN] = 1。

將字節(jié)序列寫入閃存。使用TXD從1到4字節(jié)寫入TxFIFO寄存器。

避免TxFIFO溢出。當(dāng)TxFIFO為空時(shí),可以寫入252個(gè)字節(jié)。此后,軟件可以通過(guò)讀取qspi.Intr_status_REG [TX_FIFO_full]并等待直到它等于0之后再寫入TXD寄存器,來(lái)避免TxFIFO溢出。

啟用中斷。寫入qspi.Intrpt_en_REG。

開(kāi)始數(shù)據(jù)傳輸。設(shè)置qspi.Config_reg [Man_start_com] = 1。

中斷處理程序:在編程/讀取操作期間,將所有需要的數(shù)據(jù)傳輸?shù)絈SPI flash,并傳輸?shù)絈uad-SPI flash。

如果執(zhí)行了讀取操作:重新排列READ數(shù)據(jù)以消除由于空循環(huán)而讀取的數(shù)據(jù)。

取消使能片選信號(hào)。設(shè)置QSPI.Config_reg [PCS] = 1。

禁用控制器。設(shè)置qspi.En_REG [SPI_EN] = 0。

I/O模式中斷服務(wù)程序

配置ISR以根據(jù)Quad-SPI器件類型處理中斷條件。要從Quad-SPI器件讀取數(shù)據(jù),最簡(jiǎn)單的ISR從RxFIFO讀取數(shù)據(jù)并將內(nèi)容寫入TxFIFO。控制器生成系統(tǒng)外設(shè)中斷(SPI),IRQ ID#51。對(duì)以下兩種情況進(jìn)行觸發(fā)中斷。a. 讀取傳輸中斷。RxFIFO不為空中斷b. 寫傳輸中斷。TxFIFO未完全中斷

I/O模式中斷

中斷僅在I / O模式下使用。只要滿足任何中斷條件,控制器中斷就被置為有效。Quad-SPI中斷處理程序檢查中斷原因。單個(gè)中斷服務(wù)程序可以管理所有中斷條件。

Rx和Tx的中斷處理程序

中斷處理程序由IRQ ID#51觸發(fā)。示例讀取RxFIFO直到其為空,然后填充TxFIFO。RxFIFO非空中斷狀態(tài)用于確定是否可以從RxFIFO讀取內(nèi)容。TxFIFO未滿中斷指示TxFIFO中是否有空間容納更多內(nèi)容。

禁用控制器中的所有中斷。將qspi.Intrpt_dis_REG [TX_FIFO_not_full,RX_FIFO_full]都設(shè)置為1。

清除中斷。將1s寫入中斷狀態(tài)寄存器qspi.Intr_status_REG。

清空RxFIFO。檢查是否聲明了RxFIFO非空中斷。如果qspi.Intr_status_REG [RX_FIFO_not_empty] = 1,則RxFIFO中有數(shù)據(jù)。a. 如果狀態(tài)為有效,則從RxFIFO讀取數(shù)據(jù)。使用qspi.RX_data_REG寄存器讀取數(shù)據(jù)。b. 從RxFIFO讀取數(shù)據(jù)并輪詢中斷狀態(tài),直到RxFIFO為空。當(dāng)qspi.Intr_status_REG [RX_FIFO_not_empty] = 0時(shí),RxFIFO為空。

填充TxFIFO。檢查TxFIFO未滿狀態(tài)是否有效。如果 qspi.Intr_status_REG [TX_FIFO_not_Full] = 1,則存在要發(fā)送到閃存設(shè)備的數(shù)據(jù)(編程和/或讀取操作):a. 將數(shù)據(jù)寫入qspi.TXD0寄存器。b. 輪詢qspi.Intr_status_REG [TX_FIFO_full] = 1,這表明TX FIFO已滿。c. 遵循步驟a和b,直到將所有數(shù)據(jù)寫入TxFIFO或直到qspi.Intr_status_REG[TX_FIFO_full] = 1。

啟用中斷。將qspi.Intrpt_en_REG [TX_FIFO_not_full,RX_FIFO_full]都設(shè)置為1。

開(kāi)始數(shù)據(jù)傳輸。設(shè)置qspi.Config_reg [MANSTRTEN] = 1。

在本次工程設(shè)計(jì)中,使用QSPI Flash控制器對(duì)ZYNQ的QSPI Flash進(jìn)行讀寫操作。通過(guò)對(duì)比讀取數(shù)據(jù)和寫入數(shù)據(jù)是否相等驗(yàn)證讀寫功能是否正常。

硬件平臺(tái)搭建

新建工程,創(chuàng)建 Block Design。添加ZYNQ7 ip,根據(jù)本次工程需要對(duì)IP進(jìn)行配置。勾選本次工程使用的資源。完成對(duì)所用資源的勾選,在clock configuration這里可以查看對(duì)QSPI的時(shí)鐘配置。這里不需要對(duì)其他資源進(jìn)行配置,所以可以使用默認(rèn)配置。然后我們進(jìn)行g(shù)enerate output product 然后生成HDL封裝。這里用到了僅僅用到了PS部分的資源,所以不需要進(jìn)行管腳分配。點(diǎn)擊導(dǎo)出硬件資源(不用包含bit流文件),接著launch SDK,進(jìn)入軟件部分編寫。

SDK軟件部分

打開(kāi)SDK后,新建application project。在system.mss中可以打開(kāi)相關(guān)參考文檔輔助設(shè)計(jì)。可以選擇qspi的例程進(jìn)行參考設(shè)計(jì),導(dǎo)入例程模板,根據(jù)提供的模板,主要使用的函數(shù)如下,這里對(duì)他的讀寫測(cè)試進(jìn)行了簡(jiǎn)化,

int QspiFlashPolledExample(XQspiPs *QspiInstancePtr, u16 QspiDeviceId)

{

int Status;

u8 *BufferPtr;

u8 UniqueValue;

int Count;

int Page;

XQspiPs_Config *QspiConfig;

//初始化QSPI

QspiConfig = XQspiPs_LookupConfig(QspiDeviceId);

XQspiPs_CfgInitialize(QspiInstancePtr, QspiConfig,QspiConfig-》BaseAddress);

//自測(cè)

Status = XQspiPs_SelfTest(QspiInstancePtr);

if (Status != XST_SUCCESS) {

return XST_FAILURE;

}

//初始化讀寫B(tài)UFFERfor (UniqueValue = UNIQUE_VALUE, Count = 0; Count 《 PAGE_SIZE;

Count++, UniqueValue++) {

WriteBuffer[DATA_OFFSET + Count] = (u8)(UniqueValue + Test);

}

memset(ReadBuffer, 0x00, sizeof(ReadBuffer));

//設(shè)置手動(dòng)啟動(dòng)和手動(dòng)片選模式

XQspiPs_SetOptions(QspiInstancePtr, XQSPIPS_MANUAL_START_OPTION |

XQSPIPS_FORCE_SSELECT_OPTION |

XQSPIPS_HOLD_B_DRIVE_OPTION);

//設(shè)置QSPI時(shí)鐘的分頻系數(shù)

XQspiPs_SetClkPrescaler(QspiInstancePtr, XQSPIPS_CLK_PRESCALE_8);

//片選信號(hào)置為有效

XQspiPs_SetSlaveSelect(QspiInstancePtr);

//讀FLASH ID

FlashReadID();

//使能FLASH Quad模式

FlashQuadEnable(QspiInstancePtr);

//擦除FLASH

FlashErase(QspiInstancePtr, TEST_ADDRESS, MAX_DATA);

//向FLASH中寫入數(shù)據(jù)for (Page = 0; Page 《 PAGE_COUNT; Page++) {

FlashWrite(QspiInstancePtr, (Page * PAGE_SIZE) + TEST_ADDRESS,

PAGE_SIZE, WRITE_CMD);

}

//使用QUAD模式從FLASH中讀出數(shù)據(jù)

FlashRead(QspiInstancePtr, TEST_ADDRESS, MAX_DATA, READ_CMD);

//對(duì)比寫入FLASH與從FLASH中讀出的數(shù)據(jù)

BufferPtr = &ReadBuffer[DATA_OFFSET];

for (UniqueValue = UNIQUE_VALUE, Count = 0; Count 《 MAX_DATA;

Count++, UniqueValue++) {

if (BufferPtr[Count] != (u8)(UniqueValue + Test)) {

return XST_FAILURE;

}

}

return XST_SUCCESS;

}

運(yùn)行效果

References

ZYNQ正點(diǎn)原子開(kāi)發(fā)視頻

UG585

編輯:jq

-

控制器

+關(guān)注

關(guān)注

112文章

15886瀏覽量

175386 -

FlaSh

+關(guān)注

關(guān)注

10文章

1598瀏覽量

147339 -

STD

+關(guān)注

關(guān)注

0文章

36瀏覽量

14314 -

開(kāi)發(fā)板

+關(guān)注

關(guān)注

25文章

4771瀏覽量

96182

原文標(biāo)題:ZYNQ-QSPI Flash讀寫操作

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

在mmWave SDK增加QSPI Flash驅(qū)動(dòng)的示例

STM32F746 QSPI的Flash擴(kuò)展后,添加到工程下載發(fā)現(xiàn)報(bào)錯(cuò),為什么?

STM32 QSPI怎么退出映射模式?

STM32WB55RGV6使用QSPI官方例程讀寫外部FLASH,讀出的數(shù)據(jù)跟寫入的數(shù)據(jù)不相同是為什么?

STM32H750 QSPI flash重映射模式下有方法能實(shí)現(xiàn)讀寫操作嗎?

ctt4bf上的qspi最大讀、寫速度是多少?

stm32 flash寫數(shù)據(jù)怎么存儲(chǔ)的

在軟件SDK中選擇不同的下載模式時(shí),是哪個(gè)部件更改了QSPI0中寄存器的值?

對(duì)控制flash讀寫的模塊做了相關(guān)修改,用NucleiStudio燒寫程序出現(xiàn)Debug interrupt didn\'t clear.的原因?

使用 PCIE 更新 AMD ZYNQ? 的 QSPI Flash 參考設(shè)計(jì)

使用PCIE更新AMD ZYNQ的QSPI Flash參考設(shè)計(jì)

STM32的Flash寫了保護(hù)怎么辦?STM32如何設(shè)置讀保護(hù)和解除讀保護(hù)?

mm32-2nd-bootloader技術(shù)白皮書(5)——編譯可在QSPI Flash上運(yùn)行的程序

QSPI硬件實(shí)現(xiàn)驅(qū)動(dòng)功能原理解析

QSPI Flash驅(qū)動(dòng)功能解析和使用注意事項(xiàng)

如何使用QSPI Flash控制器開(kāi)發(fā)板上的 QSPI Flash進(jìn)行寫讀操作

如何使用QSPI Flash控制器開(kāi)發(fā)板上的 QSPI Flash進(jìn)行寫讀操作

評(píng)論