作者:王仁發;林秩盛;陸南昌;熊燕

數字調諧系統是現代收發信機的核心,其性能直接影響通信質量的好壞,其主要部分是集成鎖相式頻率合成器。集成鎖相環與微處理器結合,可由微機控制完成頻率合成器的全部功能。

本文實現了一種與常規雙環方案完全不同的新雙環方案。該方案使用較高的鑒相頻率,采用直接數字合成(DDS)芯片,通過改變DDS的時鐘頻率和頻率控制字,使參考鑒相頻率產生較小的變化,就能改變環路的輸出頻率,達到精確頻率合成的目的。該方案既解決了小頻道間隔與高頻譜純度間的矛盾,又具有高的轉換速度;由單片微機完成計算和控制。

1 新方案原理

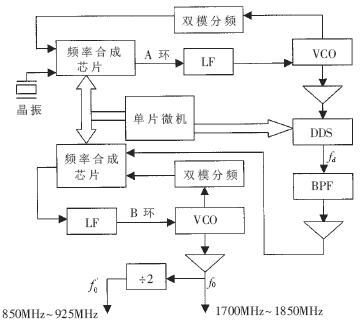

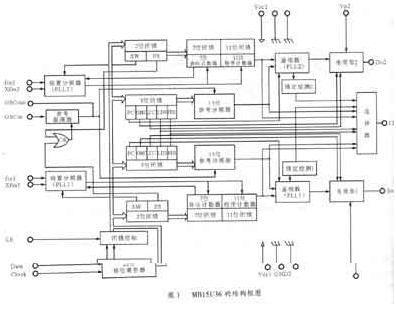

系統簡化原理圖如圖1所示。其中B環使調諧器輸出頻率f0作較大變化,A環為DDS芯片提供時鐘頻率fc,只要改變A環總分頻比NA和DDS的頻率控制字,使DDS輸出頻率fd作小變動,便可使f0以較小間隔頻率作步進改變。

圖1 方案原理圖

設A、B環中鑒相頻率分別為100kHz和300kHz(由晶振與fd分別經參考分頻器得到),雙模分頻與頻率合成芯片中的程序分頻的總分頻比分別為NA和NB, f0=1700MHz“1850MHz, f′0=850MHz”925MHz, △f0=25kHz,則由環路鎖定時的頻率關系得到△fd=4.16Hz~4.41Hz;所以只要△fd≤4.41Hz,便可使輸出的頻率分辨率達到25kHz。一般DDS的輸出頻率間隔做到小于0.1Hz,即可滿足本要求。同理,當△f0=±150kHz時(NB每改變1,f0變化300kHz),△fd=±(25~26.47)Hz, 只要fd最大改變量為±26.47Hz,便可使△f0覆蓋300kHz。上述表明采用DDS后,完全可使兩環路使用高的鑒相頻率,可大大提高頻率轉換速率。

上述方案中采用的DDS是一種取樣系統,且存在相位舍位誤差、幅度量化誤差、DAC的非線性引起的誤差等,故其輸出為復合信號頻譜,包含DDS輸出頻率fd、時鐘頻率fc及其各次諧波、各種組合頻率以及其它虛假信號。根據文獻的推導,實際DDS的輸出頻率ω為:

B為從相位累加器N中舍去的低位數,K為頻率控制字;mωp為相位舍位產生的雜散,nωc為時鐘的各次諧波,lωd為輸出的各次諧波。

其中,fc-fd雜散分量的幅度最大,即輸出信號的雜散抑制度決定于該fc-fd的幅度和LPF的帶外抑制度。如果fd與fc-fd之間的頻率間隔越大,則主頻與雜波之間的幅度差就越大,這樣就可減小雜波對DDS的影響。一般的晶振頻率都不是很高,但是利用鎖相環(A環)就可以得到想要的頻率,以增加主頻和雜波之間的頻率間隔。

另外,在式(1)中,第一項由相位舍位引起,該雜散可以通過選取適當的時鐘頻率和頻率控制字以減小其影響。由式(2)可以看出,當K-int(K/2B)·2B=0,ωp=0,此時相位舍位不會使DDS的輸出頻譜產生雜散。因此可以利用鎖相環(A環)為DDS提供時鐘信號。由于A環是鎖相環,因此DDS的時鐘頻率是可變的,可以通過調整DDS的時鐘來抑止其雜散,也可通過改變它來改變DDS輸出頻率, 從而改變整個輸出頻率。通過軟件編程還可以實現跳頻的功能。

2 電路的實現

整個電路分為A環、DDS單元、B環、二分頻單元、單片機控制單元共五個部分。

2.1 DDS電路的設計

DDS選用AD公司的AD9850。其頻率控制字K由N位的二進制數組成,輸出頻率由頻率控制字決定:

根據取樣定律,DDS的最高輸出頻率應小于fc/2,實際應用中一般只能達到0.4fc。

DDS的時鐘選用A環的輸出,頻率范圍是80MHz“100MHz。而DDS的最高時鐘是120MHz,因此滿足時鐘要求。DDS輸出頻率范圍是15MHz”19MHz,中心頻率為17MHz,頻率改變范圍可以小于0.02Hz,完全滿足輸出頻率間隔為25kHz的信號要求。帶通濾波器用來抑止DDS輸出的雜散和噪聲。

2.2 A環

主要由集成芯片MC145170外加環路濾波器(LF)、壓控振蕩器(VCO)、溫補晶振(TXCO)以及放大器組成。

(1) 鎖相環芯片MC145170

該芯片主要包含可編程÷R、÷N分頻器,8位程序控制C寄存器,單端鑒相器PDA和雙端鑒相器PDB以及鎖定指示器LD。通過選擇不同的外接參考源或改變參考分頻比R便可得到不同的基準參考頻率fr;改變程序分頻比N的值可得到fv;C寄存器用來控制整個芯片的工作;鎖定檢測器LD用來檢測并指示環路是否鎖定。單端鑒相器PDA為三態單端輸出,當fv>fr或fv相位超前時,輸出負脈沖;相反,則輸出正脈沖;當fv=fr且同相位時,輸出呈高阻狀態。雙端鑒相器PDB為雙端輸出,可在外部形成環路誤差信號。當fv=fr或fv相位超前時,ΦV 輸出負脈沖;相反,則ΦR輸出負脈沖;當fv=fr且同相位時,兩者除了有一極短暫、同相位的負脈沖外,均保持高電平。

(2) 壓控振蕩器VCO

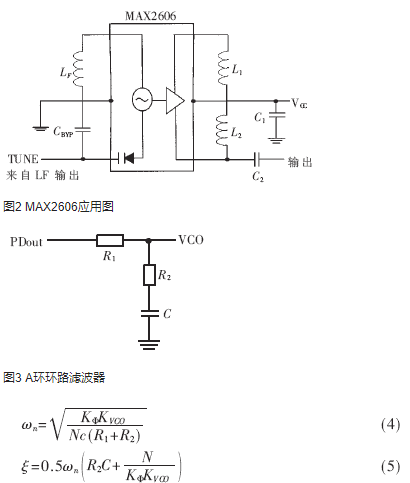

VCO選用MAX2606,電路如圖2所示。它是一種微型、高性能的中頻壓控振蕩器。頻率范圍是70MHz“150MHz,只需用少量的外圍器件。最需注意的是外接電感LF的選擇,該電感用來調整VCO輸出頻率。筆者選用電感LF=454nH來獲得80MHz”100MHz的頻率輸出。當改變該電感時,輸出頻率范圍也會變化。另外,輸出端連接的電容C2的選擇也很重要。如果C2太大,就不能與MAX2606的內部電路匹配,導致整個環路不能工作。

(3) A環環路濾波器LF

環路采用MC145170中的鑒相器PDA,在其輸出端PDOUT外接環路濾波器。環路濾波器采用無源比例積分濾波器,如圖3所示。濾波器的參數由式(4)和式(5)決定。

其中,ωn為環路等效自然頻率,ξ為等效阻尼系數,KΦ為鑒相器的鑒相靈敏度,KVCO為VCO的壓控靈敏度,N為反饋環路總分頻比。在一般情況下,ξ取0.707~1,ωn取由上述公式可計算出各參數。

(4) A環輸出放大器

選用集成芯片MAX2611。MAX2611是一種低噪聲放大器,具有高驅動能力,頻率范圍是DC到1100MHz,在500MHz時增益為18dB。

2.3 B環

主要由集成芯片MC145201外加環路濾波器、壓控振蕩器和放大器組成;其中MC145201與MC145170類似。

(1) B環環路濾波器LF

采用MC145201的單端輸出,環路濾波器由R、C組成,結構與參數可參照A環環路濾波器的設計。

(2) B環放大器

采用MAX2473芯片,它是一種寬帶、高反向隔離緩沖放大器。利用它隔離負載對VCO的影響,同時提高VCO輸出信號的功率以便驅動二分頻器。

(3) B環最終的輸出頻率范圍1700MHz“1850MHz

2.4 二分頻器

采用有源二分頻器芯片(MF220),對B環的輸出頻率進行二分頻后獲得850MHz~925MHz頻率。

3 實驗結果

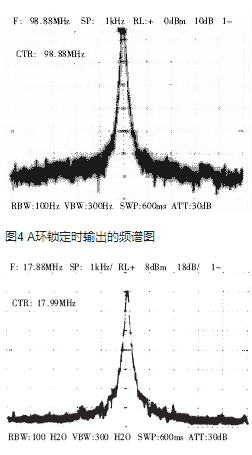

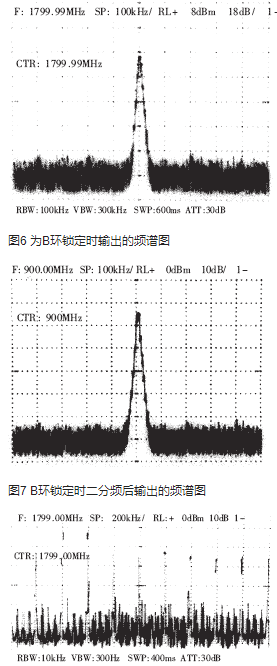

(1) 實驗圖片(注:1kHz的分辨率是該頻譜分析儀的最高分辨率)如圖4~圖7所示。

可見,環路鎖定后可獲得優良的輸出頻譜和良好的輸出波形。

(2) 頻穩度測量結果如表1。

一般鎖相理論分析的結論是:環路鎖定時,環路輸出的頻穩度與基準源的頻穩度為同一數量級。可見,實際測量結果與理論分析相吻

系統單元

頻穩度(30min時間段)

晶振

1.67×10-7

A環輸出

1.03×10-7

DDS輸出

1.18×10-7

B環輸出

1.37×10-7

二分頻輸出

1.11×10-7

表 1 頻穩度測量結果

圖5 A環作為時鐘時DDS輸出的頻譜圖

圖8 200跳/s頻譜圖

4 跳頻輸出效果

跳頻系統的兩個主要指標是跳頻帶寬和跳頻速率。一般來說,希望跳頻帶寬要寬,跳頻的頻率數目要多,跳頻的速率要快。該系統的跳頻速度至少可達5000跳/s。圖8為200跳/s時的圖片,由于儀器設備的限制,不能拍下更高的跳頻速度的圖片。但是可通過監測鑒相器的鎖定指示信號來判斷在高速跳頻時是否失鎖。

本系統的方案在很大程度上解決了鎖相環中鑒相頻率、頻率間隔和頻譜純度之間的矛盾,實現了頻率的快速跳變和小的步進,而且具有較高的頻率輸出。從上述實驗圖片和數據可以看出,該新型的DDS+雙鎖相環頻率合成器組成的數字調諧系統具有優良的性能。

責任編輯:gt

-

頻率合成器

+關注

關注

5文章

218瀏覽量

32331 -

DDS

+關注

關注

21文章

631瀏覽量

152539 -

調諧器

+關注

關注

0文章

180瀏覽量

29642

發布評論請先 登錄

相關推薦

基于DDS和雙鎖相環頻率合成器實現雙環數字調諧系統的設計

基于DDS和雙鎖相環頻率合成器實現雙環數字調諧系統的設計

評論