大家好,今天來聊聊RS-485總線。RS-485也是應用非常廣泛的一種通信接口,本文來討論一下要點,文章稍微有點長,約5000字。

前世今生

RS-485,RS是什么意思呢?是Recommended Standard的縮寫,就是推薦標準的意思。485是標準標識號,至于為什么定這個標識號,則無需深究。RS-485又稱為ANSI/TIA/EIA-485,這幾個前綴是標準協會的名稱縮寫,比如EIA就是電子工業協會 (Electronics Industries Association EIA)的縮寫。1983年,RS-485通訊接口被電子工業協會 (Electronics Industries Association EIA)批準為一種通訊接口標準。 即便在現在IOT火熱的今天,RS-485仍然有大量的應用。很多協議使用RS-485作為物理層,比如常用標準協議使用RS-485作為物理層的有哪些呢?比如:

工業HART總線

modbus協議

Profibus DP

.......

電氣特性

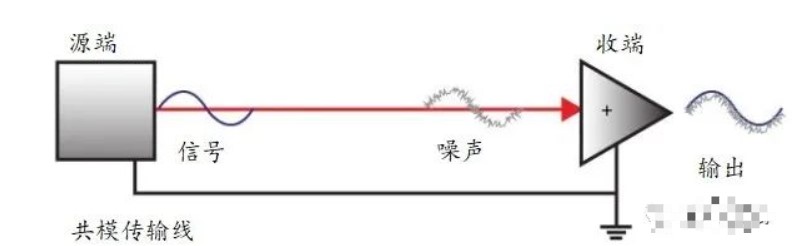

信號采樣差模傳輸,差模是相對于共模而言的,差模也稱為差分,那么什么樣的傳輸是差模呢?一圖勝千言,看下面兩個圖就明白了:

共模傳輸

采用共模傳輸方式時,共模噪聲將會疊加在最終的輸出信號上面,污染了原始的信號。

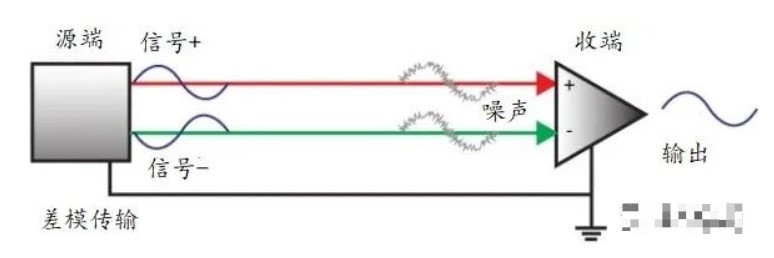

差模傳輸

而采用差模傳輸方式,則源端發出的信號+與信號-相位是相反的,而對于共模噪聲而言在+/-兩條線上都會存在,理想情況是等幅同相的,而接收端,相當于一個減法器,有用信號由于相位相反則經過減法器仍然保留,而噪聲則會被抵消。而實際電路中,則會大幅度削弱。 由此可見,差模傳輸相對于共模傳輸方式,優勢在于差模方式可以有效抵消共模干擾。 差模方式在有的地方又稱為平衡模式,而共模模式也稱為非平衡模式。 對于這個干擾,我們來實際抓個波形看看:

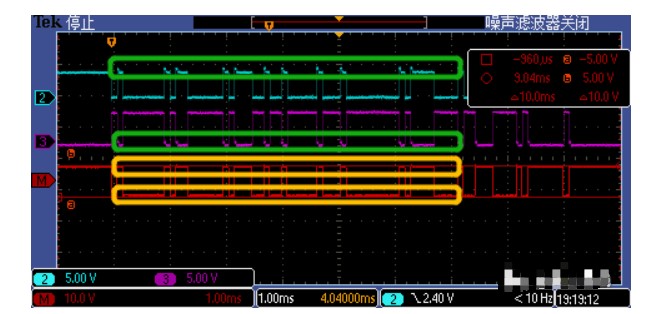

在A/B信號的邊緣處,波形都略微有些變形,但是你看A-B做差(紅色的為示波器的MATH減功能,為A-B),邊沿則變得非常的干凈!這例子就可以很好地說明差模傳輸可以有效的抵抗共模干擾。

電氣參數

RS-485的電氣參數為:

共模電壓范圍為-7~+12V

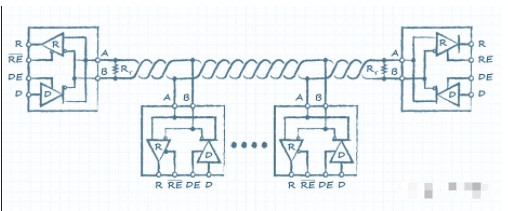

可支持32個多點拓撲連接,見下面的網絡拓撲圖

使用40英尺線纜時,傳輸速率可達10Mbps,1英尺相當于30.48cm,這里Mbps是兆bit/s的意思

使用4000英尺線纜時,傳輸速率可達到100kbps

半雙工通信

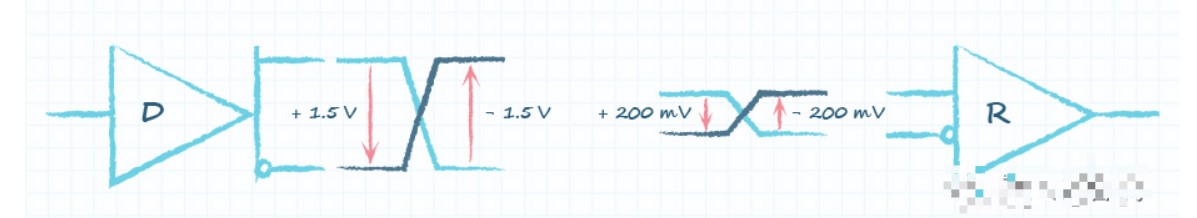

最小差分電壓容限:200mV,也就是說接收端在差分電壓低于200mV時就無法正確識別0/1了。這句話應該怎么理解呢?

上面這個圖怎么理解呢?RS-485收發器的發送電路至少提供1.5V差分電壓輸出能力,經由總線線路阻抗衰減,32個接收電路輸入阻抗,以及120?端接電阻,差分信號的幅度必然逐漸衰減,那么至最末端還需要至少提供200mV的差分電壓給末端接收電路。

:對于接收電路是判決A線共模電壓與B線共模電壓之差:

如果,則接收電路R識別為邏輯 1

如果,則接收電路R識別為邏輯0

簡單說就是,A線的絕對電壓值比B線的至少大于200mV則識別為邏輯1,或者A線的絕對電壓值比B線的至少小200mV,才識別為邏輯0

這里的參數,應該是在一定特征阻抗線纜時的理論值,實際工程使用的時候需要做相應的調整以及現場測試。一般以不超出這個理論極限為好。 說到電氣特性參數,首先來看看一般的接口電路:

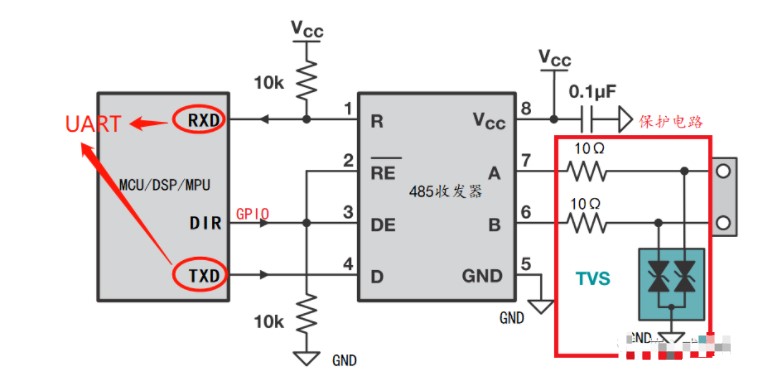

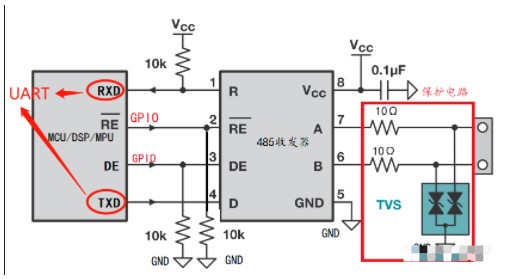

從這樣一個接口電路來看,有這么些要點:

RS-485通信從單片機/DSP/處理器接口而言,是利用UART接口與RS-485收發器接口。當然你說我用FPGA難道不行么?肯定是可以的,用FPGA實現一個串口收發的IP模塊,當然也是可以的。甚至你想說,我拿GPIO去模擬一下 UART 是不是就不行?也是能辦得到的,只不過這么干意義不大,需要占用CPU資源實現底層BIT的收發。

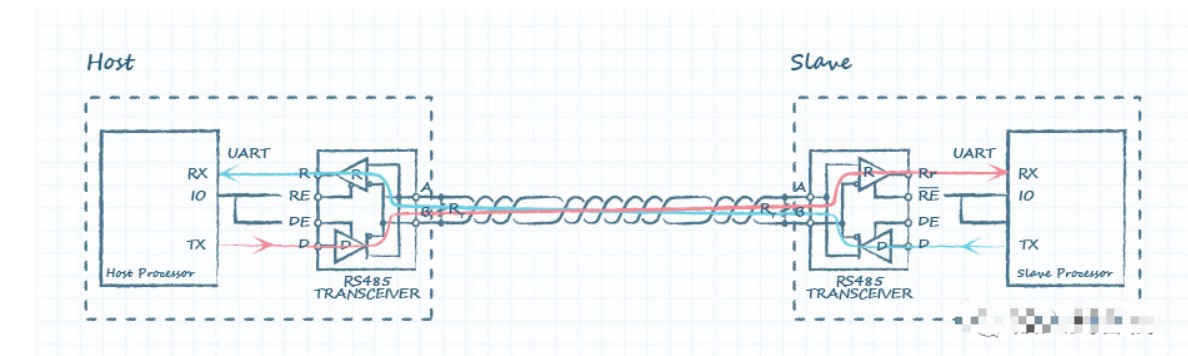

前面說到半雙工,有半雙工就有全雙工。什么是半雙工呢?首先半雙工以及全雙工,所界定的對象一定是點對點而言的,這里說點對點就是指在同一時刻而言,所謂半雙工,就是設備在同一時刻要么處于收數據狀態, 要么處于發數據狀態, 不允許同時收發數據。 全雙工則剛好相反,允許同時收發。比如 I2C 總線就是半雙工總線,4線制 SPI 是全雙工,而三線制SPI則是半雙工總線;又譬如RS-422或者RS-232 是全雙工接口;而CAN總線則是半雙工總線。RS-485就是一種半雙工總線:

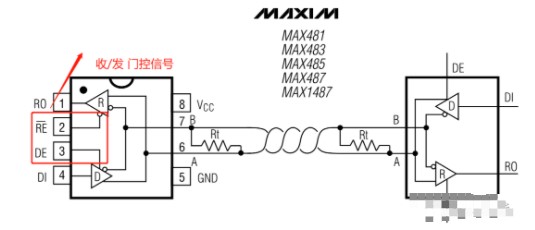

當Host發送數據時,數據沿著紅色的線經由雙絞線,傳輸至Slave的差分接收電路,當slave應答時,數據沿著蘭色的方向傳輸至Host的接收電路,但是傳輸介質是一對雙絞線,所以一方在傳輸數據的時候,另一方是無法傳輸信號的,從收發器的控制角度來看: 控制芯片側,用一個GPIO腳來控制收發使能,來一張芯片內部原理框圖,就很容易理解了:

當DIR=0時,接收電路使能,發送電路禁止DE=0,對總線而言相當于高阻;當 DIR=1 時,接收電路使能,發送電路禁止DE=1,對總線A/B信號取決于DI的信號。這里有兩個問題: 1.為什么芯片要把和設計成相反的有效邏輯呢?這樣其實也是方便用一個GPIO同時控制收發電路的考慮。 2.那收發器芯片收發使能為什么不做成一個腳呢?比如就叫DIR?做成兩個腳收/發也可以用兩個腳單獨控制,比如:

甚至可以在DE=1的時候,將設置為0,這樣是不是就可以自環了?產品中也可以就這樣設計,可以實現收發器以及布線的自診斷,通過接收到的報文與發送出去的報文比較,可以診斷出芯片焊接,收發器是否損壞或者斷路,以及布線是否存在短路故障。 或許你會說,瞎扯!你前面才說RS-485不能同時收發,這里又說能同時收發,豈不是自相矛盾嗎?不矛盾,前面所說的不能同時收發,是指發的同時不能收來自其他設備的發送報文,這里收的是自身發出的報文。

所以半雙工的本質,是通訊介質不存在雙向通道,在向總線發送數據的時候,介質被占用,即便想發送也是無法正確的將信號發送到介質上的,如果強行發送,數據將會錯亂,甚至收發器芯片有可能損壞。

: Receiver Output Enable,接收器使能,

DE:Driver Output Enable,驅動輸出使能

圖中的DIR腳就是控制當前RS-485是處于“收”還是處于“發”模式。

前面說到共模電壓指標以及差模傳輸方式,這里來實際抓抓波形看看:

示波器的CH2接485輸出A端,CH3接485輸出A端,紅色的為示波器的MATH功能:CH2-CH3。大部分示波器都具有數學運算功能。

如果想看差分信號,就可以利用雙通道示波器加MATH減功能觀測。或許有的示波器沒有MATH功能,那么這里還可以使用一個技巧:

將B通道,或者說差分信號的負端反相,然后將B通道上移至空閑電平重合,這樣是不是也就比較直觀的可以看出A-B了? 通過這個圖,能發現哪些有價值的信號特征呢?

信號A在空閑時候為高電平;信號B在空閑時為低電平。所以你會看到有設備上會標識485_A+,485_B-。

每個通道的共模電壓值都在標準要求的-7~12V之內,信號A為4V,信號B為5V:

那么數據怎么去解讀呢? 這里抓的數據是一個MODBUS-RTU主端發送給從設備的報文,其內容前面兩個字節是0x01 0x03,UART模式為1個起始位,8個數據位,1個停止位,無校驗位,低位在前,此例中UART的通訊格式為

先根據UART通訊模式,來計算一下幾個參數,每bit占用時間,每字節占用時間:

這個圖就是起始位,寬度正好是104us。 對于解析這種異步串行時序波形而言,最重要就是根據通信格式計算位時間,字節時間,進而可以直接解析波形數據。從這一點思考,假設要利用FPGA來實現一個UART協議邏輯分析儀,這就是最為核心的指標,通過檢測到起始位邊沿,進而通過時間軸將數據解析出來。這里我來充當一個肉眼UART邏輯分析儀吧:

8bit數據的時間寬度剛好是832us,由于格式是低位在前,所以要反過來看,與實際發送的數據0x01 0x03是吻合的。 這里在調試底層的時候遇到問題,就可以通過這種方式可以檢查軟件是否正確的驅動了硬件,譬如在調試I2C/SPI等等其他底層接口的時候,都可以類似的去檢查硬件波形,唯一不一樣的是,I2C/SPI屬于同步通信,所謂同步通信,是指其通信底層有同步時鐘信號,I2C的SCL,SPI的SCK都屬于同步時鐘。

驅動能力

電氣參數里總結說RS-485最大電氣驅動能力,在多點網絡拓撲結構下,可最大驅動32個站點。那么怎么去解讀這一指標呢? 首先來考察一個站點收發電路特性,收發器的接收電路其標準等效輸入阻抗為12k?,比如MAX 485數據手冊為例:

至于為什么是32個呢?主要是由于前面200mV最小驅動能力的規定。 也可以這樣理解一下,每一個接收電路輸入阻抗并非理想的高阻,而是12k?,那么比如其中一個站點發送,就相當于有32個站點的輸入阻抗并聯,為什么是32個呢?別忘了發送站點自身也有接收電路,所以在不考慮端接電阻以及線路阻抗的情況下,對于發送電路接了一個等效負載:,而發送電路驅動能力肯定是有限的,這樣就好理解了。 下面這個圖就是所謂的多點網絡拓撲,所有的站點都是沿著雙絞線的排布并接在總線上的。

所以,你有可能會在一些地方看到所謂的一個單位RS-485負載的說法,這里所謂的單位負載就是指12k?標準輸入阻抗,這個12k?就是EIA-485標準定義的。從而看到比如單位負載之類的說法,就是源于此處。

數據監控

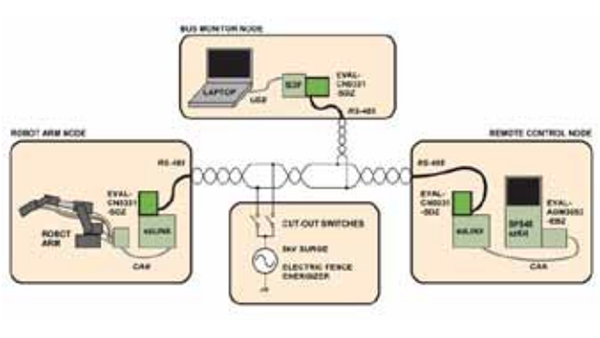

比如一個基于RS-485的Modbus-RTU多點網絡中,在做協議編程或者實際多站點總線調試的時候,有可能需要監控總線上所有的報文。甚至還有可能就像實現一個總線報文的的記錄器,將總線上所有的報文都記錄下來。應該怎么實現呢? 買一根USB轉RS-485的轉換線或者自己做一個也可以。將A/B線并接在總線上,USB 插入電腦。使用串口監控終端或者自己寫一個串口接收小軟件,就可以監控所有總線上的報文了。 比如這個AccessPort串口工具就比較好用:

應用設計

作為應用設計而言,需要考慮這些維度:

端接設計

接口芯片

隔離設計

端接設計

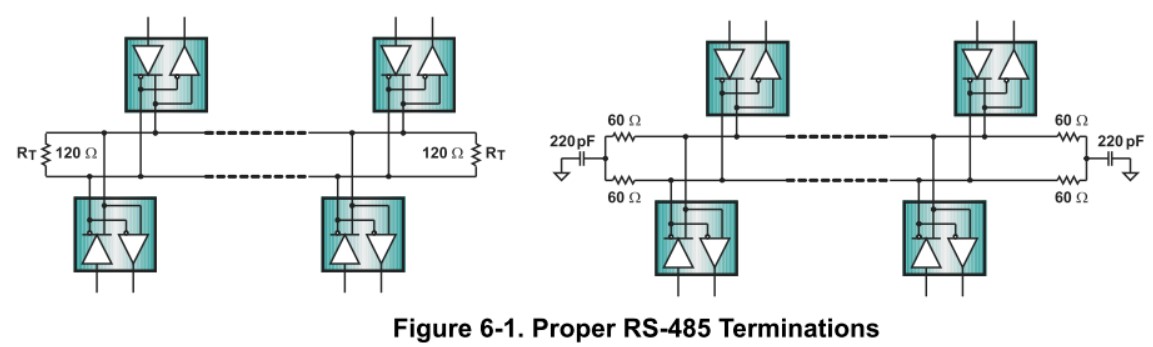

首先為什么要端接?這是由于RS-485采用雙絞線傳輸,標準規定的雙絞線的差分特征阻抗在100Ω至150Ω之間。RS-485標準制定者選擇120Ω作為標稱特征阻抗。

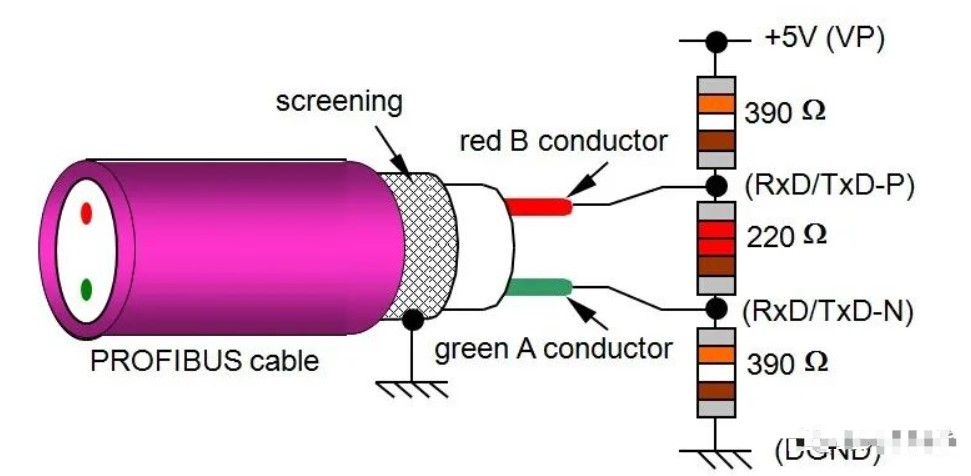

假定信號自左邊站點發出,如果沒有端接,信號在線路上傳輸其阻抗是連續的,但是到達右側的時候則,等效阻抗變成了接收電路的輸入阻抗,比如是12kΩ,阻抗不連續了,阻抗突變!信號的一部分能量就會按照原路徑返回,如返回回去的信號由于容抗及感抗,就會產生相差。反射回去的信號與原信號疊加在一起。這樣就會造成通信發生錯誤,嚴重的時候,通信就無法正確進行。 要想更深入的了解背后的原理,可以去學習一下傳輸線理論。 或許做過Profibus DP(物理層也是采用的RS-485)的朋友會說,你看profibus DP為什么推薦的終端匹配電路是下面這樣的呢?

其實是因為Profibus DP采用的通信介質其標稱特征阻抗不一樣。所以實際工程應用的時候則會有小的差異。 在TI的資料上看到這樣一個端接接法:

在噪聲比較嚴重的場合,建議使用右邊的端接方案,利用兩個60Ω電阻以及220pF電容形成低通濾波器,將增加線路的抗噪聲能力。 在實際工程布線的時候,如果遇到噪聲比較嚴重的時候,一方面可以利用示波器查看總線信號質量,在將端接方式做一些小的調整。

接口設計

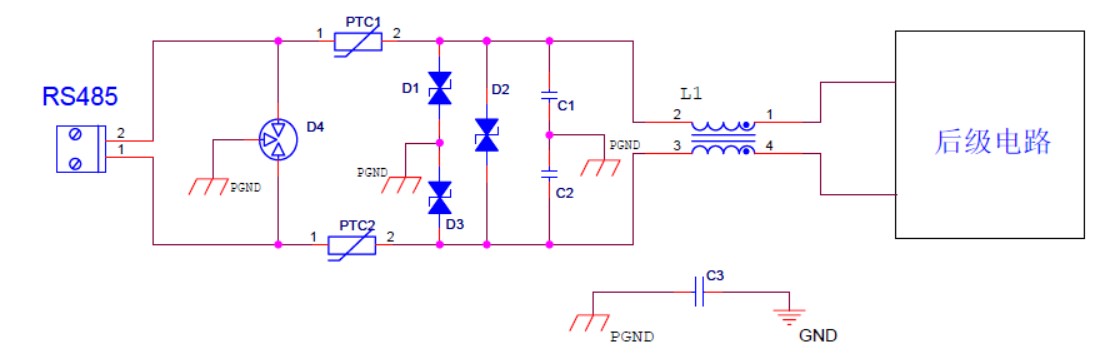

RS-485收發器芯片很多芯片公司都提供,比如TI,Microchip 等廠家都有,選擇接口芯片的時候需要考慮,芯片的供電電壓輸入邏輯是否與使用的單片機/DSP的電平兼容,另外就是前面提到的其接收電路的阻抗是否是符合RS-485標準輸入阻抗的。如果不是的,那么在考慮網絡部署的時候,所能帶的負載數量就有可能需要做調整。另外注意一下,有的新設計RS-485收發器具備fail-safe功能。 另外,前面說到標準收發器可以驅動32個標準收發器負載設備,也即是(12kΩ)標準單位輸入阻抗。 在做具體接口電路設計的時候還需要考慮EMC要求,在一些設備現場真的有很強的干擾,比如電網上有大的電機等感性設備運行,有時候就會干擾設備;另外也有可能有空間輻射干擾,這時候可以考慮采用帶屏蔽雙絞線,屏蔽層接大地,抗干擾方面我了解的不是很深入,僅整理一下。在這里看到一個防雷接口電路的設計方案,可以參考一下:

https://www.programmersought.com/article/95833359295/ 前面說通常標準RS-485可以容納32個標準接收阻抗收發設備。實際系統中就是想接入超過32個站點設備,怎么辦呢?可以設計一個中繼設備。想當于將兩個網段利用中繼給銜接起來,以解決驅動能力不足的問題。當然也有這樣的現成產品。

隔離設計

為什么要隔離,是為了降低接地噪聲。在很多現場可能有大電流開關設備,電機感性設備等,噪聲很有可能通過通訊的接地耦合進設備。尤其在工業設備中,一般都會設計成帶隔離的接口電路。要設計隔離接口,可以考慮選擇具有隔離功能的芯片,比如ADI的 iCoupler技術產品ADM2481,ADM2485。當然也可以采用光耦+普通RS-485收發器的方式。唯一需要注意的是需要設計一個帶隔離的電源,給隔離兩側電路分別供電。

總結一下

RS-485看似簡單,實際應用設計的時候還是有很多需要去理解和注意的地方。做一個穩健的產品,往往所差不是大方向,而是一些細微處容易導致產品不穩定。

責任編輯:lq6

-

總線

+關注

關注

10文章

2866瀏覽量

87981 -

RS-485

+關注

關注

11文章

679瀏覽量

84176

原文標題:RS-485總線,這篇很詳細

文章出處:【微信號:gh_c472c2199c88,微信公眾號:嵌入式微處理器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【RS-485總線】如何提高總線抗擾度之EFT篇

【RS-485總線】如何快速解決RS-485組網通訊異常?

RS-485總線電平異常解決方案解析

【RS-485總線】詳解RS-485上下拉電阻的選擇

將傳統RS-485系統與TI基于RS-485的Powerbus結合使用

靈活的RS-485:采用THVD1424的RS-485多系統簡化設計

沒聽過這個,都不好意思說自己做過RS-485總線開發!

和大家聊一聊RS-485總線

和大家聊一聊RS-485總線

評論