要問做邏輯的什么看的最久,那一定是波形吧。那除了看波形,還能做點(diǎn)兒其他的么?

調(diào)試“三十六計(jì)”

作為邏輯開發(fā)者,仿真是一個(gè)永遠(yuǎn)跑不掉的話題。盡管說嚴(yán)格來講設(shè)計(jì)和驗(yàn)證是分離的,但對(duì)于FPGA開發(fā)來講,即便是大廠也很少配備專門的邏輯驗(yàn)證人員來支持你的工作。無論是單元級(jí)仿真還是系統(tǒng)級(jí)仿真,那些年我們常用到仿真調(diào)試手段首推的估計(jì)就是看波形了。但老實(shí)講,小的模塊或者小的case看看波形還好,但如果是比較大的模塊或case需要很長的時(shí)間來跑的話那么追蹤波形對(duì)我個(gè)人來講還是很廢眼神的~

那么除了查看波形,我們常用的仿真調(diào)試手段無外乎在待仿真測(cè)試邏輯里添加打印和添加SVA了。對(duì)于添加打印,在之前通過verilog/systemVerilog搬磚時(shí)是時(shí)常干的事情,而SVA在上學(xué)的那會(huì)兒倒是看過下面這本書:

那么如今轉(zhuǎn)到SpinalHDL,這些手段是否還能用呢?

Assertion

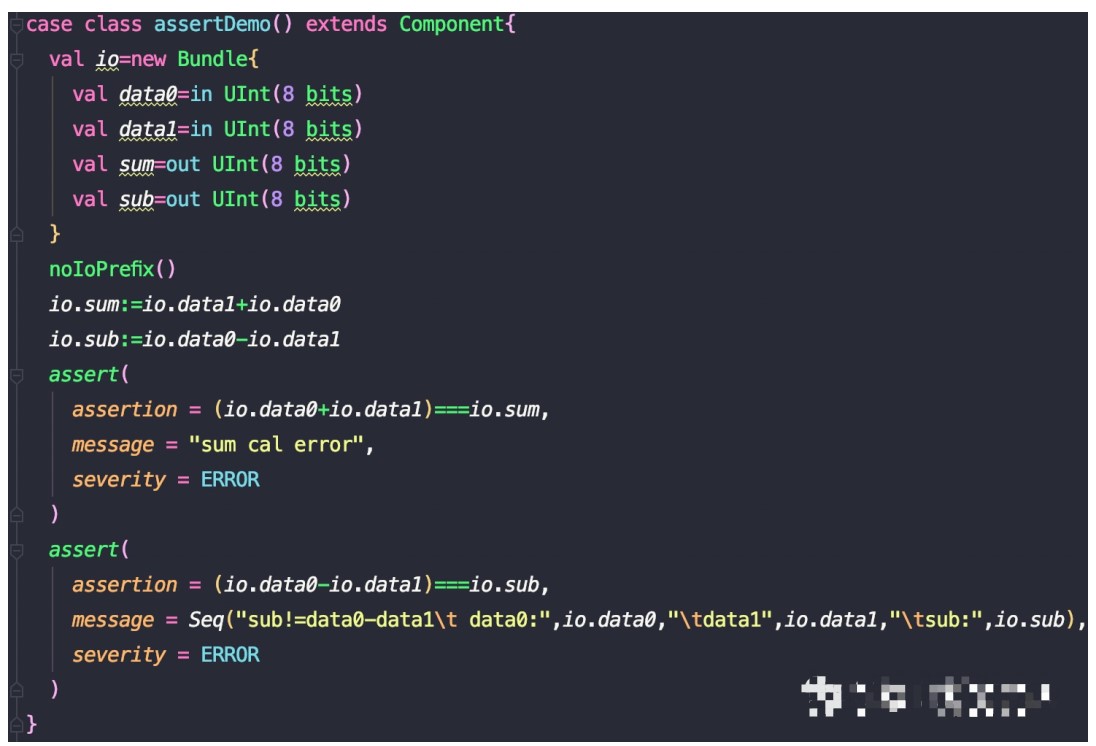

與SystemVerilog中相似,SpinalHDL中也提供Assertion功能,其關(guān)鍵字也為assert:

assert(assertion : Bool, message : String = null, severity: AssertNodeSeverity = Error)assert(assertion: Bool, message: Seq[Any], severity: AssertNodeSeverity)

assertion:斷言條件

message:斷言失敗時(shí)顯示信息,可以是字符串或者是Seq。

severity:斷言等級(jí)。

來看一個(gè)demo:

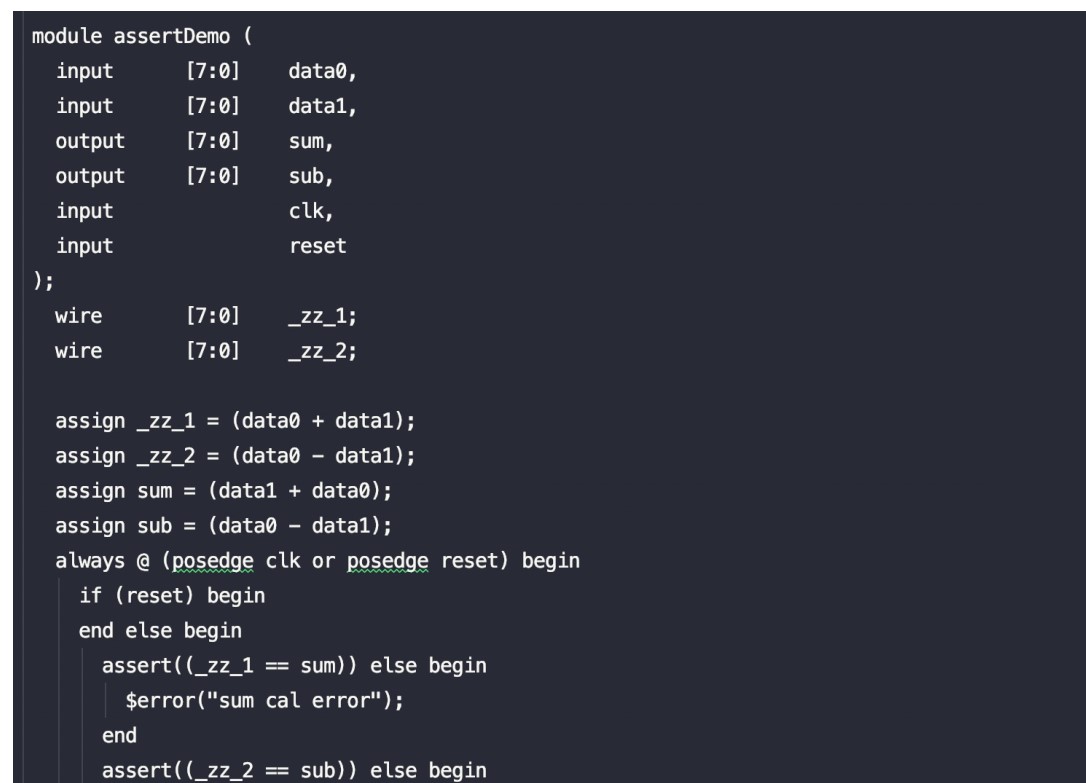

這里放置了兩個(gè)assert,分別使用了兩種assert的使用方式。message中放置Seq時(shí)可以顯示更多的提示信息。 要知道即便我們是采用SpinalHDL,在仿真的時(shí)候還是要生成Verilog文件交給仿真器去執(zhí)行的。那看下生成的RTL代碼:

可以看到,在SpinalHDL中,對(duì)于SVA中的立即斷言和并發(fā)斷言,其只支持并發(fā)斷言。而且會(huì)生成額外邏輯用來支持?jǐn)嘌裕以趶?fù)位期間是不做斷言檢查的。

report

SpinalHDL中提供了report方法用于在邏輯中顯示打印信息:

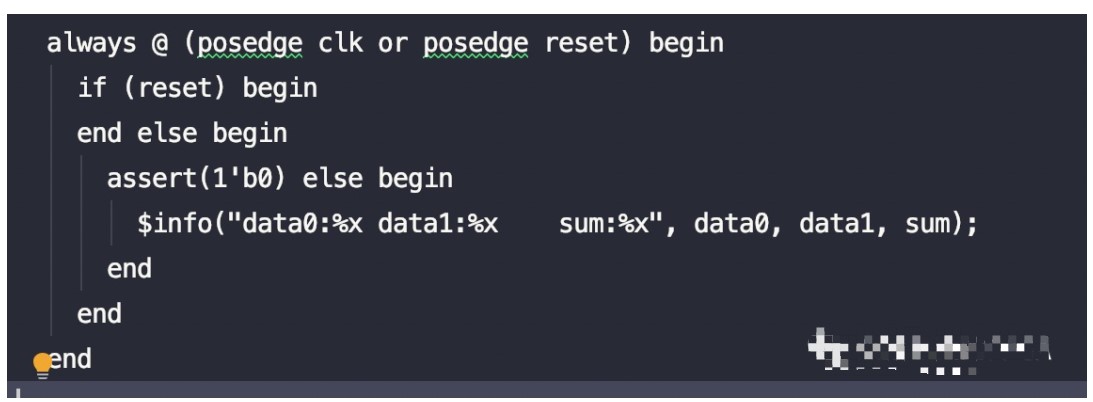

def report(message: String) = assert(False, message, NOTE)def report(message: Seq[Any]) = assert(False, message, NOTE) def report(message: String, severity: AssertNodeSeverity) = assert(False, message, severity)def report(message: Seq[Any], severity: AssertNodeSeverity) = assert(False, message, severity) 可以看到,report的底層實(shí)現(xiàn)是基于assert來實(shí)現(xiàn)的,且默認(rèn)斷言失敗,故而信息會(huì)一直打印。像上面的dmeo我們可以添加下面的打印信息:

report(Seq(“data0:”,io.data0,“ data1:”,io.data1,“ sum:”,io.sum),WARNING)

在生成的RTL代碼中會(huì)有:

同樣不出意外,在復(fù)位期間將不會(huì)打印任何信息。

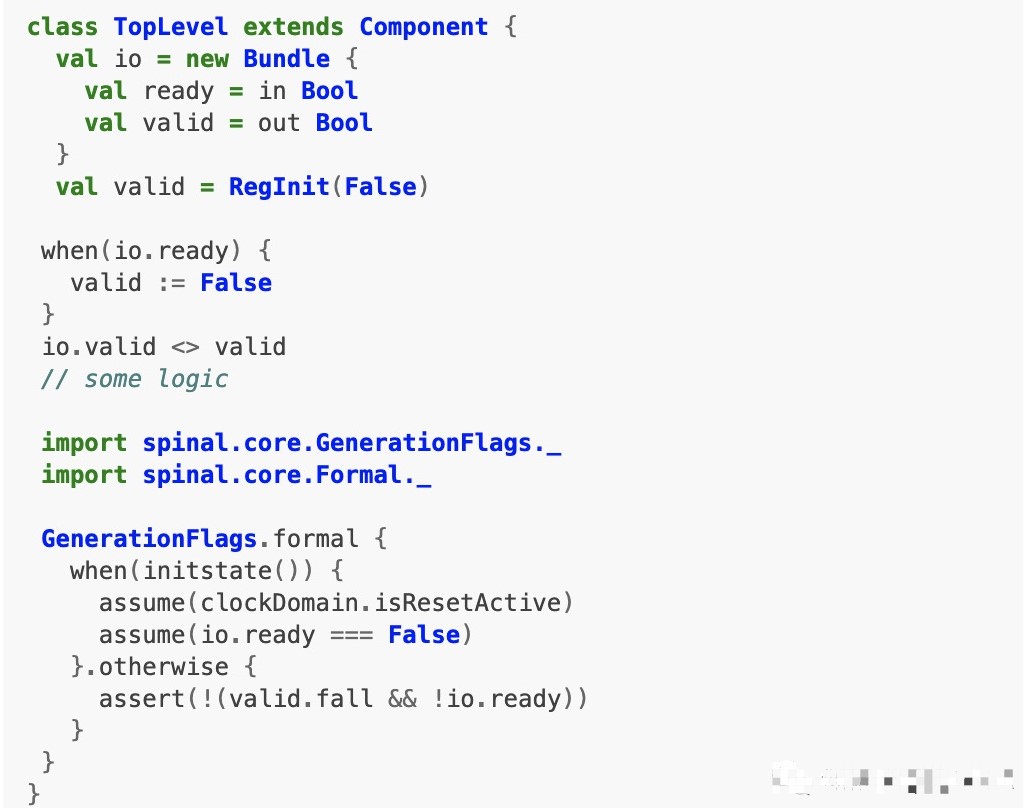

Formal

針對(duì)SVA的支持,SpinalHDL提供了部分支持。在SpinalHDL-Doc中給出了下面的這個(gè)Demo:

object MyToplevelSystemVerilogWithFormal { def main(args: Array[String]) { val config = SpinalConfig(defaultConfigForClockDomains = ClockDomainConfig(resetKind=SYNC, resetActiveLevel=HIGH)) config.includeFormal.generateSystemVerilog(new TopLevel()) }}

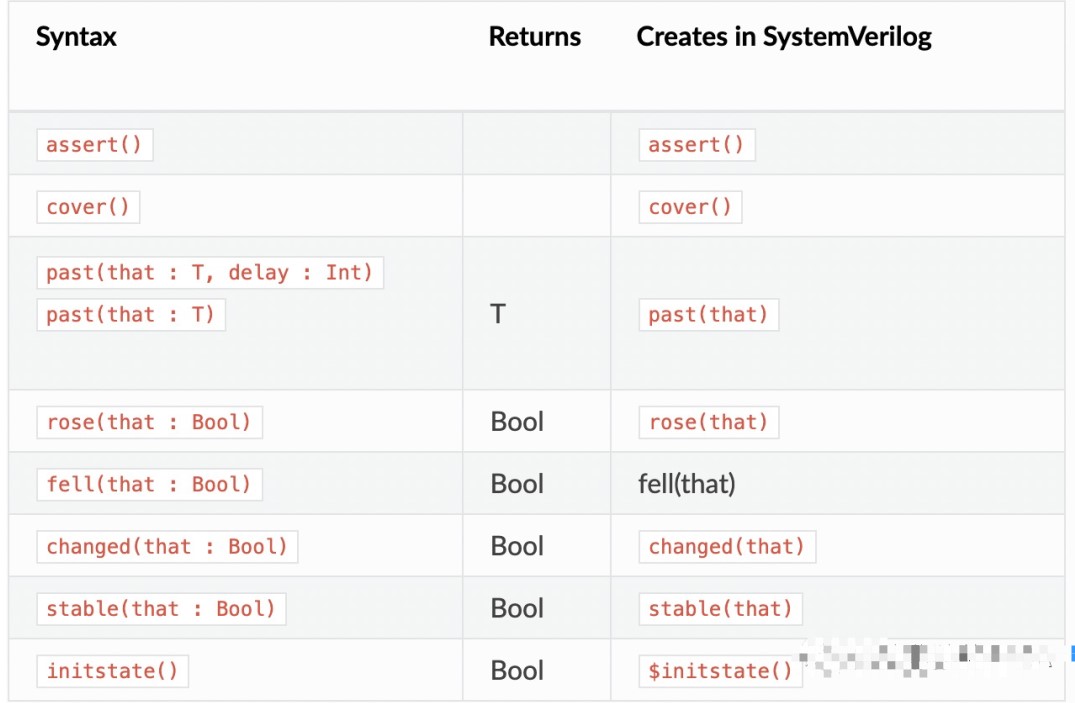

但這個(gè)demo有幾個(gè)問題是: 1、使用GenerationFlags.formal及includeFormal時(shí)如果我們的代碼在GenerationFlags外圍如果有使用assert或者report時(shí),GenerationFlags.formal會(huì)將其屏蔽掉,在仿真時(shí)不起作用。 2、initstate()在verilator中不支持。 針對(duì)上面的問題,可以采用: 1、采用GenerationFlags.simulation和includeSimulation替代GenerationFlags.formal及includeFormal。 2、如果要在復(fù)位期間添加sva,那么通過clockDomain.isResetActive替換initstate() 當(dāng)在生成Verilog時(shí)不添加includeSimulation,那么GenerationFlags.simulation所包含的內(nèi)容將不會(huì)生成在Verilog中,從而能夠提供一個(gè)干凈的代碼。 手冊(cè)中給出了支持的SVA:

但具體還是要看仿真器是否支持,畢竟verilator和vcs這些在功能上還是有一些差距。

文章來源:Spinal FPGA

圖片來源:似猿非猿的FPGA

責(zé)任編輯:lq6

-

仿真

+關(guān)注

關(guān)注

50文章

4044瀏覽量

133421 -

HDL

+關(guān)注

關(guān)注

8文章

327瀏覽量

47340

原文標(biāo)題:除了看波形,還能做點(diǎn)兒啥

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

谷景科普一體成型電感外殼破損還能不能用

設(shè)計(jì)仿真 基于VTD的AR-HUD仿真測(cè)試解決方案

解鎖SoC “調(diào)試”挑戰(zhàn),開啟高效原型驗(yàn)證之路

AFE77 JESD204B 調(diào)試手冊(cè)

TI AFE8092 AFE8030 JESD204配置及調(diào)試手冊(cè)- Part A

TI AFE8092 AFE8030 JESD204C配置及調(diào)試手冊(cè) Part B

TI AFE8092/AFE8030 JESD204C配置及調(diào)試手冊(cè) Part C

請(qǐng)問PMODE[2:0]處于懸空狀態(tài),即FFF,USB接口還能用嗎?

單片機(jī)Debug的這幾種方式,你都知道嗎?

仿真調(diào)試手段在SpinalHDL中還能用嗎?

仿真調(diào)試手段在SpinalHDL中還能用嗎?

評(píng)論