SoC(片上系統)的概念已日益普及,而隨著FPGA技術的迅速發展,可編程系統芯片(SoPC)作為一種特殊的嵌入式微處理器系統,融合了SoC和FPGA各自的優點,并具備軟硬件在系統可編程、可裁減、可擴充、可升級的功能,已逐漸成為一個新興的技術方向。SoPC的核心是在FPGA上實現的嵌入式微處理器核,目前主要有Xilinx公司的32位軟核MicroBlaze、32位PowerPC系列處理器硬核PowerPC 405,以及Altera公司的Nios系列微處理器軟核等。

本文介紹的系統是一個以PowerPC 405為微處理器,基于VME總線的以太網接口設備,它通過以太網和VME總線接口,實現VME系統與外部局域網的實時數據交換。

硬件開發

開發采用Xilinx公司的EDK7.1(嵌入式開發套件)和ISE7.1工具軟件。EDK工具包中集成了硬件平臺生成器(Platgen)、軟件平臺生成器(Libgen)、仿真模型生成器(Simgen)、軟件編譯器(Mb-gcc/ppc-gcc)和軟件調試工具(Mb-gdb/ppc-gdb)等,通過提供的集成開發環境XPS,用戶可以調用上述所有工具,來完成嵌入式系統開發的整個流程。

首先在XPS界面環境下生成硬件系統框架并添加所需的IP核,也可以用文本編輯器直接編寫硬件描述文件 (.MHS文件),再調用Platgen將其生成嵌入式處理系統的網表文件(.NGC文件);然后通過系統生成或手工編輯的軟件描述文件(.MSS文件)來設置系統軟件配置,并調用Libgen生成驅動層和庫。雖然EDK的IP庫中有一些很有用的功能模塊和外設接口的IP核,如DCM(數字時鐘管理器)、處理器復位、PLB/OPB總線接口、外部存儲控制器(EMC)、UART、GPIO、中斷控制器、定時器等,充分利用這些資源就可以構建一個較為完善的嵌入式微處理器系統,但是對于許多有特殊專用電路的嵌入式計算機系統的應用還是不夠的。如何將用戶專用電路設計到EDK系統中,一般有兩種方法,第一種是將EDK工程作為一個子系統在XPS中用Export to PorjNav生成ISE工程,然后在ISE中將專用電路和處理器子系統(system.vhd)合成為頂層HDL文件(system_stub.vhd)后,在ISE中完成綜合布線,最后在XPS中用Import from PorjNav得到硬件的.bit文件,便可以回到XPS中完成和應用軟件的合成、下載和調試了。第二種方法是將專用電路設計成為用戶自定義的IP Core,然后直接在系統中調用來實現。自定義的IP Core用HDL設計并要滿足EDK的規范,如有專門目錄結構和處理器外設定義文件(.MPD)、外設分析定義文件(.PAO)等。如果自定義的IP Core要具有軟件驅動,那設計還要完全符合相應的PLB或OPB總線接口規范。完成了硬件和驅動的設計后,就可以在XPS工程中添加應用軟件項目并編寫應用軟件,然后調用處理器對應的編譯器編譯并和硬件綜合后生成的.bit文件合成后下載到目標板便可以進行調試了。

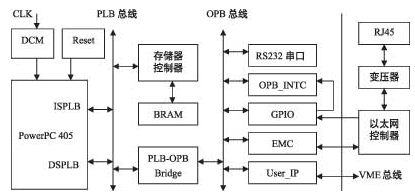

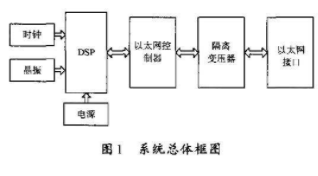

本系統硬件組成框圖如圖1所示。本設計選用Virtex-II Pro系列FPGA芯片XC2VP40,將系統的程序存儲器和數據存儲器都放在片內用Block RAM來實現,在系統中添加DCM模塊,將外部參考時鐘4倍頻提供給PowerPC 405作處理器時鐘,并分頻后再送給OPB總線作總線時鐘,降低慢速外設的總線速度,使系統搭配更合理。

圖1 系統硬件組成框圖

PowerPC 405是此嵌入式系統的核心,它通過PLB總線實現和程序存儲器和數據存儲器的快速通道,并通過PLB-OPB橋實現了片上的OPB總線,然后通過OPB總線進行各種外設的擴展,OPB外設包括一個RS232串口,一個OPB_EMC用于擴展以太網控制器芯片,一個GPIO作以太網控制器輸出的中斷請求,一個中斷控制器OPB_INTC將GPIO輸入的外部中斷通知PowerPC 405并可以設置優先級,還有一個用戶自定義的IP Core用于實現和VME總線的接口電路。

PowerPC 405 是專門為嵌入式應用而設計的高性能32位PowerPC系列處理器芯核,對于Virtex-II Pro系列FPGA,其實現型號為PowerPC 405D5。

PLB是處理器本機總線,它為指令和數據一側提供獨立的32位地址和64位數據總線。PLB總線架構支持多主從設備,每一個PLB主控機通過獨立的地址總線、讀數據總線和寫數據總線與PLB連接,有一個中央判決機構來授權對PLB的訪問以允許主控機通過競爭來獲得總線的所有權。OPB是片上外設總線,提供分離的32位地址總線和32位數據總線,一般用來訪問低速和低性能的系統資源。它是一種完全同步總線,但不直接連接到處理器內核,處理器內核通過“PLB to OPB”橋和OPB總線來訪問OPB接口外設。

網絡控制器采用Cirrus Logic公司的通用單片10/100M以太網控制器CS8900A,該芯片完全遵從與IEEE 802.3以太網標準,支持完全的全雙工操作。應用EDK的OPB_EMC IP可以很方便地將CS8900A擴展為系統OPB總線上的一個設備,只要將EMC端口的地址、數據總線以及控制信號分別接到CS8900A的地址、數據總線和控制端口上,并將EMC的時序參數設置成與CS8900A手冊上要求的一致就可以了。另外將CS8900A的中斷輸出INTRQ作為一個GPIO引入系統以實現以太網的中斷服務功能。

自定義的IP Core內容如圖2所示,它用FPGA內的Block RAM資源實現64KB的雙口RAM用來完成和VME總線上其他設備的通信和數據交換。我們用上述的第二種方法來實現將用戶專用電路嵌入微處理器系統中,自定義的IP主要包括OPB總線接口和用戶電路兩部分,我們用EDK提供的OPB總線的IPIF模板修改后,作為自定義IP的總線接口,64KB的雙口RAM和VME總線接口是真正的用戶電路。

圖2 自定義的IP Core結構

軟件開發

嵌入式開發環境EDK(Embedded Development Kit)將軟件開發分為兩大部分,一是底層系統軟件的開發,主要完成BSP(板級支持包)的功能;另一部分則是用戶應用軟件的開發(包括用戶硬件驅動及用戶上層應用軟件)。由于EDK中帶有許多IP核以及相應的驅動軟件,因此底層系統軟件的開發大部分可以借助EDK集成開發環境來完成的,如操作系統的選擇、設備驅動程序的選擇、中斷/異常處理例程的設置、操作系統參數設置等在內的各種系統級軟件參數的設置。而用戶應用軟件的開發由于有底層驅動的隔離,可移植性好。整個用戶軟件的開發及調試工作都可以在EDK中完成。

● 底層系統軟件開發

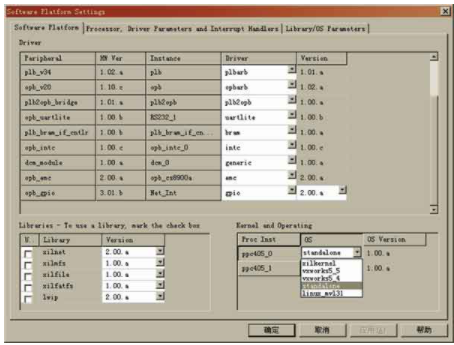

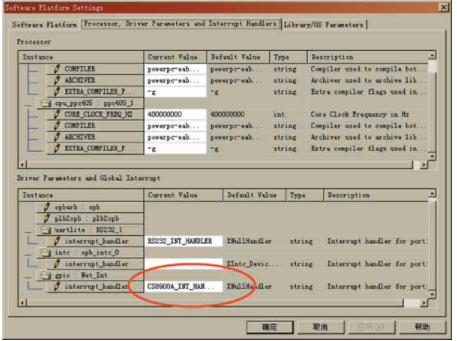

在本設計中,沒有使用操作系統,使用所謂的standalone模式,即EDK僅提供硬件初始化及引導代碼。此外還需要對GPIO、EMC、RS232、中斷控制器等一些外設生成底層驅動,這些都可以通過在EDK集成環境XPS中選擇菜單Project->Software Platform Settings的對話框進行設置,如圖3所示。其實質是自動修改工程的.MSS文件。例如中斷函數的處理例程可在如圖4所示的界面中加以設置。也可以手工編輯.MSS文件如下設置:

PARAMETER int_handler = CS8900A_INT_HANDLER, int_port = IP2INTC_Irpt

圖3 在XPS中設置操作系統和驅動程序

圖4 在XPS中設置中斷服務例程

設置完成后在XPS中運行Tools->Generate Libraries and BSPs將調用LibGen自動生成驅動庫文件,這些CPU和外設驅動庫的設置、操作函數實現或定義可在工程項目根目錄下的以處理器實例名為名字的目錄下的libsrc目錄下相應的各模塊子目錄中找到,參考其實現有助于深刻理解事實上發生的操作。例如中斷向量表可在中段向量控制器模塊子目錄(本例中為intc_v1_00_c\src)下的xintc_g.c文件中找到。

● 用戶軟件開發

用戶軟件主要是對網絡控制器、GPIO、RS232串口等的操作,其中控制CS8900A的程序是重要部分,它要完成TCP/IP協議。CS8900A所有的控制寄存器和數據寄存器都映射在被稱為PacketPage的片上4K地址空間內,這4K空間可映射到主機地址空間中(存儲器模式),或通過8個16位I/O口進行存取(I/O模式)。本設計中CS8900A工作于I/O模式,通過EDK的OPB_EMC IP作為OPB總線上的一個設備,并給EMC控制器和所映射的設備分配操作地址空間,在程序中用 Xuint32 XIo_In32(XIo_Address InAddress); void XIo_Out32(XIo_Address OutAddress, Xuint32 Value);

讀寫映射的設備,這兩個I/O函數同*pDestMem = Value(直接讀寫存儲器操作)的差別在于前者做了讀寫同步(調用eieio匯編指令)。參考芯片手冊編寫CS8900A的驅動,實現基本I/O操作CS8900A_SendFrame和CS8900A_RecvFrame。EDK中有需付費的以太網IP CORE并附帶有一些TCP/IP協議棧,該協議棧實現了大部分常用功能,但也有一些重要功能并未實現,例如TCP包的超時未達重發,收發操作的中斷工作方式。通過修改、增加和完善這些軟件包,實現了真正面向用戶更高層應用軟件的網絡編程接口。

● 軟件開發中的部分問題

軟件開發過程中遇到的幾個主要問題歸納如下:

(1)IEEE 802.3網絡及網絡控制器CS8900A采用的均是Little Endian編碼,而XC2VP40內含的處理器PowerPC 405D5采用的是Big Endian編碼方式,因此在數據I/O過程中需要做一下轉換。

(2)可通過編寫鏈接控制腳本文件控制應用程序的鏈接過程,從而控制程序映像在存儲器中的重定位過程。這在FPGA這種存儲器資源有限的環境中有時很有用。

(3)要將EDK提供的默認bootloop程序打包到硬件初始化流中,這樣做的目的是提供默認的CPU復位后運行程序,保證CPU處在可預知的狀態,而不是因為執行了存儲器中的隨機代碼而處于一種未知的狀態。

系統調試方法

由于PowerPC 405處理器核中已包含調試模塊,并用JTAG端口引出,只要在系統中添加一個叫做JTAGPPC的IP模塊并和PowerPC 405相連便可將其調試端口串入FPGA的JTAG鏈中,這樣只需使用FPGA本身的下載電纜和JTAG接口便可完成系統軟件調試而不需要增加額外電路。

EDK提供的軟件調試工具主要有XMD和GDB。值得一提的是利用XMD下載可執行程序映像時還會顯示各程序段的重定位情況,在發生錯誤時會報告錯誤,諸如要求的地址空間大于實際提供的地址空間等錯誤,而這在EDK集成環境下是看不到的。在存在多種類型存儲器資源的情況下,編寫鏈接控制腳本文件控制重定位過程可能能夠解決上述某地址空間不夠的問題。網絡通信部分的調試主要由Sniffer軟件輔助完成。

GDB是EDK附帶的GNU的主機方圖形界面調試工具,它通過和XMD通信完成圖形界面調試功能,此時XMD則扮演了一個主機方調試代理的角色,所有的調試通信是由XMD同目標機通信完成的。

結語

SoPC使得硬件設計能真正實現象搭積木一樣方便迅速,而利用EDK開發工具就可以實現一個基于FPGA的嵌入式系統的軟硬件一體化的開發,的確大大提高了嵌入式系統的開發效率,但是目前它還有許多不夠完善的方面。

首先是系統設計對設計工具軟件的依賴性很大,而這些軟件還有許多有待修正完善的地方,設計師無法避免將在使用熟悉軟件方面花許多時間。其次,IP Core的不斷豐富和完善是SoPC的基礎,昂貴的付費IP核不利于此技術的推廣,尤其在國內,而要設計驗證用戶自己的IP Core對設計者的要求較高。如今一個完善的嵌入式系統都有實時操作系統在運行,SoPC要成為主流也需要更豐富的RTOS的支持。

責任編輯:gt

-

以太網

+關注

關注

40文章

5287瀏覽量

169624 -

接口

+關注

關注

33文章

8249瀏覽量

149938 -

微處理器

+關注

關注

11文章

2211瀏覽量

81976

發布評論請先 登錄

相關推薦

一種低功耗以太網接口電路的設計方案

基于CAN總線與以太網的嵌入式網關電路設計

基于FPGA的萬兆以太網接口的設計與實現

基于ARM7內核和嵌入式系統的VME總線控制器的研制

嵌入式微處理器和接口詳技術詳解

在ZedBoard下SPI接口和ARM處理器端實現以太網遠端傳輸的設計

基于GAL芯片實現VME總線接口電路的設計流程概述

基于TMS320F28335和DM9000A芯片實現以太網接口的設計

基于PowerPC 405微處理器和VME總線實現以太網接口設計

基于PowerPC 405微處理器和VME總線實現以太網接口設計

評論