作者:Rajeev Kumar,Harpinder Singh

串行總線協議PCIe、ASI和sRIO的比較

電路板間以及背板上的數據通信越來越受到關注。由于下一代計算機、控制和通信系統的設計都是為日益提高的性能需求所驅動的,建立在共享多點并行總線協議和非標準小型封裝及機架上的傳統系統正在被小型模塊化系統所取代。

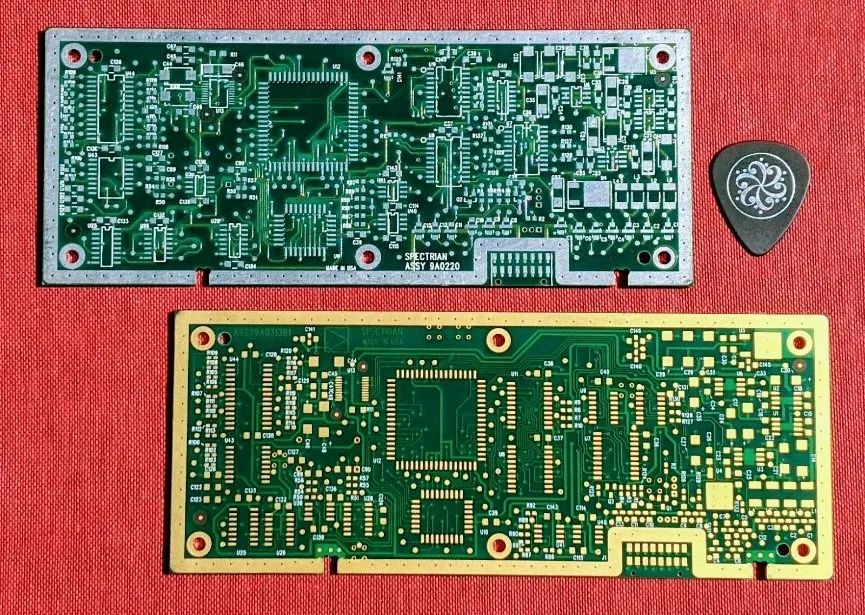

點對點的串行總線協議正在取代多點的并行總線協議。PCIe(PCI Express)和sRIO(Serial Rapid I/O,串行快速I/O)等片間串行總線互連正用于高速高密度的模塊設計,甚至更小的嵌入式設計也能受益于這些新的串行互連。

背板的總線互連是建立模塊化系統的關鍵。新的設計需要低延遲的互連,某些情況下,還需要互連具有多種QoS功能以使子系統緊密耦合。一些經銷商開發了專用的背板協議,但是,隨著ASI(Advanced Switching Interconnect,高級交換互連)的發展,專用背板會越來越少。

串行互連的構架

無處不在的PCI/PCI-X加載/存儲外設互連總線協議使用了深度優先的層次樹將I/O設備和CPU相連,PCIe是其后繼者。所有設備共享一個公共存儲器和I/O地址空間,數據包基于存儲器和I/O地址傳遞。

主機CPU經主橋(或稱根聯合體)與I/O設備相連,或轉為形成層次樹。PCIe的使用正在猛增,它被廣泛應用于PC、服務器、存儲器和電信系統。

sRIO同樣是串行加載/存儲總線協議,它針對基于DSP的嵌入式應用。sRIO有一個使用郵箱或隊列的信息設備,并用設備地址擴充了基于存儲器地址的路由。

sRIO與PCIe的主要區別在于它具有支持點對點通信的能力;SerDes采用×1和×4的縮減的連接寬度,速率為3.125Gb/s;此外,sRIO還有原子操作等附加的數據包定義。

sRIO的其他特性包括:簡單的地址分配路由、小數據包頭和基于郵箱的信息機制。通過延伸這一特性就發展成了快速結構(Rapid Fabric)。

為將控制系統、計算機和通信背板整合,ASI提供了可擴展的互連。它用三層堆棧結構使物理數據傳輸和同步,它也使用了PCIe的物理層和數據鏈路層,并進行了少許的增強。

傳輸層提供了基于路徑的路由機制,支持背板特性,并將應用空間擴展至包含路由器等通信系統。在ASI定義中包含了PI(協議接口),它為網絡以及傳統的或經銷商定義的開隧道(tunneling)提供了傳輸服務。

PI網絡服務基本規范包括設備管理(PI-4)、事件/錯誤處理(PI-5)、組播(PI-0)和拆分與重組的通用傳輸(PI-2),以及網絡管理。ASI配套規范定義了簡單排隊和簡單加載/存儲等附加的數據運動模型。

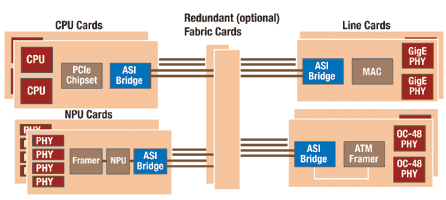

圖1 ASI構架和基于路徑的路由

ASI基于路徑的路由簡化了交換機設計,同時也通過免除對交換機路由表的支持縮短了延遲。圖1顯示了典型的基于背板的ASI系統及其基于路徑的路由。

總線協議的對比

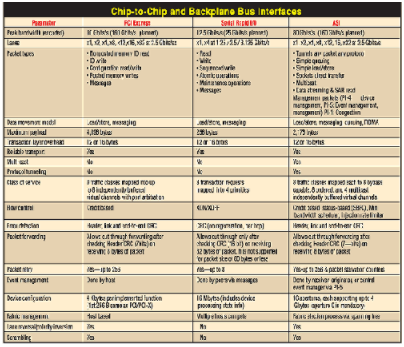

表1總結了片間和背板總線接口的關鍵特性。基于標準的高速串行互連和標準小型模塊化設計指出了下一代計算機與通信系統設計的方向。

表1 三種總線接口特性的對比

PCIe可能是大部分CPU和端點設備的選擇;sRIO有望成為用于無線基礎設施上線卡DSP的指導性方案;而ASI則提供了豐富的支持高性能背板互連的特性。

責任編輯:gt

-

計算機

+關注

關注

19文章

7425瀏覽量

87722 -

服務器

+關注

關注

12文章

9024瀏覽量

85187 -

路由器

+關注

關注

22文章

3708瀏覽量

113550

發布評論請先 登錄

相關推薦

器件高密度BGA封裝設計

應用于高密度電路板的表面粘著式自復式保險絲

高速高密度PCB設計的關鍵技術問題是什么?

高速高密度PCB 設計中電容器的選擇

高速高密度PCB的SI問題

用于高速高密度模塊設計的點對點串行總線協議

用于高速高密度模塊設計的點對點串行總線協議

評論