根據(jù)PCIE規(guī)范對(duì)設(shè)備的要求是PERST# must deassert 100 ms after the power good of the systems has occurred, and a PCI Express port must be ready to link train no more than 20 ms after PERST# has deasserted.

現(xiàn)在大規(guī)模FPGA的bitstream比較大導(dǎo)致板卡從上電到FPGA配置完成的時(shí)間遠(yuǎn)遠(yuǎn)超過100MS的要求,從而電腦端無法正常識(shí)別到PCIE設(shè)備。

為此Xilinx的PCIE Tandem(詳見PG156)功能是專為滿足PCIe設(shè)備在100ms之內(nèi)枚舉起來要求而設(shè)計(jì)的。

Zynq UltraScale+ MPSoC是Xilinx推出的第二代多處理SoC系統(tǒng),其PL提供高性能的PCIE GEN3 IP core給客戶使用。

由于MPSOC的啟動(dòng)加載image方式是跟純FPGA器件是有所差異,MPSOC器件是需要從PS部分先去加載bootrom里面內(nèi)容,然后按順序去加載FSBLBitstream等等內(nèi)容。

MPSOC加載是比純FPGA器件復(fù)雜很多同時(shí)差異也比較大,所以本文主要是介紹如何在MPSOC的器件里面實(shí)現(xiàn)PL PCIE tandem的加載方式來滿足PCIE規(guī)范里面對(duì)設(shè)備100ms的加載時(shí)間要求。

此設(shè)計(jì)流程是James Shen基于Xilinx AE Iris Yang提供的方法上面完善設(shè)計(jì)并進(jìn)行板卡驗(yàn)證。

詳細(xì)操作步驟請(qǐng)按照下面流程來進(jìn)行:

1、測(cè)試環(huán)境為ZCU106 V1.1板卡和Vivado 2019.1軟件;

2、由于ZCU106的PS DDR4 DIMM中間換過,所以新的DIMM需要按照下面參數(shù)來進(jìn)行修正,不然系統(tǒng)會(huì)無法啟動(dòng);

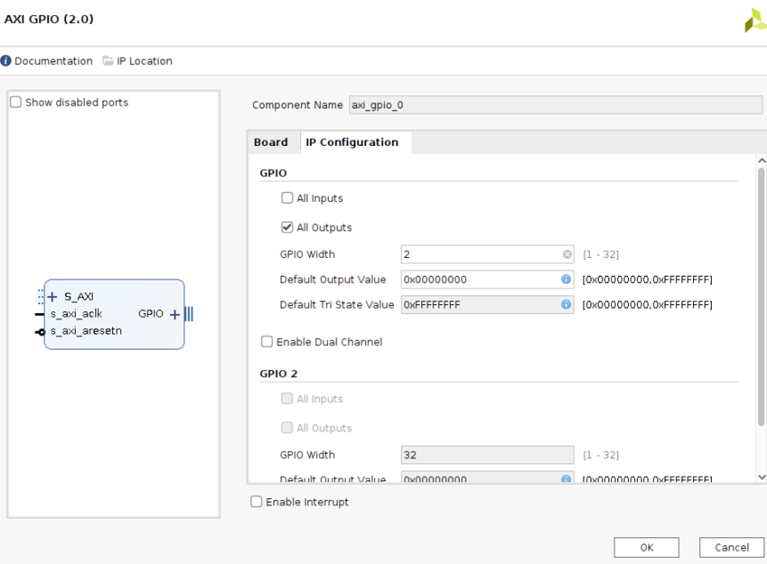

3、在PL里面搭建PCIE XDMA架構(gòu);

4、根據(jù)ZCU106板卡硬件做XDMA配置;

5、根據(jù)Xilinx的PCIE example design修改XDC約束;

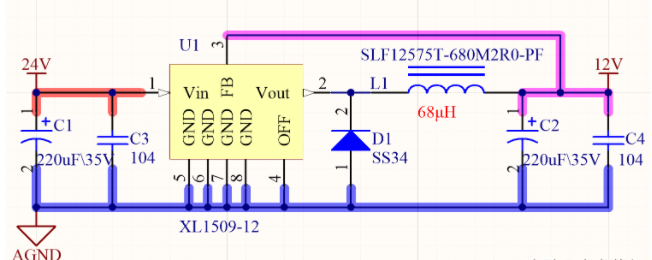

6、把ZCU106的QSPI配置同時(shí)提高時(shí)鐘頻率到300MHZ;

7、在XDMA界面設(shè)置Tandem PROM;

8、設(shè)置XDC里面相關(guān)約束文件;

9、修改xfsbl_qspi.c里面時(shí)鐘計(jì)算相關(guān)值;

10、去掉打印Debug等信息,從而節(jié)約加載時(shí)間;

11、修改xfsbl_partition_load.c來支持加載兩個(gè)階段的bitstream文件;

12、對(duì)ZCU106的硬件需要進(jìn)行設(shè)置;

13、生成相關(guān)boot image;

14、根據(jù)ZCU106板卡硬件選擇下載方式去下載bit到板卡上面就實(shí)現(xiàn)本文目的。

根據(jù)上文的流程和要求,經(jīng)過硬件板卡實(shí)際驗(yàn)證可以滿足PCIE在100ms之內(nèi)枚舉的要求。供大家參考。

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1626文章

21665瀏覽量

601814 -

Xilinx

+關(guān)注

關(guān)注

71文章

2163瀏覽量

121005 -

IP

+關(guān)注

關(guān)注

5文章

1649瀏覽量

149331 -

PCIe

+關(guān)注

關(guān)注

15文章

1217瀏覽量

82437 -

MPSoC

+關(guān)注

關(guān)注

0文章

198瀏覽量

24250

原文標(biāo)題:基于ZCU106來實(shí)現(xiàn)PL PCIE Tandem PROM功能

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何測(cè)試PROM器件的性能

PROM器件與FPGA的結(jié)合使用

PROM器件的編程和擦除方法

PROM器件的特點(diǎn)和應(yīng)用 如何選擇合適的PROM器件

LG Display首款13英寸Tandem OLED筆記本電腦面板投入量產(chǎn)

AMD Versal自適應(yīng)SoC CPM5 QDMA的Tandem PCIe啟動(dòng)流程介紹

Multi-Scaler IP的Linux示例以及Debug(上)

如何用 S7-200 實(shí)現(xiàn) Modbus 通信?

ZCU106評(píng)估板用戶指南

PCIe插槽竟然能玩出花樣?多個(gè)最新PCIe擴(kuò)展硬盤方式!#PCIe擴(kuò)展 #PCIe #硬盤盒

“PL7072鋰電池保護(hù)電路:功能全面,易于集成,電池安全新保障”

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

zcu102和zcu104有什么區(qū)別

PL2733C SOP-8 同步降壓電源管理芯片

如何用ZCU106來實(shí)現(xiàn)PL PCIE Tandem PROM功能

如何用ZCU106來實(shí)現(xiàn)PL PCIE Tandem PROM功能

評(píng)論