傳統的工業數據采集設計通常需要對模數轉換器 (ADC) 之前的模擬前端 (AFE) 進行復雜的濾波處理。模擬濾波器的主要目的是衰減不需要的帶外信號,進而防止這類信號在所需的目標信號上發生混疊,因此,模擬濾波器又稱為抗混疊濾波器 (AAF)。混疊頻段中不需要的信號和噪聲可能源自驅動放大器、電源切換引入的雜散,甚至是意外的干擾因素(干擾器)。

混疊頻率大小直接取決于 ADC 采樣速率,數據轉換器在給定瞬時帶寬下的工作速度越快,混疊頻段距離所需的信號就越遠,越容易進行濾波處理。根據這一現象,在精度非常高的系統中,設計人員通常使用具有高過采樣率和抽取濾波器的 Σ-Δ ADC。

在手機基站中,將 3GPP 的射頻直采頻段從 1GHz 增至 6GHz,提高了每秒千兆取樣率 (GSPS) 數據轉換器的使用率。由于 3GPP 頻段的瞬時帶寬只是此采樣率的一小部分,因此,使用過采樣 GSPS 轉換器的全新架構也放松了對模擬射頻濾波器的要求。

使用逐次逼近寄存器 (SAR) ADC 的各種工業應用(例如,電能質量分析、聲納或采樣率在 1MSPS 到超過 10MSPS 之間的工業雷達)也可以使用精密 Δ-Σ 和 GSPS ADC。高速 SAR ADC 的全新 ADC35xx 和 ADC36xx 系列具有一個集成式數字濾波器,因此工業應用可利用這一過采樣和抽取設計技術來降低對外部模擬濾波器的要求。

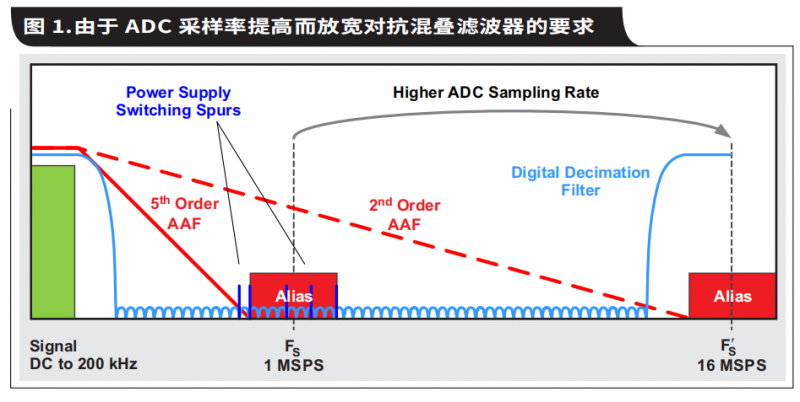

對于圖 1 所示的示例,假設直流輸入信號為 200kHz,ADC 采樣率為 1MSPS。實現約 300kHz 的通帶和 40dB 左右的混疊抑制大概需要一個五階濾波器。如將 ADC 采樣率從 1MSPS 增至 16MSPS,混疊頻段就會從 800kHz 推遠至 15.8MHz,所以將抗混疊濾波器替換為二階濾波器。此外,混疊頻段還會偏離此頻區(600kHz 至 2MHz),此頻區中通常包含由電源的開關穩壓器產生的雜散。

內部數字濾波器

下面主要介紹了內部數字濾波器的三種作用。

1.衰減混疊頻段信號

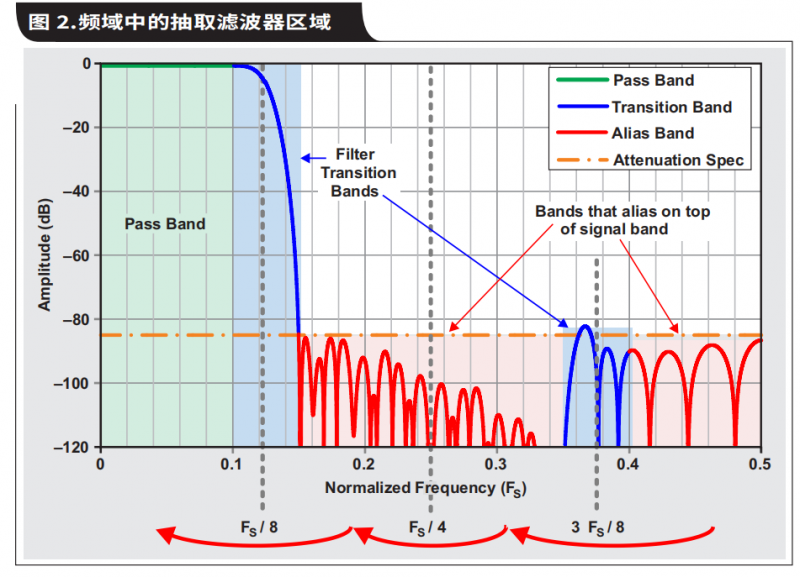

在頻域中常用的數字抽取濾波器是數字低通濾波器。該濾波器包括三個不同的頻域:通帶、多過渡帶和混疊帶,如圖 2 所示。在本圖中,混疊帶中的任何信號都會在通帶上發生混疊,但會衰減 85dB 左右或以上。所有三個混疊帶都圍繞 FS/8、FS/4 和 3 FS/8進行鏡像。

2.降低輸出數據速率

下游處理器可能很難處理較高的過采樣率。而且,在過采樣配置中,大部分頻譜都只包含不需要的分量,傳輸這些分量會造成不必要的能量消耗。數字濾波器會丟棄樣本并降低輸出數據速率。

目標頻段不在低頻率范圍內時,數字混頻器會對信號進行降頻轉換,然后再進行低通濾波,從而更大程度地降低輸出速率。

3.提高 SNR

數據轉換器的信噪比 (SNR) 是通過對 ADC 整個奈奎斯特區域的底噪進行積分運算來計算的。理論上,每個數字抽取因子 2 都會使 ADC SNR 增加 3dB。實際上,在帶內噪聲成為主要噪聲前,ADC SNR 的增加幅度很接近 3dB。

在之前的示例中,ADC 采樣率從 1MSPS 增至 16MSPS。增加抽取因子為 16 的數字濾波器會將輸出速率降至 1MSPS,而將 ADC SNR 提高多達 12dB (4 × 3dB)。

噪聲頻譜密度 (NSD) 是數據轉換器噪聲性能的另一個量度。它將 SNR 和帶寬考慮在內,通常用于比較不同的數據轉換器。例如,SNR 為 82dB 的 16MSPS ADC 的 NSD 為 –151dBFS/Hz [82dB + 10 × LOG (8MHz)]。在抽取因子達到 16 后,SNR 會增加 12dB(從 82dB 增至 94dB),而 NSD 會保持在 –151dBFS/Hz [94dB + 10 × LOG (0.5MHz)]。

了解抽取濾波器

以下多項權衡因素決定了數字濾波器的架構和濾波器抽頭的數量:可編程系數和固定系數、最大帶通紋波、最小阻帶衰減、延遲和功耗。例如,濾波器滾降越快,阻帶衰減越多,就會需要更多的濾波器抽頭,從而導致較高的功耗和較長的延遲。濾波器系數決定濾波器提供低通、高通,還是帶通頻率響應。

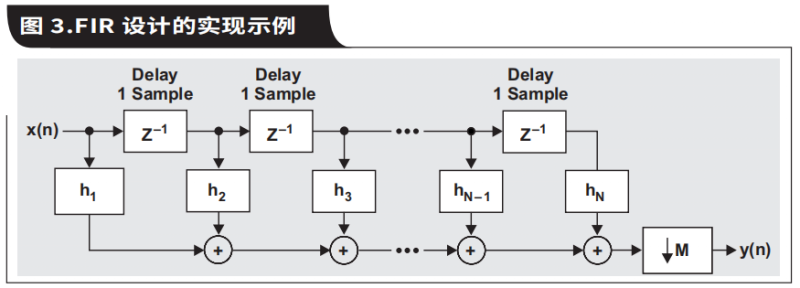

將數字濾波器與高速數據轉換器集成時,ADC 設計人員通常使用有限沖激響應 (FIR) 半帶低通濾波器,因為這種濾波器的設計本質上非常節能。半帶意味著抽取因子為 2,其他每個系數均為 0,并且這些系數無需任何計算。非零系數關于脈沖響應中心對稱。

圖 3 顯示了常規 FIR 的實現方案。在具有 7 個抽頭/系數 (N = 7) 的半帶實現中,除了 h4 之外的所有偶數抽頭(h2、h6)都為 0,從而將 7 個乘法減少至 5 個。如果抽取因子較高,會連接半帶濾波器。理論上,低通、高通或帶通濾波器可以與 ADC 相集成,但是,低通濾波器是更實用的選擇,尤其是在添加復頻混頻器以構建數字調諧器時更是如此。

請注意,數字濾波器位于模數轉換之后。因此,數字濾波器無法防止接收器的干擾導致 ADC 達到飽和狀態。但是,仍有必要使用外部濾波和可調節的增益來防止 ADC 過載。

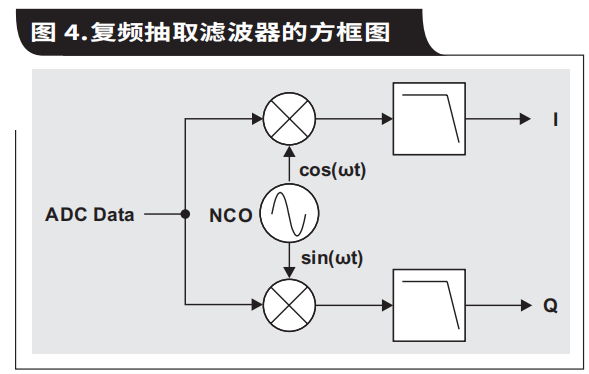

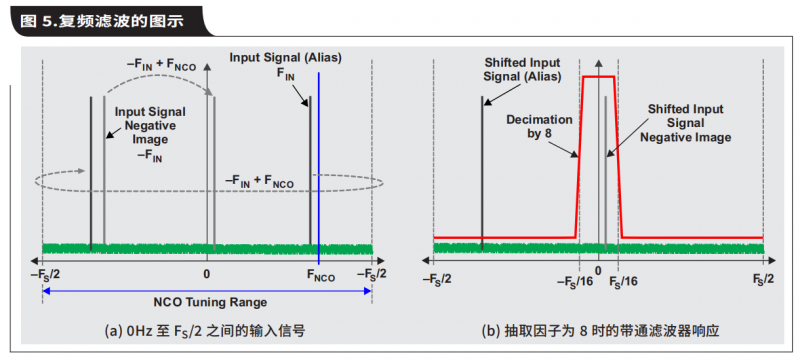

復頻抽取 - 數字調諧器

添加復頻混頻器 [對 I/Q 輸出使用 cos(ωt) 和 sin(ωt)] 可將兩個數字低通濾波器轉換為可調節的數字帶通濾波器,如圖 4 所示。該混頻器將數控振蕩器 (NCO) 用作本振 (LO)。“I”路徑和“Q”路徑都相當于此頻域中的低通濾波器。正弦、余弦之間的相位差消除了正/負頻率。數字混頻器會將正或負奈奎斯特區域中的任何頻率轉換為 0Hz,從而實現功能強大的可調帶通濾波器,同時還替代了傳統的模擬混頻器。

0Hz 和 +FS/2 之間的輸入信號 (FIN)。該輸入信號 (–FIN) 的負頻率介于 0Hz 和 –FS/2 之間。輸入信號及其負頻率都與 NCO 頻率(在此示例中為 +FNCO)混合。在 –FIN 旋轉至正奈奎斯特區域時,+FIN 旋轉至負奈奎斯特區域。此示例顯示了在 0Hz 下、抽取因子為 8 時帶通濾波器的響應,會傳遞與 NCO 頻率 (FOUT = –FIN + FNCO) 混頻的 –FIN 頻率。

實際示例

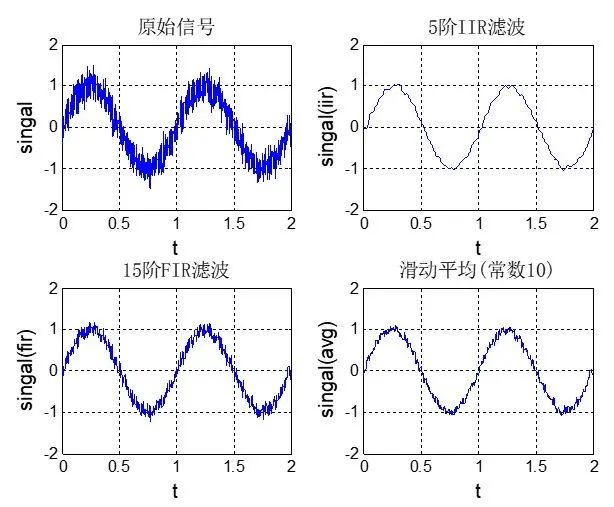

在時域應用中,數字低通濾波器可以去除輸入信號上的高頻噪聲。對脈沖形狀的波形進行采樣時,低通濾波器將移除較高階的諧波,從而降低脈沖的邊沿速率。

綜上所述,在雷達等頻域應用中,集成式抽取濾波器可提供強大的功能。圖 6 進一步說明了分別在 FS = 65MSPS 下、使用復頻抽取因子 8 和 NCO 頻率 5.5MHz 對輸入信號 FIN 進行采樣的結果。

結束語

為了減小印刷電路板的尺寸并降低物料清單成本,設計人員希望使用數字邏輯/知識產權 (IP) 替換模擬電路。具有集成式數字濾波功能的高速 SAR 數據轉換器(如 ADC35xx 和 ADC36xx 系列)非常適合各種各樣的工業應用。與 Δ-Σ 轉換器相似,得益于較高的過采樣率和集成式數字濾波功能,這些 ADC 也放寬了對模擬濾波器的限制。復頻混頻器還可以去除模擬混頻級,從而進一步簡化了模擬前端信號鏈。

編輯:jq

-

濾波器

+關注

關注

160文章

7728瀏覽量

177685 -

寄存器

+關注

關注

31文章

5317瀏覽量

120010 -

adc

+關注

關注

98文章

6438瀏覽量

544099 -

GSPS

+關注

關注

0文章

48瀏覽量

16884

原文標題:如何通過具有內部數字濾波器的高速 ADC 簡化 AFE 濾波

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數模轉換器與數字濾波器的結合應用

ADC3663數字濾波器如何使用呢?

基于FPGA實現FIR數字濾波器

AFE032系數濾波器的設置格式是什么,如何設置?

數字濾波器的實現方法

數字濾波器的原理和應用

iir濾波器和fir濾波器的優勢和特點

數字濾波器是如何工作的

怎么用具有內部數字濾波器的高速ADC簡化AFE濾波呢

怎么用具有內部數字濾波器的高速ADC簡化AFE濾波呢

評論