1 引言

隨著internet技術的發展,在許多領域都引起了飛躍性的變化。嵌入式系統應用領域中一個新的趨勢就是開始在嵌入式設備上集成網絡通信功能,比如網絡監控、網絡數據采集系統等,以便于通過網絡與遠程設備進行信息的交互和增強系統的互連性,僅僅需要一根網線就可以輕輕松松完成系統的互連。

目前市場上的嵌入式處理器的種類很多。altera公司推出了第二代片上可編程嵌入式軟核處理器nios ii,再配上其低成本、高性價比的fpga器件,使得嵌入式系統的開發變得越發方便。再者由于nios ii可配置和fpga器件可編程的特點,與專用硬件相比靈活性得有很大的優勢,從而使得fpga器件在現代電子設計中得到廣泛的應用。

2 系統設計

2.1 nios ii簡介

nios ii嵌入式軟核處理器是altera公司推出的第二代片上可編程的軟核處理器,nios ii是可配置的,用戶可以根據自己的實際需要進行處理器的配置,以達到資源的合理使用,其性能可以超過200dmips。nios ii采用哈佛結構,具有32位指令集,32位數據通道和可配置的指令及數據緩沖,而且支持用戶自定義指令(最多256個)以擴展cpu指令集,提升系統的性能,為可編程片上系統(sopc)設計提供了一套完整的解決方案。nios ii提供了三種內核:nios ii/f是一種高性能的內核,速度最快但消耗的資源最多;nios ii/e是低成本內核,速度最慢消耗的資源最少;nios ii/s是一種性能和成本折中的內核。本設計采用的是nios ii/s內核。

nios ii的優勢就在于其靈活性,可以根據用戶的需求進行靈活的配置和裁剪。基于nios ii軟核的系統設計利用altera公司提供的系統設計工具sopc builder和集成開發環境niosii ide可以進行軟硬件協同設計,很大程度上縮短開發周期,在系統開發的任何階段要都可以很方便的對系統進行修改。fpga器件豐富的邏輯資源,結合nios ii強大的處理能力,將為嵌入式系統設計提供有效的解決方案。

2.2 系統設計

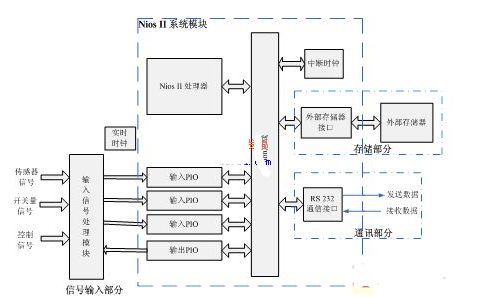

圖 1 系統模塊圖

系統模塊圖如圖1所示。設計采用了altera公司的cyclone ii系列芯片。在其中配置niosii軟核處理器控制外圍設備和協議棧的運行。而且添加了一個計算校驗和的用戶指令(cal_checksum)。

片上ram用作內存運行程序;flash使用了sharp公司的lh28f160s3t-l13a,用來存儲程序和配置信息,系統上電后,先將程序從flash中拷貝到片上ram運行;網絡接口芯片使用smsc公司的10/100m以太網接口控制芯片lan9c111,所以在sopc builder中配置系統時,需要加上altera免費提供的lan9c111接口控制器,嵌入式設備通過lan9c111就可以接入以太網,與網絡上的其他設備進行網絡通信;sdram選用micron公司的mt48lc8m16a2,用來緩存網絡數據,其中sdram控制器使用altera免費提供的sdram控制器。

要提高系統的性能,一方面是提高處理器的處理能力;另一方面就是將用軟件處理比較費時間的模塊使用硬件模塊來實現。經過分析發現,在網絡協議棧的運行過程中,最耗費時間的是校驗和的計算,尤其是當數據量非常大的時候。為此,專門用硬件定制了一個用戶指令校驗和計算指令(cal_checksum),對數據校驗和的計算實現硬件加速,作為一個指令添加到niosii系統中,在協議棧程序中調用來縮短計算校驗和的時間,提高處理速度,達到提升系統性能的目的。

2.3 校驗和計算指令(cal_chkusm)

在上面的分析中已經提到過,在整個協議棧的處理中,最耗時間的就是數據校驗和的計算,特別是當數據長度很大時。所以在設計中將數據校驗和的計算采用硬件模塊來實現,作為niosii的一個用戶自定義指令,以提高校驗和計算的速度。在協議棧的移植過程中,將數據的寬度修改為16位,方便最后將16位校驗和的計算結果添加到相應的域。

校驗和的計算需要很多個時鐘周期才能完成,所以校驗和計算指令使用了multi-cycle用戶指令結構。multi-cycle用戶指令的端口操作有:固定長度和可變長度。因為網絡傳輸的數據長度是不斷變化的,所以校驗和計算指令選擇可變長度操作,這也影響到端口信號的選擇。

multi-cycle用戶指令結構的信號有:reset,clk,clk_en,start,dataa[31:0],datab[31:0],done,result[31:0]。其中除了reset,clk,clk_en三個信號外,其他信號都是可選的,要根據具體的應用選擇。本設計中校驗和計算指令用到了start,dataa[31:0],done,result[31:0]。start信號作為數據有效信號,dataa[31:0]為數據輸入信號,當校驗和計算完成時done信號有效,通知cpu讀取result端口上的數據,因此計算校驗和指令邏輯必須確保當done信號有效時,result端口上的數據有效。

在sopc builder中添加校驗和計算指令,然后重新產生系統,再在quartusii中更新并編譯,在ide的重新編譯一次工程,系統庫中的“system.h”文件包含校驗和計算指令的宏定義如下:

#define alt_ci_cal_chksum_n 0x00000000

#define alt_ci_cal_chksum(a) __builtin_custom_ini(alt_ci_cal_chksum_n,(a))

用戶只需要在源文件中將計算校驗和部分使用上面的宏做相應的替換就可以,對用戶來說這再簡單不過了,就像是調用一個子函數。由此可見,基于niosii軟核處理器開發的嵌入式系統,具有一般嵌入式處理器不能比擬的優勢。

3 軟件設計

協議棧使用了現在在嵌入式應用領域已經很成熟的uip。如果使用altera提供的lwip協議棧,那么就得考慮其在嵌入式操作系統上的移植,這樣無疑會增加系統軟件設計的復雜度和代碼量。

設計的關鍵部分是uip協議棧在nios ii上的移植。針對niosii的特點,將uip做適當的修改,使niosii處理器的處理能力得到充分發揮,提高系統的性能。uip原來是針對8位處理器的,現在將其修改為16位,這樣理論上處理能力就提高了一倍,系統的性能也就提升了一倍。

根據tcp/ip模型結構,數據鏈路層和物理層使用網絡接口芯片lan9c111完成;網絡層和傳輸層協議解析在niosii中由嵌入式tcp/ip協議棧實現;應用層由用戶根據需要編寫。各個模塊合起來共同完成網絡通信功能。

3.1 底層驅動程序的編寫

lan9c111芯片的底層驅動是由altera免費提供的,可以調用這些底層驅動來完成初始化、通信建立、監聽等通信功能。這些底層驅動函數是已經封裝好的,用戶不需要了解其細節就可以編寫網絡通信程序,但是為了進行高級的開發,必須對整個程序的工作機制有一定的了解。

幾個主要的底層驅動函數來完成啟動、復位和初始化phy、以太網packet的收發及中斷處理函數等工作:

static void r_lan91c111_enable():用于啟動芯片工作,使能發送和接收。

int nr_lan91c111_reset():對芯片盡心復位。

static int r_lan91c111_init_phy( ):完成物理層芯片的初始化。

int nr_lan91c111_set_irq():設置芯片的中斷

上層的通信程序調用這些函數實現網絡接口的控制,通信功能的實現以此為基礎。

3.2 通信軟件的實現

通信軟件完成設備之間通信的主要功能,主要是uip協議棧的。傳輸層實現了tcp和udp,這在軟件設計時就需要做不同的考慮,不同的數據傳輸需求要求使用不同的傳輸層協議,比如,實時性要求高的傳輸應用就要求使用無連接的udp協議;對實時性要求不高并且要保證數據傳輸的可靠性的應用使用面向連接的、可靠的tcp協議可以保證傳輸的可靠性。

程序框架如下:

main()

{

netif_init(); // 網絡接口初始化

uip_init(); // 協議棧初始化

arp_table_init(); // arp 表初始化

netconn_new() // 建立新的連接

netconn_bind() // 綁定端口號

netconn_listen() // 偵聽端口

while(1)

{

if (收到數據){

…… // 處理接收的數據

}

else if(發送數據){

…… // 發送數據

}

else

…… // 返回準備下次處理

}

}

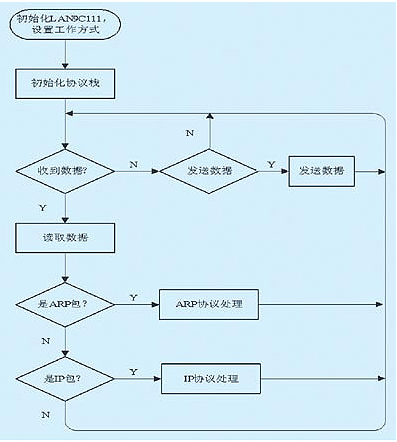

圖2是軟件處理流程。

圖2 通信軟件流程圖

4 結束語

采用niosii進行系統設計,由于sopc builder工具的強大系統開發功能再加上niosii ide集成開發環境,使得系統的設計變得簡單方便、可擴展性強,并且系統軟件的設計與系統設計同時進行,大大縮短開發周期。在該網絡平臺的設計中,使用了嵌入式領域非常成熟的uip,并且是開放源代碼的,所以對uip的移植非常的方便,只是對其進行修改以最大限度的發揮niosii處理器的特點,再加上簡單靈活的用戶自定義指令,對系統性能的提升起到很大作用。這個系統已經在硬件上經過了驗證,可以進行可靠、穩定的網絡通信,并已經應用于一個要求遠程網絡通信功能的數據處理機系統。

責任編輯:gt

-

處理器

+關注

關注

68文章

19159瀏覽量

229115 -

嵌入式

+關注

關注

5068文章

19014瀏覽量

303232 -

數據采集

+關注

關注

38文章

5903瀏覽量

113513

發布評論請先 登錄

相關推薦

Cyclone II FPGA和Nios II嵌入式處理器的優勢

嵌入式軟核Nios Ⅱ串口直接讀寫寄存器有哪些編程方法?

怎么設計集軟核處理器的嵌入式設計平臺?

Nios II入門起步-創建一個嵌入式處理器系統

Nios II嵌入式設計包詳解

基于Nios II的嵌入式開發模式的搭建方案

基于nios ii嵌入式軟核處理器的嵌入式系統設計解決方案

基于nios ii嵌入式軟核處理器的嵌入式系統設計解決方案

評論