“先進封裝”是半導體產業近年來的熱詞之一,也掀起了封裝技術發展史上的第三次技術躍進。有人對它有一個形象比喻“攤大餅不行了,做一下千層餅試試吧”。 為什么這么說?以2.5D、3D封裝為代表的、結合了芯片堆疊和異構封裝等技術的先進封裝,正在為摩爾定律指揮棒下的芯片實現爭取更優方案。<與非網>對話英特爾院士/封裝研究與系統解決方案總監Johanna Swan,就先進封裝的關鍵技術、發展方向等問題進行了深入交流。

為什么需要先進封裝?

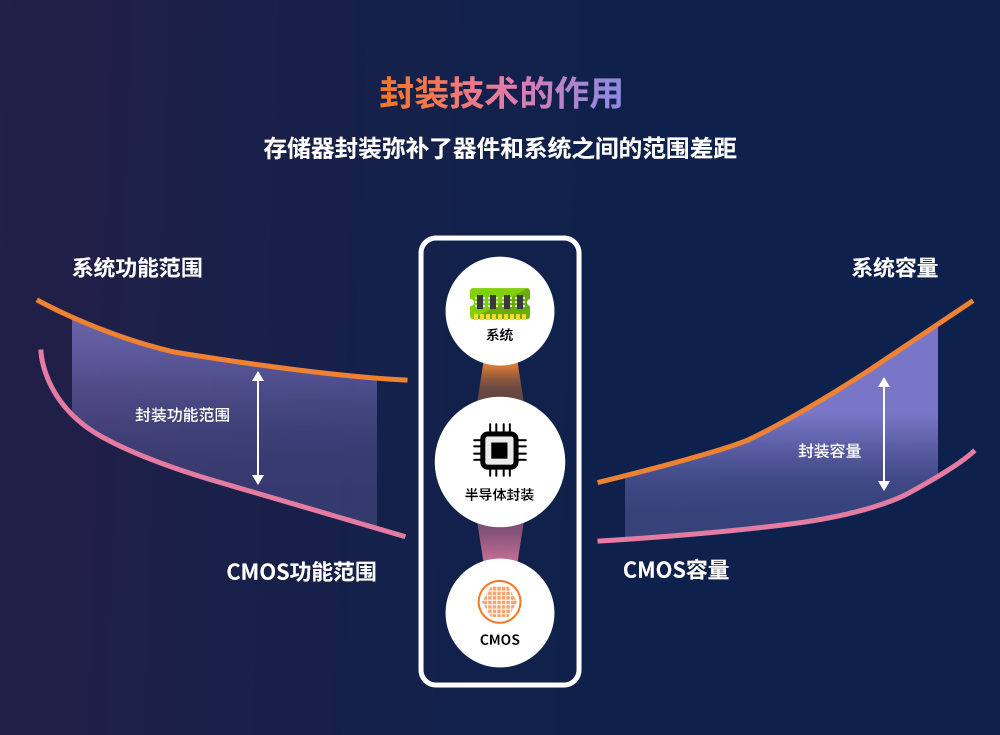

多年來,業界并沒有在先進封裝上投入太多精力,但近年來情況發生了變化。Johanna Swan指出,由于先進封裝技術能夠集成多種制程工藝的計算引擎,實現類似于單晶片的性能,但其平臺范圍遠遠超過單晶片集成的晶片尺寸限制。這些技術將大大提高產品級性能和功效,縮小面積,同時對系統架構進行全面改造。正因如此,先進封裝成為各公司打造差異化優勢的一個重要領域,以及提升性能、提高功率、縮小外形尺寸和提高帶寬的機會。

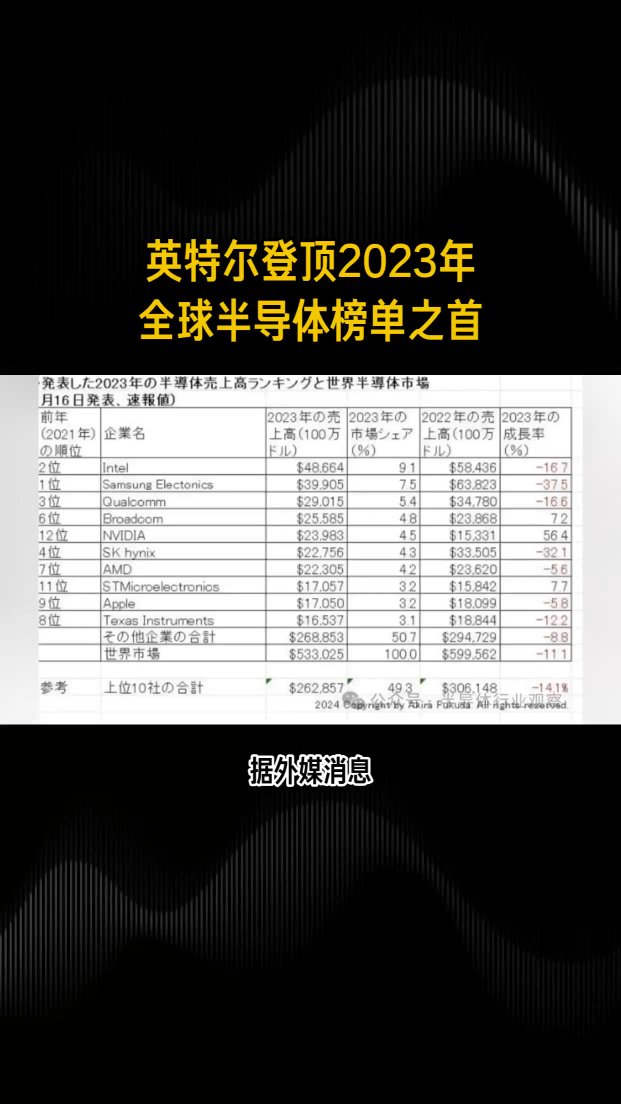

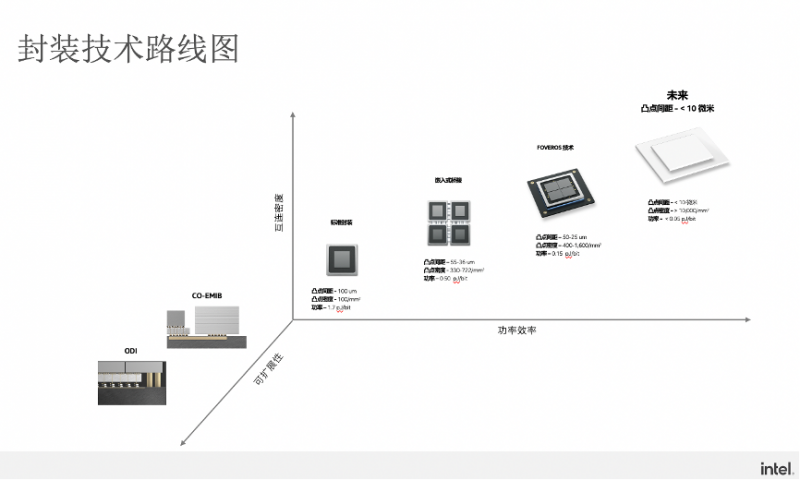

從Intel 的先進封裝技術路線圖可以看出,三大維度是未來方向:X軸代表功率效率,Y軸代表互連密度,Z軸代表可擴展性。

多區塊異構集成提升功率效率

Johanna Swan介紹,單獨IP的異構集成能夠帶來更大量的更小區塊,它們可以大量重復使用,開發時間從單片式集成SoC的3-4年、多晶片2-3年縮短至1年,并且芯片缺陷率進一步降低。這樣一來,便于根據客戶的獨特需求定制產品,滿足產品快速的上市需求。

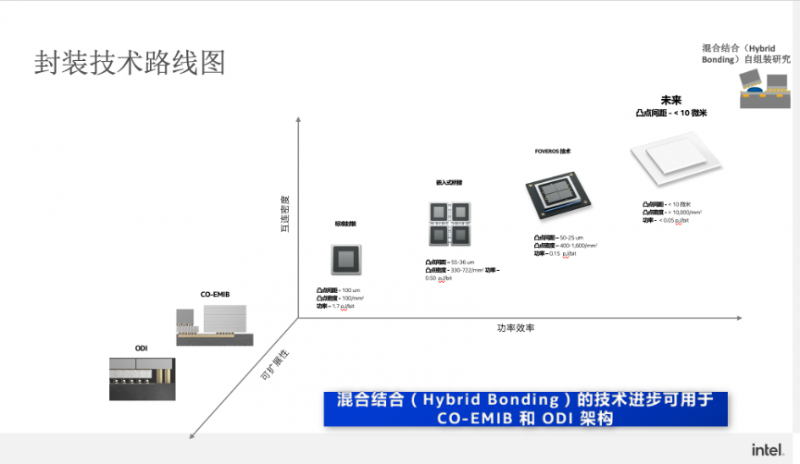

多區塊異構集成能夠解決芯片設計和制造的諸多限制,但與此同時,它所帶來的影響也是深遠的,主要體現在兩方面:一是晶片間互連的微縮從焊接轉到混合結合(Hybrid Bonding),二是大量區塊轉變到按批次組裝的精確放置,這樣又帶來了新的挑戰。

大量區塊如何保持制造流程以相同的速度進行?有更多的晶片需要放置,能否在一次只放置一個晶片的基礎上加快速度?英特爾正在考慮的解決方案是批量組裝/自組裝。

目前,英特爾正在與法國原子能委員會電子與信息技術實驗室(CEA-LETI)合作,研究一次放置多個晶片,進行確定性對齊,并使用超小的晶片,進行快速放置,通過批次組裝,實現拾取更多、并放置更多晶片。Johanna Swan通過一個視頻介紹了自組裝的大概機制:把晶片放在一個能夠將自身恢復到最低能量狀態的位置,這時就不需要設備,只需要讓它足夠接近、試圖達到最低限度的能量狀態時,就會自己組裝、放置到位。在英特爾的封裝技術路線圖中,最新增加了混合結合自組裝研究為未來的方向。

為異構計算而生的混合結合技術

在英特爾的封裝技術路線中,混合結合是一種在相互堆疊的芯片間獲得更密集互連的方法,并且能夠幫助實現更小的外形尺寸。

當前的Foveros技術能實現的是凸點間距 50 微米,這將使每平方毫米有大約 400 個凸點。 由于面積隨著凸點間距在微縮,未來,英特爾希望能縮減到大約 10 微米的凸點間距,達到每平方毫米 10000 個凸點。 這樣,就可以實現更小、更簡單的電路,更低的電容和功耗,實際上可以進行相互疊加,不必做扇入(fan-in)和扇出(fan-out)。

Johanna Swan表示,混合結合可以說是為異構計算而生的,主要有兩大原因:第一,大多數封裝技術中使用的是傳統的“熱壓結合(thermocompression bonding)”技術,而混合結合技術是這一技術的替代品。這項新技術能夠加速實現10微米及以下的凸點間距,提供更高的互連密度、帶寬和更低的功率。

第二,先進的處理系統需要高帶寬和子系統(處理器、片上網絡和處理元件)之間的低功耗互連。傳統上,這些子系統都是單片集成在一個芯片上。隨著異構集成技術的發展,單片集成已經不再適用。擴大芯片之間的互連間距對于異構計算的發展非常重要,而混合結合技術就是解決這一問題的重要技術之一。

混合結合技術已經應用于諸如像圖像傳感器和非易失性存儲器等應用,目前,它的商業應用還局限于晶圓與晶圓之間的結合,并且只能在低能耗的系統中。未來,混合結合會擴展到晶片與晶圓的應用中,以支持計算chiplet、內存chiplet的靈活異構集成,以及未來更高能耗的系統中。

Johanna Swan強調,定制將是下一階段異構集成的重要驅動力。通過將更多不同的節點或 IP 組合,在不同的制程或節點上進行集成,通過這種混合搭配,可以為特定客戶進行深度定制。

可擴展性是先進封裝的重要維度

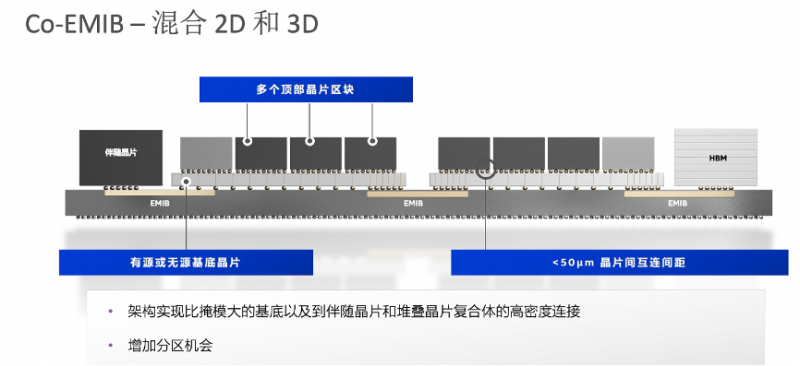

可擴展性是英特爾先進封裝路線的又一個維度,在這個維度上,ODI和CO-EMIB是兩大關鍵技術。

英特爾構建高密度MCP的關鍵基礎技術包括EMIB、Foveros和Co-EMIB。其中,EMIB(嵌入式多芯片互連橋接)2D封裝和Foveros 3D封裝技術利用高密度的互連技術,能夠實現高帶寬、低功耗,并實現相當有競爭力的I/O密度。Co-EMIB則融合了2D和3D,將更高的計算性能和能力連接起來,基本達到單晶片性能。

FOVEROS技術前文已提到過,它作為當前的混合結合技術方式,能夠為密度更高的垂直互連實現更小的尺寸。

那么,ODI又是什么技術呢?它是英特爾全新的全方位的互連技術,能夠為封裝中小芯片之間的全方位互連通信提供靈活性。頂部芯片可以像EMIB技術下與其他小芯片進行水平通信;同時還可以像Foveros技術下,通過硅通孔(TSV)與下面的底部裸片進行垂直通信。這種方法減少了基底晶片中所需的硅通孔數量,為有源晶體管釋放了更多的面積,并優化了裸片的尺寸。

極致的異構集成是半導體封裝未來趨勢

談到先進封裝,小芯片Chiplet是一個必須要探討的話題。Johanna Swan認為,小芯片最重要的事情是它能夠幫助我們獲得越來越小的IP。一旦擁有較小的 IP,它就可以混合在眾多產品中,這可以具有非常高的重用水平,可以根據放入封裝中的產品進行深度定制。

而定制將是實現下一階段異構集成的驅動力,通過將更多不同的節點或 IP 組合,在不同的制程或節點上進行集成, 通過這種混合搭配,可以為特定客戶進行深度定制。

她強調,極致的異構集成是方向,也是封裝技術的未來趨勢。封裝技術將繼續具有縮小尺寸的特征,能夠將越來越小的 IP 和越來越小的區塊集合在一起。歸根結底,我們擁有的發展機會是在每毫米立方體上提供最多的區塊并獲得每毫米立方體最多的功能,所以我們還沒有走到極限。封裝將繼續小型化和縮小尺寸,以便獲取有限體積內的最大功能。

-

異構集成

+關注

關注

0文章

33瀏覽量

1866

發布評論請先 登錄

相關推薦

英特爾擬成立半導體研究中心

消息稱英特爾獲英偉達封裝訂單

英特爾是如何實現玻璃基板的?

英特爾計劃最快2026年量產玻璃基板

英特爾引領未來封裝革命:玻璃基板預計2026年實現量產

英特爾攜手日企加碼先進封裝技術

英特爾加大玻璃基板技術布局力度

Sarcina Technology加入英特爾聯盟

英特爾與聯華電子聯手研發12nm半導體工藝平臺

英特爾實現大規模生產3D封裝技術Foveros

英特爾實現先進半導體封裝技術芯片的大規模生產

英特爾:玻璃基板將推動算力提升

西門子與英特爾共同研發制造先進半導體技術

英特爾院士Johanna Swan:極致的異構集成是半導體封裝未來趨勢

英特爾院士Johanna Swan:極致的異構集成是半導體封裝未來趨勢

評論