什么是AMBA?

現如今,集成電路芯片的規模越來越大。數字IC從基于時序驅動的設計方法,發展到基于IP復用的設計方法,并在SoC設計中得到了廣泛應用。在基于IP復用的SoC設計中,片上總線設計是最關鍵的問題。

因而,業界出現了很多片上總線標準,AMBA是其中之一。

AMBA(Advanced Microcontroller Bus Architecture),是一種開放的協議,主要用于SoC內部和ASIC,用于連接各種功能模塊。簡稱AMBA總線,最早由ARM設計推出。AMBA是相對使用比較廣的片內總線技術,已成為一種流行的工業標準片上結構,如今不單單是ARM專有的。

AMBA總線可以將RISC處理器集成在其他IP芯核和外設中,它是有效連接IP核的“數字膠”,并且是ARM復用策略的重要組件。它不是芯片與外設之間的接口,而是內核與芯片上其他元件進行通信的接口。

首先,讓我們按照它的發布版本來認識一下它。

AMBA版本1規范定義:ASB( Advanced System Bus)與 APB(Advanced Peripheral Bus);

AMBA版本2規范定義:AHB(Advanced High-performance Bus)、ASB( Advanced System Bus)與 APB(Advanced Peripheral Bus);

AMBA版本3規范定義:AXI v1.0(Advanced Extensible Interface)、AHB-Lite v1.0(Advanced High-performance Bus Lite)、 APB v1.0(Advanced Peripheral Bus)與ATB v1.0(Advanced Trace Bus);

AMBA版本4規范定義:ACE(AXI Coherency Extensions)、ACE-Lite(AXI Coherency Extensions Lite)、AXI4(Advanced Extensible Interface 4) 、AXI4-Lite(Advanced Extensible Interface 4 Lite)、AXI4-Stream v1.0(Advanced Extensible Interface 4 Stream)、APB v2.0(Advanced Peripheral Bus)與ATB v1.1(Advanced Trace Bus);

它們之間的區別在哪里呢?讓我們來依次介紹它們。

AHB (Advanced High-performance Bus) 高級高性能總線

APB (Advanced Peripheral Bus) 高級外設總線

ASB (Advanced System Bus) 高級系統總線

AXI (Advanced eXtensible Interface) 高級可拓展接口

其中AXI是在AMBA3.0的協議中增加的,可以用于ARM和FPGA的高速數據交互,剩下的三種是在AMBA2.0協議中定義的總線標準。

AHB介紹

AHB主要用于高性能模塊(如CPU、DMA和DSP等)之間的連接,作為SoC的片上系統總線,它包括以下一些特性:單個時鐘邊沿操作;非三態的實現方式;支持突發傳輸;支持分段傳輸;支持多個主控制器;可配置32位~128位總線寬度;支持字節、半字節和字的傳輸。

AHB 系統由主模塊、從模塊和基礎結構(Infrastructure)3部分組成,整個AHB總線上的傳輸都由主模塊發出,由從模塊負責回應。基礎結構則由仲裁器(arbiter)、主模塊到從模塊的多路器、從模塊到主模塊的多路器、譯碼器(decoder)、虛擬從模塊(dummy Slave)、虛擬主模塊(dummy Master)所組成。其互連結構如下圖所示。

AHB的組成

Master(主控制器):能夠發起讀寫操作,提供地址和控制信號,同一時間只有1個Master會被激活。

Slave(從設備):在給定的地址范圍內對讀寫操作作響應,并對Master返回成功、失敗或者等待等狀態。

Arbiter(仲裁器):負責保證總線上一次只有1個Master在工作。仲裁協議是規定的,但是仲裁算法可以根據應用決定。

Decoder(譯碼器):負責對地址進行解碼,并提供片選信號到各Slave。

AHB基本信號

HADDR:32位系統地址總線;

HTRANS:M指示傳輸狀態,NONSEQ、SEQ、IDLE、BUSY;

HWRITE:傳輸方向1-寫,0-讀;

HSIZE:傳輸單位;

HBURST:傳輸的burst類型;

HWDATA:寫數據總線,從M寫到S;

HREADY:S應答M是否讀寫操作傳輸完成,1-傳輸完成,0-需延長傳輸周期。需要注意的是HREADY作為總線上的信號,它是M和S的輸入;同時每個S需要輸出自HREADY。所以對于S會有兩個HREADY信號,一個來自總線的輸入,一個自己給到多路器的輸出;

HRESP:S應答當前傳輸狀態,OKAY、ERROR、RETRY、SPLIT;

HRDATA:讀數據總線,從S讀到M;

AHB基本傳輸

兩個階段

地址周期(AP),只有一個cycle

數據周期(DP),由HREADY信號決定需要幾個cycle

流水線傳送

先是地址周期,然后是數據周期

AHB突發傳輸與AXI突發傳輸的特點

AHB協議需要一次突發傳輸的所有地址,地址與數據鎖定對應關系,后一次突發傳輸必須在前次傳輸完成才能進行;

AXI只需要一次突發的首地址,可以連續發送多個突發傳輸首地址而無需等待前次突發傳輸完成,并且多個數據可以交錯傳遞,此特征大大提高了總線的利用率;

AHB總線與AXI總線均適用于高性能、高帶寬的SoC系統,但AXI具有更好的靈活性,而且能夠讀寫通道并行發送,互不影響;更重要的是,AXI總線支持亂序傳輸,能夠有效地利用總線的帶寬,平衡內部系統。因此SoC系統中,均以AXI總線為主總線,通過橋連接AHB總線與APB總線,這樣能夠增加SoC系統的靈活性,更加合理地把不同特征IP分配到總線上。

APB介紹

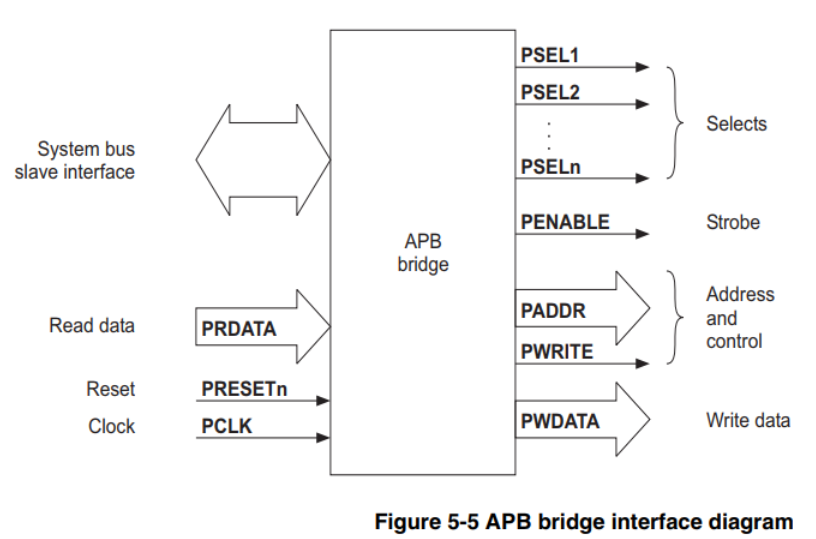

APB主要用于低帶寬的周邊外設之間的連接,例如UART、1284等,它的總線架構不像AHB支持多個主模塊,在APB里面唯一的主模塊就是APB 橋。

APB總線協議包含一個APB橋,它用來將AHB,ASB總線上的控制信號轉化為APB從設備控制器上可用信號。APB總線上所有的外設都是從設備,這些從設備有以下特點:

a 接收有效的地址和控制訪問

b 當APB上的外設處于非活動狀態時,可以將這些外設處于0功耗狀態

c 譯碼器可以通過選通信號,提供輸出時序(非鎖定接口)

d 訪問時可執行數據寫入

其特性包括:兩個時鐘周期傳輸;無需等待周期和回應信號;控制邏輯簡單,只有四個控制信號。APB上的傳輸可以用下圖所示的狀態圖來說明。

1、系統初始化為IDLE狀態,此時沒有傳輸操作,也沒有選中任何從模塊。

2、當有傳輸要進行時,PSELx=1,,PENABLE=0,系統進入SETUP狀態,并只會在SETUP狀態停留一個周期。當PCLK的下一個上升沿到來時,系統進入ENABLE狀態。

3、系統進入ENABLE狀態時,維持之前在SETUP狀態的PADDR、PSEL、PWRITE不變,并將PENABLE置為1。傳輸也只會在ENABLE狀態維持一個周期,在經過SETUP與ENABLE狀態之后就已完成。之后如果沒有傳輸要進行,就進入IDLE狀態等待;如果有連續的傳輸,則進入SETUP狀態。

APB讀寫傳輸

一次傳輸過程中,psel保持兩個周期不變,且在此期間,paddr、pwrite也保持不變,penable在psel有效的第2個周期有效。為了降低功耗,地址信號和寫信號將在傳輸后不再改變,直到發生下一次傳輸。協議僅要求使能信號有個規則的跳變,背靠背傳輸情況下,選擇和寫信號可能有小跳變。

讀傳輸時各信號的時序和寫時一樣,在讀傳輸中,從機必須在ENABLE周期提供數據,數據在ENABLE末尾的時鐘上升沿被采樣。

ASB介紹

AMBA2.0 規范中的ASB總線適用于連接高性能的系統模塊。它的讀/寫數據總線采用的是同一條雙向數據總線,可以在某些高速且不必要使用AHB 總線的場合作為系統總線,可以支持處理器、片上存儲器和片外處理器接口及與低功耗外部宏單元之間的連接。

ASB支持高性能處理器,片上內存,片外內存提供接口和慢速外設。高性能,數據傳輸,多總線主控制器,突發連續傳輸。ASB總線是位于APB總線架構之上的用于高性能的總線協議,它有如下特點:

a 突發連續傳輸

b 單管道數據傳輸

c 多總線主控制器

AXI介紹

AXI是一種總線協議,該協議是ARM公司提出的AMBA3.0中最重要的部分,是一種面向高性能、高帶寬、低延遲的片內總線。AMBA4.0將其修改升級為AXI4.0。

AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-stream。

AXI4.0-lite是AXI的簡化版本,ACE4.0 是AXI緩存一致性擴展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA進行以數據為主導的大量數據的傳輸應用。

AXI協議是基于burst的傳輸,并且定義了5個獨立的傳輸通道:讀地址通道、讀數據通道、寫地址通道、寫數據通道、寫響應通道。

地址通道攜帶控制消息,用于描述被傳輸的數據屬性;數據傳輸使用寫通道來實現master到slave的傳輸,slave使用寫響應通道來完成一次寫傳輸;讀通道用來實現數據從slave到master的傳輸。

由若干master設備和slave設備通過一些形式的interconnect組成的典型的系統如下圖所示,AXI總線即可作為其中的Interface,實現數據通信。

AXI的性能

AXI總線是一種多通道傳輸總線,將地址、讀數據、寫數據、握手信號在不同的通道中發送,不同的訪問之間順序可以打亂,用BUSID來表示各個訪問的歸屬。主設備在沒有得到返回數據的情況下可發出多個讀寫操作。讀回的數據順序可以被打亂,同時還支持非對齊數據訪問。

AXI總線還定義了在進出低功耗節電模式前后的握手協議。規定如何通知進入低功耗模式,何時關斷時鐘,何時開啟時鐘,如何退出低功耗模式。這使得所有IP在進行功耗控制的設計時,有據可依,容易集成在統一的系統中。

AXI的特點

單向通道體系結構-信息流只以單方向傳輸,簡化時鐘域間的橋接,減少門數量。當信號經過復雜的片上系統時,減少延時。

支持多項數據交換-通過并行執行猝發操作,極大地提高了數據吞吐能力,可在更短的時間內完成任務,在滿足高性能要求的同時,又減少了功耗。

獨立的地址和數據通道-地址和數據通道分開,能對每一個通道進行單獨優化,可以根據需要控制時序通道,將時鐘頻率提到最高,并將延時降到最低。

增強的靈活性-AXI技術擁有對稱的主從接口,無論在點對點或在多層系統中,都能十分方便地使用AXI技術。

AXI讀寫數據

寫入數據

1、master通過寫地址通道發出寫入請求;

2、master通過寫數據通道發送寫入的數據;

3、slave在完成寫入動作后(寫數據通道last),通過寫響應通道發回確認信息。

讀取數據

1、master通過讀地址通道發出讀取請求;

2、slave通過讀數據通道將讀取的數據傳給master。

握手過程

5個傳輸通道均使用VALID/READY信號對傳輸過程的地址、數據、控制信號進行握手。使用雙向握手機制,傳輸僅僅發生在VALID、READY同時有效的時候。

通道順序

AXI協議要求通道間滿足如下關系:

-寫響應必須跟隨最后一次burst的的寫傳輸

-讀數據必須跟隨數據對應的地址

-通道握手信號需要確認一些依賴關系

通道握手信號的依賴關系

為防止死鎖,通道握手信號需要遵循一定的依賴關系。

1、VALID信號不能依賴READY信號。

2、AXI接口可以等到檢測到VALID才斷言對應的READY,也可以檢測到VALID之前就斷言READY。

單箭頭指向的信號能在箭頭起點信號之前或之后斷言;雙箭頭指向的信號必須在箭頭起點信號斷言之后斷言。

突發傳輸機制

突發傳輸,一般也稱為數據突發,其在通信領域中一般指在短時間內進行相對高帶寬的數據傳輸。

AXI 總線中的突發傳輸(Burst Transaction)是指,在地址總線上進行一次地址傳輸后,進行多次數據傳輸。第一次地址傳輸中的地址作為起始地址,根據突發傳輸類型的不同,后續數據的存儲地址在起始地址的基礎上遞增(INCR 模式);或者首先遞增,到達上限地址后回到起始地址,繼續遞增(WRAP 模式);又或者后續數據都將不斷寫入起始地址,刷新起始地址上的數據。(FIXED 模式)

突發傳輸的流程

a.主機在讀/寫地址通道寫入起始地址(AxADDR)以及突發傳輸的長度(AxLEN)、寬度(AxSIZE)、類型(AxBURST)等信息;

b.從機將在起始地址開始,依次接收主機傳輸的寫數據,或者讀取連續地址上的數據,作為讀數據傳輸給主機。

突發傳輸長度

突發傳輸長度(burst length),指一次突發傳輸中包含的數據傳輸(transfer)數量,在協議中使用AxLEN信號控制(AWLEN和ARLEN)。

突發傳輸長度在不同的模式下有一些限制,包括:

a.對于WRAP模式,突發傳輸長度僅能為2,4,8,16

b.在一次突發傳輸中,地址不能跨越4KB地址邊界

c.一次突發傳輸不能在完成所有數據傳輸前提前結束

突發傳輸寬度

突發傳輸寬度(burst size),指傳輸中的數據位寬,具體地,是每周期傳輸數據的字節數量,在協議中使用AxSIZE信號控制(AWSIZE和ARSIZE)。

突發傳輸數據寬度不能超過數據總線本身的位寬。而當數據總線位寬大于突發傳輸寬度時,將根據協議的相關規定,將數據在部分數據線上傳輸。

突發傳輸類型

突發傳輸類型(burst type),類型共有 3 種,分別為 FIXED,INCR 以及 WRAP。使用 2 位二進制表示,在協議中使用 AxBURST信號控制(AWBURST和ARBURST)。

FIXED:突發傳輸過程中地址固定,用于FIFO訪問。

INCR:增量突發,傳輸過程中,地址遞增。增加量取決AxSIZE的值。

WRAP:回環突發,和增量突發類似,但會在特定高地址的邊界處回到低地址處。回環突發的長度只能是2,4,8,16次傳輸,傳輸首地址和每次傳輸的大小對齊。最低的地址整個傳輸的數據大小對齊。回環邊界等于(AxSIZE*AxLEN)。

AHB、AXI、APB的區別與聯系

AHB:主要是針對高效率、高頻寬及快速系統模塊所設計的總線,它可以連接如微處理器、芯片上或芯片外的內存模塊和DMA等高效率模塊。

APB:主要用在低速且低功率的外圍,可針對外圍設備作功率消耗及復雜接口的最佳化。APB在AHB和低帶寬的外圍設備之間提供了通信的橋梁,所以APB是AHB或ASB的二級拓展總線。

AXI:高速度、高帶寬,管道化互聯,單向通道,只需要首地址,讀寫并行,支持亂序,支持非對齊操作,有效支持初始延遲較高的外設,連線非常多。

AMBA的應用

大多數掛在總線上的模塊(包括處理器)只是單一屬性的功能模塊:主模塊或者從模塊。主模塊是向從模塊發出讀寫操作的模塊,如CPU,DSP等;從模塊是接受命令并做出反應的模塊,如片上的RAM,AHB/APB 橋等。

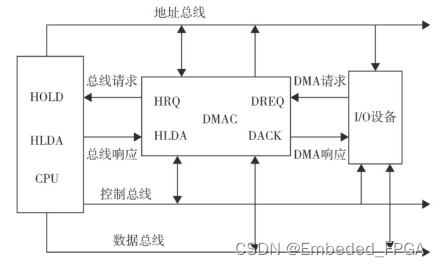

另外,還有一些模塊同時具有兩種屬性,例如直接存儲器存取(DMA)在被編程時是從模塊,但在系統讀傳輸數據時必須是主模塊。如果總線上存在多個主模塊,就需要仲裁器來決定如何控制各種主模塊對總線的訪問。

雖然仲裁規范是AMBA總線規范中的一部分,但具體使用的算法由RTL設計工程師決定,其中兩個最常用的算法是固定優先級算法和循環制算法。AHB總線上最多可以有16個主模塊和任意多個從模塊,如果主模塊數目大于16,則需再加一層結構(具體參閱ARM公司推出的Multi-layer AHB規范)。APB 橋既是APB總線上唯一的主模塊,也是AHB系統總線上的從模塊。其主要功能是鎖存來自AHB系統總線的地址、數據和控制信號,并提供二級譯碼以產生APB外圍設備的選擇信號,從而實現AHB協議到APB協議的轉換。

AMBA AHB循環級建模標準是完全公開和免費的。

AMBA總線的仲裁

如果總線上存在多個主模塊,就需要仲裁器來決定如何控制各種主模塊對總線的訪問。

而對于AMBA總線仲裁的相關應用,我們來看一個實例,有關于對應的優先順序的設置:

即,對應的ARB寄存器,可以設置,AHB總線上面的數據的優先級

ARMI:ARM的指令

ARMD:ARM的數據

DMAC:DMA控制器

BRIDGE:AHB/APB 橋(Bridge)

可以通過配置,決定他們的優先級順序。

編輯:jq

-

集成電路

+關注

關注

5381文章

11381瀏覽量

360850 -

ARM

+關注

關注

134文章

9045瀏覽量

366807 -

IC

+關注

關注

36文章

5897瀏覽量

175229 -

AMBA

+關注

關注

0文章

68瀏覽量

14951

發布評論請先 登錄

相關推薦

AMBA AXI4接口協議概述

usb主機控制器位于ahp總線上嗎

AMBA總線協議的基本原理和應用場景

SoC設計中總線協議AXI4與AXI3的主要區別詳解

集成電路開發之寄存器工具介紹

SOC設計中APB協議總線的工作原理

漫談AMBA總線-AXI4協議的基本介紹

AMBA總線中APB slave設計介紹

AMBA總線中APB interconnect的介紹

AHB與DMA詳細解讀

深度解讀AMBA、AHB、APB、AXI總線介紹及對比

深度解讀AMBA、AHB、APB、AXI總線介紹及對比

評論