賽靈思近日宣布推出 Vivado ML 版,這是業內首個基于機器學習(ML )優化算法以及先進的面向團隊協作的設計流程打造的 FPGA EDA 工具套件,可以顯著節省設計時間與成本,與目前的 Vivado HLx 版本相比,Vivado ML 版將復雜設計的編譯時間縮短了 5 倍,同時還提供了突破性的平均達 10% 的結果質量( QoR )提升。

Vivado ML 概述

1、基于 ML 的設計優化

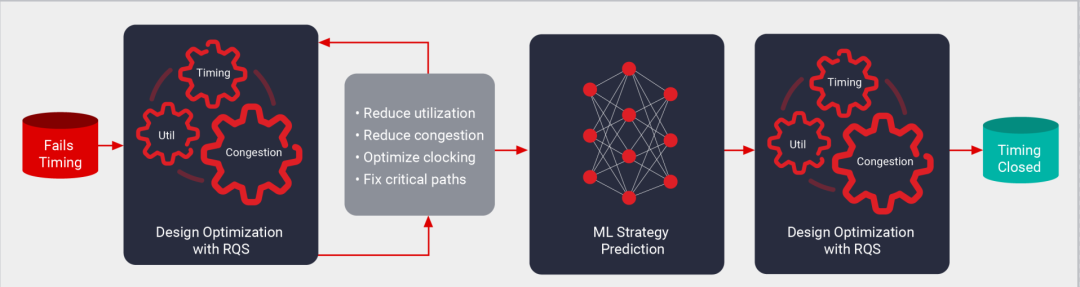

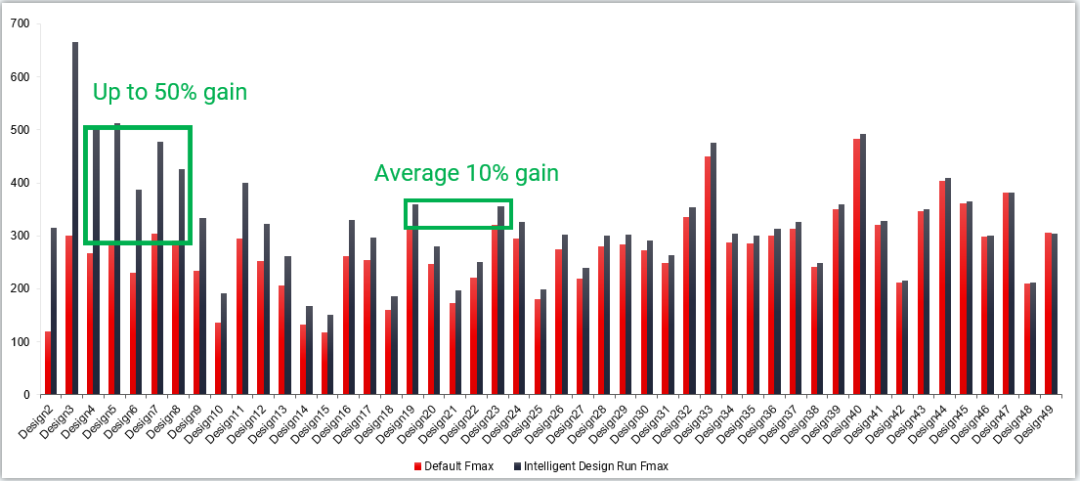

加速設計收斂

與當前的 Vivado HLx 版本相比,全新w Vivado ML 版本在復雜設計上實現了高達 50%(平均 10%)的突破性結果質量 (QoR) 提升。

基于 ML 的邏輯優化、擁塞估計、延遲估計和智能設計運行等新功能和算法有助于自動化策略以減少時序收斂迭代。

2、協同設計環境

提升生產力

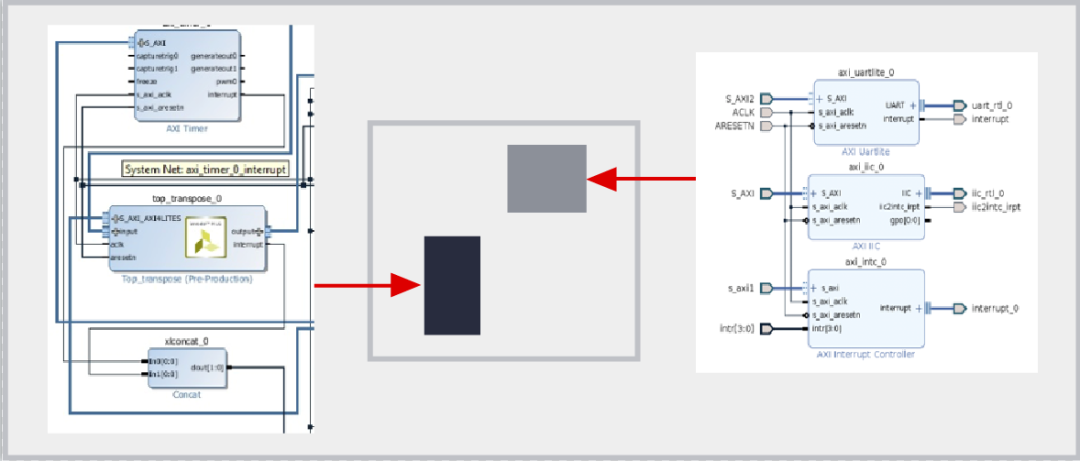

使用 Vivado IP Integrator 改進協作設計,使用全新的“塊設計容器”功能實現模塊化設計。

推廣基于團隊的設計方法,并允許采用分而治之的策略來處理具有多站點協作的大型設計。

3、全新高級 DFX 功能

編譯時間減少

Xilinx 引入了抽象 Shell 的概念,允許用戶在系統中定義多個模塊以進行增量和并行編譯。

與傳統的完整系統編譯相比,此功能可將平均編譯時間縮短 5 倍,最多可縮短 17 倍。

Abstract Shell 通過將設計細節隱藏在模塊之外來幫助保護客戶的 IP

功能介紹

1、高層次設計

Vivado IP Integrator 可提供基于 Tcl、設計期正確的圖形化設計開發流程。設計團隊在接口層面上工作,能快速組裝復雜系統,充分利用 Vitis HLS、Vitis Model Composer、Xilinx IP、聯盟成員 IP 和自己的 IP。通過利用全新提升的 Vivado IPI 和 HLS 的完美組合,客戶能將開發成本相對于采用 RTL 方式而言節約高達 15 倍。

2、驗證

應對當前復雜器件的驗證挑戰,需要在各種設計層面上應用大量工具及技術。Vivado 設計套件在緊密結合的環境中提供這些工具和技術,從而可加速模塊及芯片級設計的驗證。

3、實現

具有高級機器學習算法的 Vivado ML 設計套件提供了在運行時和性能方面具有顯著優勢的最佳實現工具。憑借用于綜合、布局、布線和物理優化的一流編譯工具以及 Xilinx 編譯方法建議,設計者可以加快設計周期的實現階段。

平臺版本

Vivado ML 標準版

Vivado ML 的器件受限免費版本。

Vivado ML 企業版

包括對所有 Xilinx 器件的支持。

文章出處:【微信公眾號:FPGA開發圈】

責任編輯:gt

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601807 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131162 -

機器學習

+關注

關注

66文章

8377瀏覽量

132406

原文標題:Vivado ML 版,讓設計更智能化

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

優化 FPGA HLS 設計

思爾芯賽題正式發布,邀你共戰EDA精英挑戰賽!

賽思快訊 | 發展新質生產力問道賽思?賽思如何下好“創新棋”?

中科愛畢賽思紅外光電探測技術,打破高端市場“卡脖子”困境

安賽思半導體與新加坡三福半導體達成戰略合作

是德科技推出AI數據中心測試平臺旨在加速AI/ML網絡驗證和優化的創新

易靈思RAM使用--Update3

賽靈思Vivado ML版優化應用設計

賽靈思Vivado ML版優化應用設計

評論