上上期我們提到了buck電路的開(kāi)關(guān)的振鈴波形,本質(zhì)原因是LC的阻尼振蕩。文章偏理論,那BUCK到底是怎么產(chǎn)生尖峰振蕩呢?

問(wèn)題

本期主要分析以下這兩個(gè)問(wèn)題:

1、死區(qū)時(shí)間是什么?這里有個(gè)小臺(tái)階是什么情況?

2、上下尖峰振蕩是如何產(chǎn)生的?跟哪些因素有關(guān)?

理想的BUCK的SW波形

我們由淺入深,一步一步來(lái),先看理想的開(kāi)關(guān)SW波形—沒(méi)有尖峰電壓的波形。

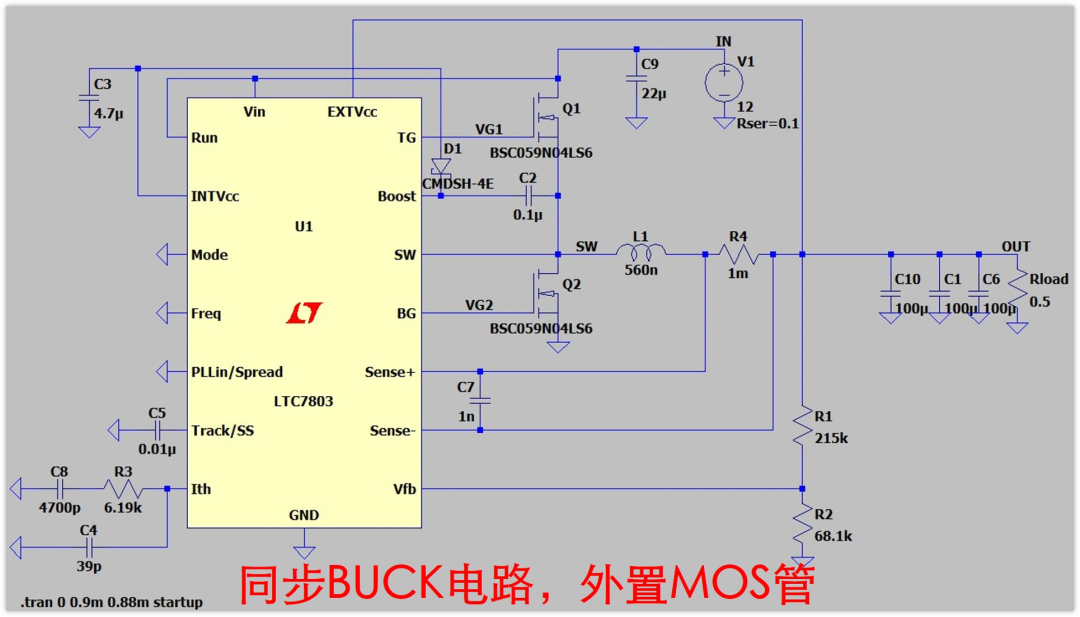

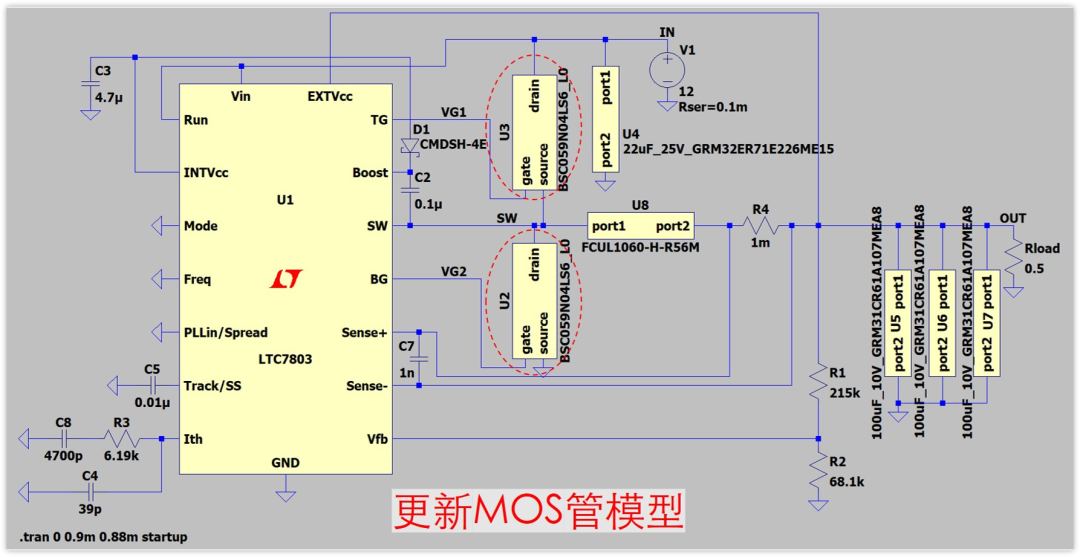

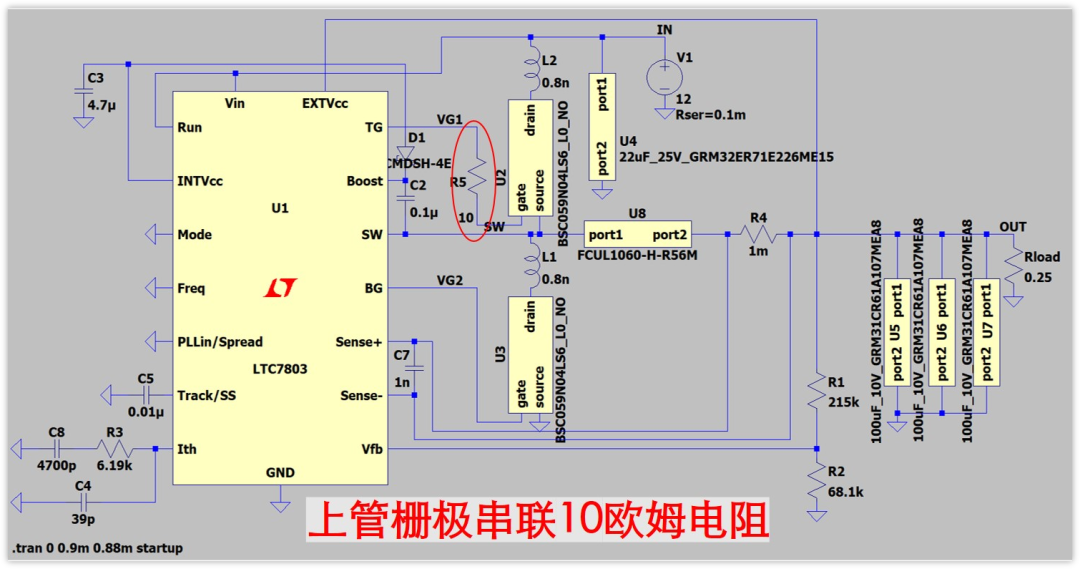

為了能更好的看buck電路各個(gè)點(diǎn)的電壓電流情況,我選的電源芯片是沒(méi)有內(nèi)部集成開(kāi)關(guān)管的,使用的是外置的MOS管,電源芯片型號(hào)為L(zhǎng)TC7803。

如果對(duì)BUCK的拓?fù)溆辛私獾脑挘厦孢@個(gè)電路一眼應(yīng)該就看明白了,是一個(gè)同步buck,沒(méi)有用到二極管。

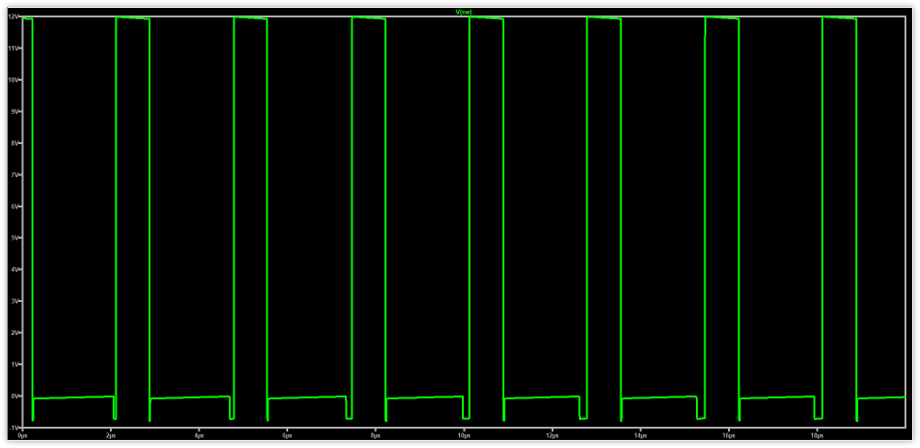

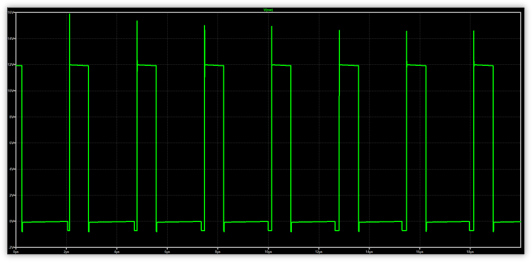

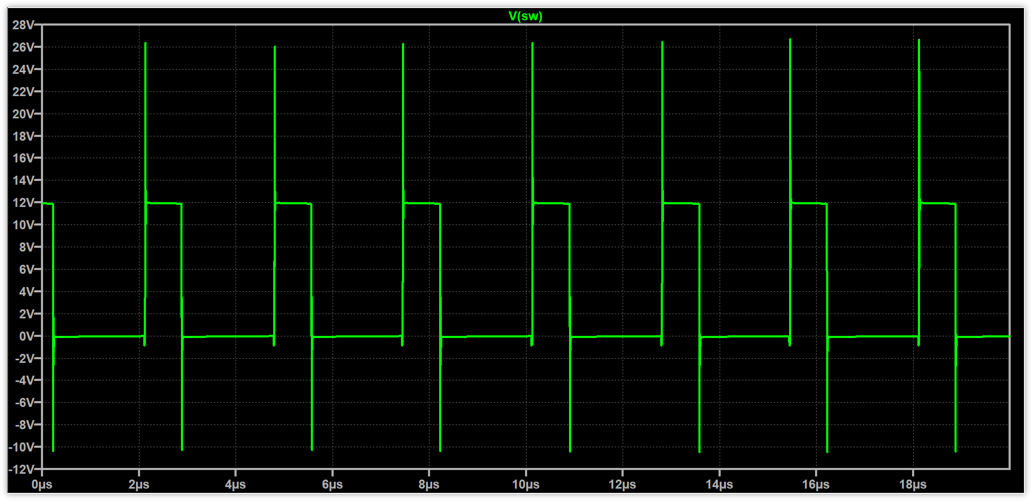

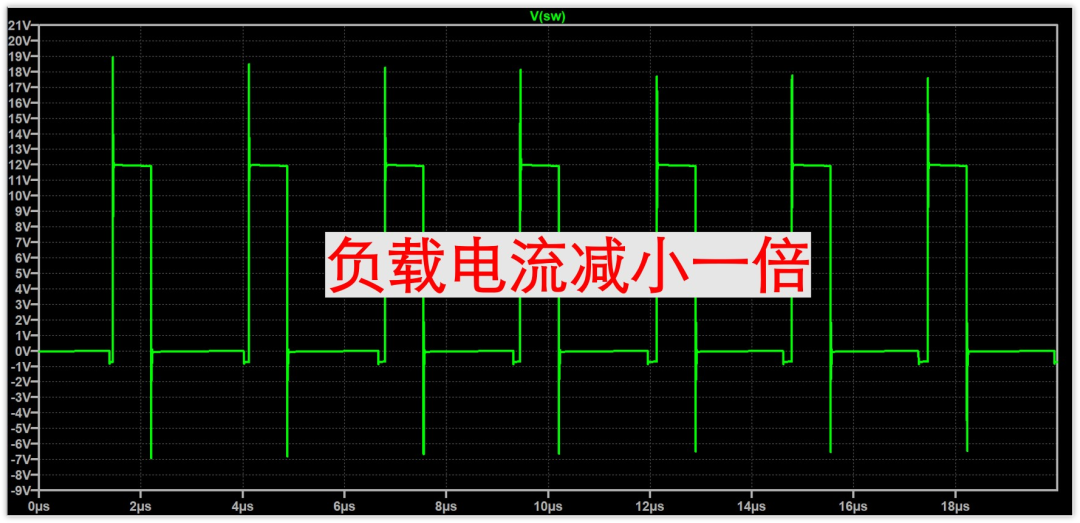

這個(gè)電路的輸入是12V,輸出是3.3V,負(fù)載等于0.5Ω,BUCK工作在連續(xù)模式。現(xiàn)在我們直接看電感前面SW的波形,如下圖:

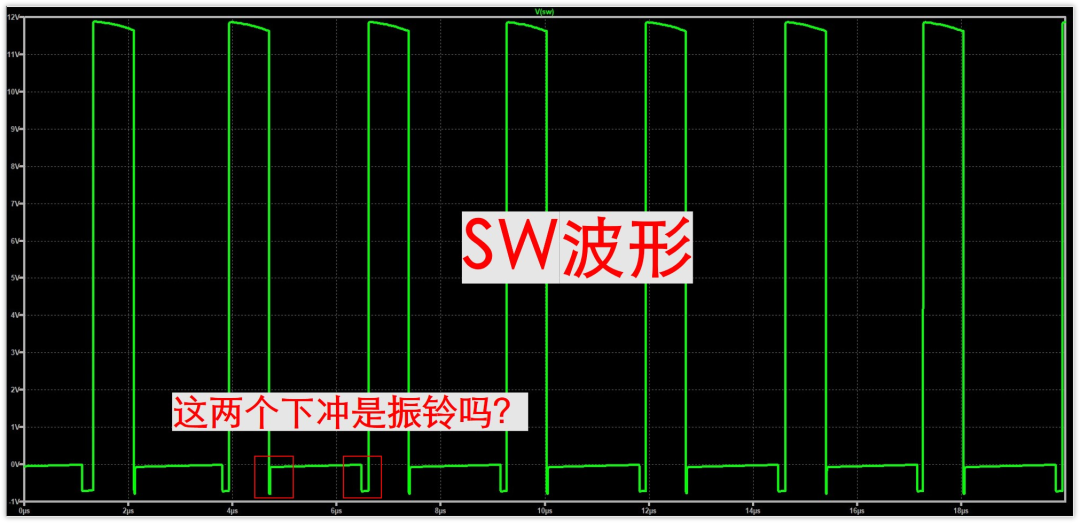

我們可以看到,這個(gè)波形很漂亮,看著就是非常好的矩形波,沒(méi)有向上的振鈴。

唯一美中不足的是,在底部有下沖。

這是怎么回事呢?是向下的振鈴嗎?

如果仔細(xì)觀察的話,這個(gè)下沖的幅度大概是0.7V左右,也沒(méi)有出現(xiàn)振蕩波形,如此,猜測(cè)應(yīng)該是二極管的導(dǎo)通電壓。

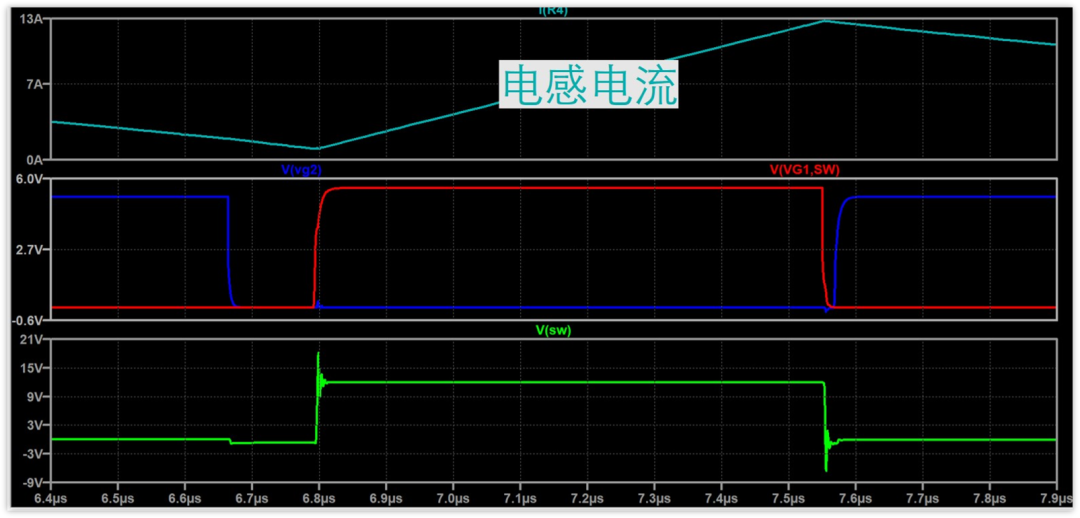

為了驗(yàn)證這個(gè)想法,我們對(duì)比兩個(gè)MOS管的驅(qū)動(dòng)電壓Vgs,然后看看電感的電流。

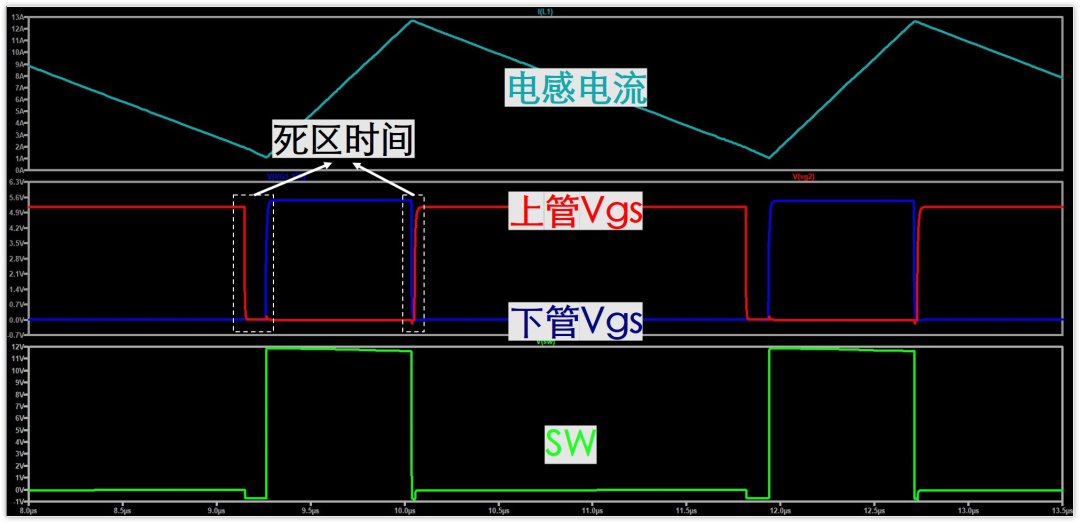

從上圖,很容易看到,電感的電流一直都是正的(大于0),也就是電感的電流總是向負(fù)載那個(gè)方向流動(dòng)的,并不會(huì)反向,并且,最小的電流也有2A。

但是呢,如果我們對(duì)比兩個(gè)NMOS管的Vgs,會(huì)發(fā)現(xiàn)有同時(shí)為低的情況,也就是說(shuō)兩個(gè)管子同時(shí)都不導(dǎo)通,這一段時(shí)間就是死區(qū)時(shí)間。

為啥會(huì)有死區(qū)時(shí)間呢?

我們通常分析BUCK拓?fù)浣Y(jié)構(gòu)的時(shí)候,經(jīng)常會(huì)認(rèn)為只有一個(gè)管子導(dǎo)通,要不上管,要不下管(連續(xù)模式)。

而實(shí)際MOS管在切換導(dǎo)通狀態(tài)的時(shí)候,MOS管必然會(huì)存在中間態(tài)-半導(dǎo)導(dǎo)通狀態(tài),半導(dǎo)通時(shí)的MOS管的導(dǎo)通電阻是變化的,很大到接近于0,如果兩個(gè)管子同步切換,那么必然會(huì)出現(xiàn)都處于半導(dǎo)通狀態(tài)的情況,回路電阻很大,這樣功率電感電流就沒(méi)法續(xù)流了。

所以呢,必須要考慮切換時(shí)其它的續(xù)流方式。

不僅如此,如果兩個(gè)管子同步切換,稍微有一點(diǎn)不同步的話,那么肯定會(huì)存在兩個(gè)管子都導(dǎo)通的情況,這樣的話就相當(dāng)于電源直接對(duì)地短路了,這簡(jiǎn)直是災(zāi)難。

現(xiàn)在看來(lái),保險(xiǎn)起見(jiàn),干脆將時(shí)間錯(cuò)開(kāi),每次切換的時(shí)候,讓兩個(gè)管子都不導(dǎo)通一段時(shí)間,這樣就絕不會(huì)出現(xiàn)兩個(gè)管子同時(shí)導(dǎo)通了。

但是這樣的話,我們必須想辦法給功率電感續(xù)流。

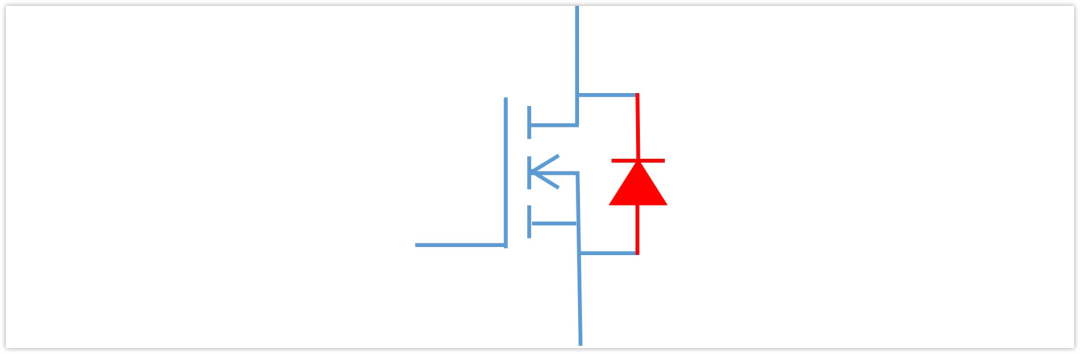

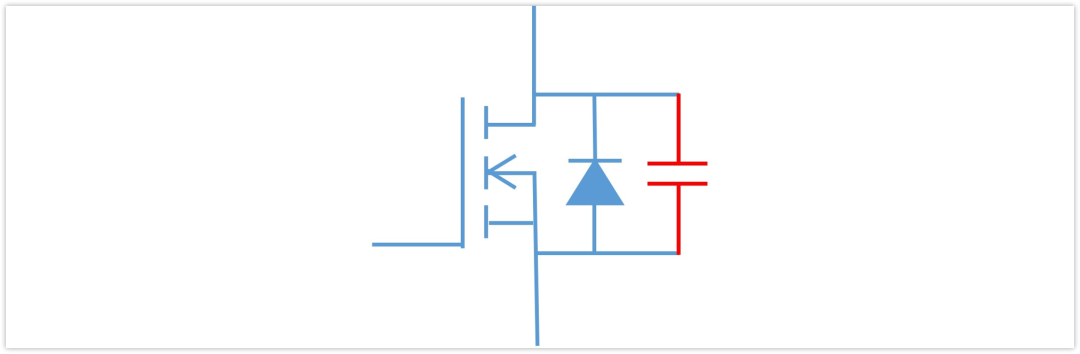

這個(gè)續(xù)流的方式很容易想到,MOS管是有體二極管的。在兩個(gè)管子都關(guān)閉的時(shí)候,可以通過(guò)體二極管的續(xù)流。

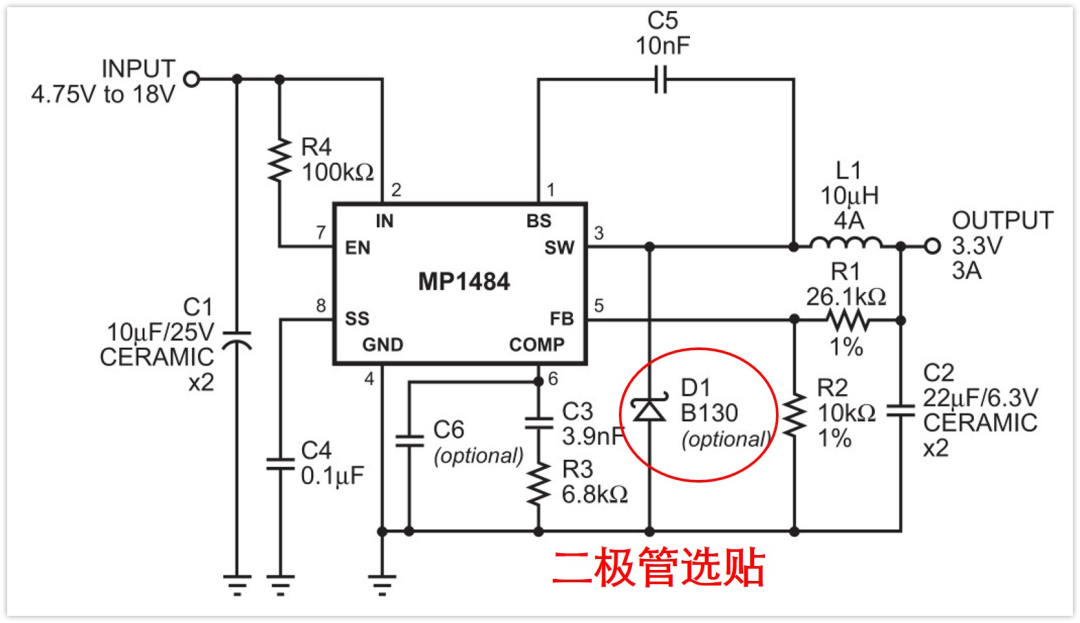

寫(xiě)到這里,我突然想起來(lái),有些同步的DCDC芯片推薦的電路,會(huì)有二極管選貼一說(shuō)(二極管可要可不要),比如這個(gè)MP1484的D1。

看到這個(gè)圖不要以為這是一個(gè)異步buck,二極管D1是選貼的。

那這個(gè)二極管有什么用呢?

其實(shí)MP1484芯片手冊(cè)里面也有寫(xiě)。

寫(xiě)的很明白了:

在上管和下管轉(zhuǎn)換期間,電感電流主要從下管的體二極管流過(guò)。體二極管的導(dǎo)通電壓比較高,可選用一個(gè)肖特基二極管并在SW和GND之間,以此來(lái)提升整體效率。

這個(gè)器件是硅芯片,那么顯然,體二極管也就是硅二極管,導(dǎo)通電壓自然要比肖特基二極管更高,因此使用肖特基二極管可以降低功耗。

不過(guò)我想這個(gè)降幅應(yīng)該很是很有限的,因?yàn)樯舷鹿苻D(zhuǎn)換期間的時(shí)間非常短暫,只占開(kāi)關(guān)周期很短的一部分時(shí)間,并且就算用了肖特基二極管,也還是有導(dǎo)通電壓,只是比之前小一點(diǎn)而已。

以上是仿真波形,那實(shí)際電路也會(huì)在開(kāi)關(guān)切換時(shí)有個(gè)0.7V左右的“下沖”嗎?

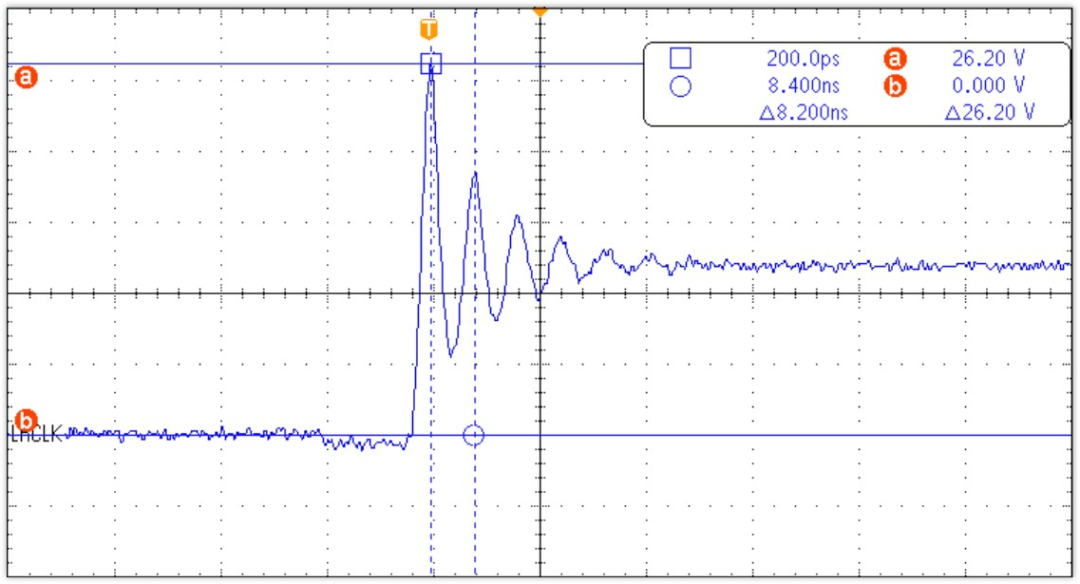

我手頭正好有MP1484的板子,于是我用示波器測(cè)試了一下,波形如下圖:

奇怪的是,只在下降沿時(shí)出現(xiàn)了一個(gè)0.7V的下沖臺(tái)階,在上升沿時(shí)底部并沒(méi)有向下的“下沖”臺(tái)階。

這是為什么呢?難道上升沿時(shí)上下管切換并沒(méi)有死區(qū)時(shí)間?

為此,我猜測(cè)可能是負(fù)載電流的太小,并且上升沿時(shí)的死區(qū)時(shí)間比較短,而MOS管的D和S是有寄生電容的。

在開(kāi)關(guān)切換之前,下管是導(dǎo)通的,等于接地,寄生電容兩端電壓約為0V,體二極管也是0V。

在切換時(shí),體二極管剛開(kāi)始也沒(méi)有導(dǎo)通,所以是先對(duì)電容進(jìn)行放電才能讓電壓變?yōu)?0.7V,此時(shí)二極管才會(huì)導(dǎo)通。如果死區(qū)時(shí)間太短,或者電感需要續(xù)的電流很小,那么可能在死區(qū)時(shí)間結(jié)束,電容都能提供足夠的續(xù)流,電壓下降很小。

為了印證我的猜測(cè),因?yàn)闆](méi)法加長(zhǎng)死區(qū)時(shí)間,所以我改變了負(fù)載電阻,加大了負(fù)載電流,目的是為了讓寄生電容提供不了足夠的續(xù)流。

再次測(cè)試了一下,確實(shí)就能量到上升沿的死區(qū)時(shí)間了,如下圖所示

可以看到,上升沿也有一個(gè)向下的冒尖,時(shí)間非常短,拉開(kāi)示波器時(shí)間尺度發(fā)現(xiàn)大概是13ns(就不截圖了)。而下降沿向下的冒尖時(shí)間大概是100ns。也就是說(shuō)這個(gè)MP1484的兩個(gè)死區(qū)時(shí)間分別是13ns和100ns。

從前面的仿真波形可以看到,在開(kāi)關(guān)管切換時(shí),死區(qū)時(shí)間會(huì)導(dǎo)致SW處出現(xiàn)0.7V左右的負(fù)壓臺(tái)階,但是完全看不到尖峰。

而實(shí)測(cè)波形是有尖峰的,那這個(gè)尖峰是如何產(chǎn)生的呢?它的大小與哪些因素有關(guān)系呢?

我們接著看。

當(dāng)然,我上圖中實(shí)測(cè)的尖峰也很小,這是因?yàn)槲易龅陌遄右呀?jīng)盡量?jī)?yōu)化PCB了,所以尖峰效果不明顯,如果板子做得差的話,可能是下面這樣的。

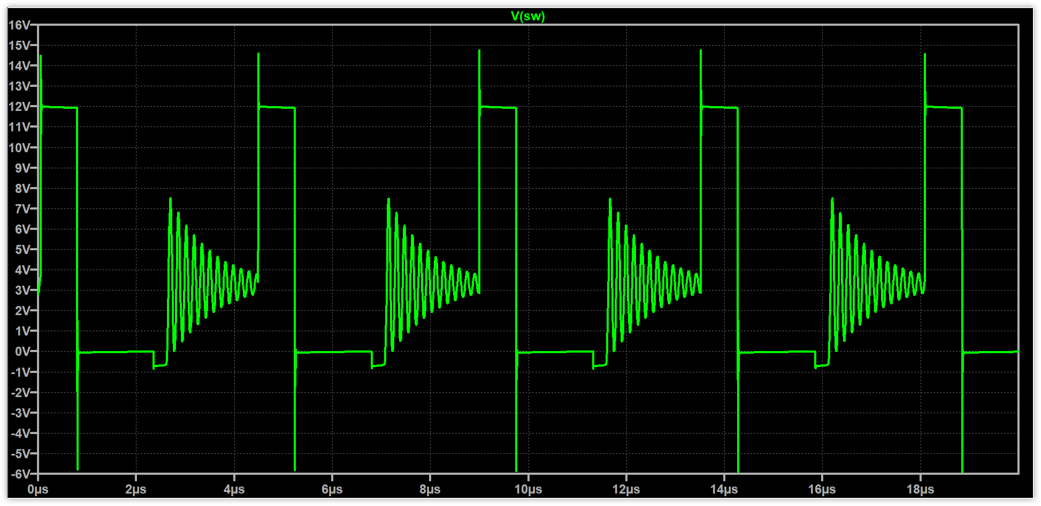

拉開(kāi)可以看到是高頻振蕩

我們知道,這個(gè)尖峰過(guò)高,意味著存在高頻的劇烈變化的電流,會(huì)產(chǎn)生EMI的問(wèn)題,同時(shí),如果太高的話,可能會(huì)擊穿內(nèi)部開(kāi)關(guān)管。

如果我們想要降低尖峰,最好的方式莫過(guò)于知道這個(gè)尖峰是如何產(chǎn)生的,然后對(duì)癥下藥。

BUCK的SW波形尖峰如何產(chǎn)生

首先一個(gè)問(wèn)題,仿真沒(méi)有出現(xiàn)尖峰,是什么原因呢?

是因?yàn)槠骷P筒粶?zhǔn)確嗎?也許吧,仿真使用到了集成芯片,NMOS管,電感和電容,那么如何確認(rèn)這個(gè)問(wèn)題呢?

更新功率電感模型

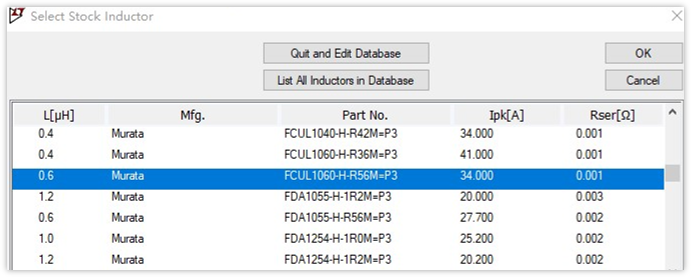

功率電感FCUL1060-H-R56M我使用的是LTspice庫(kù)里面自帶的。

里面的寄生參數(shù)很少,我只看到了Rser,寄生電容都看不到,因此我有理由懷疑這個(gè)模型不準(zhǔn)確。

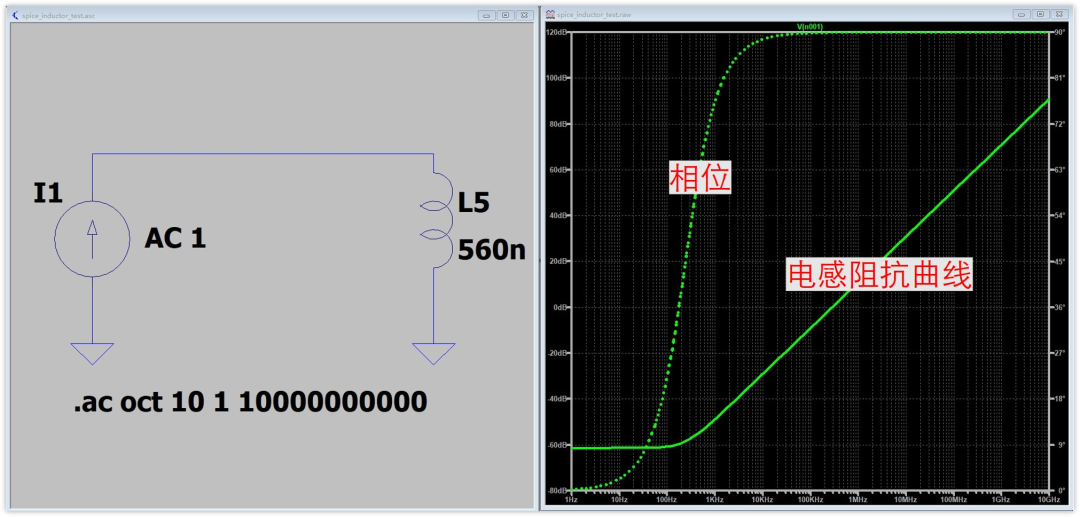

既然有懷疑,那就單獨(dú)測(cè)試下這個(gè)電感的阻抗曲線。

測(cè)試方法很簡(jiǎn)單,用1A的電流源,采用AC頻率掃描的方式,測(cè)量電感兩端電壓就可以了。

因?yàn)殡娏魇?A,所以阻抗值與測(cè)得的電壓相等,測(cè)試電路與結(jié)果如下圖:

實(shí)線是阻抗,虛線是相位。

很顯然,這個(gè)電感模型有問(wèn)題,或者說(shuō)是不夠準(zhǔn)確吧,因?yàn)樽杩闺S頻率的增大而增大,連自諧振頻率都看不見(jiàn)。

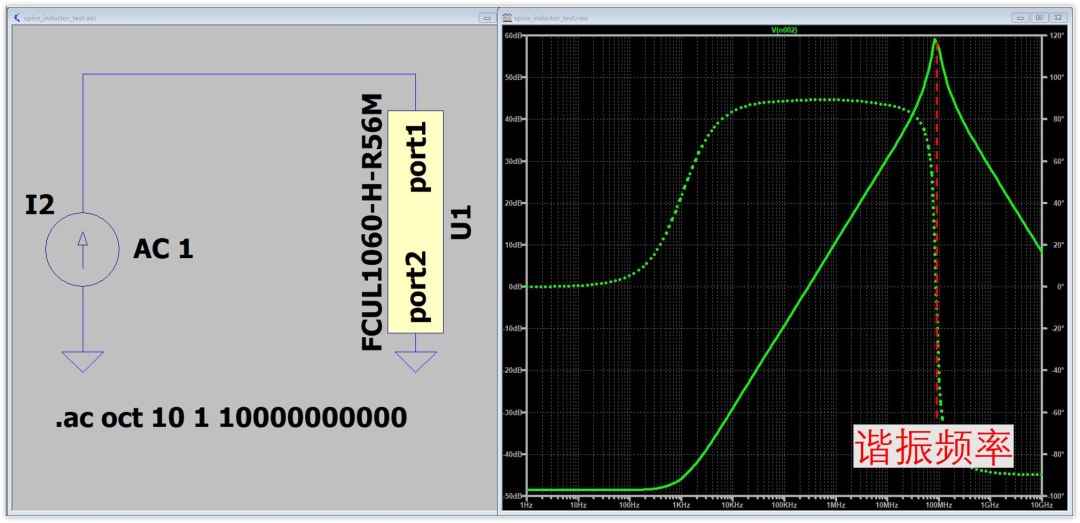

因此,我從村田下載了FCUL1060-H-R56M的Spice文件,重新構(gòu)建模型,再次測(cè)試阻抗曲線如下圖:

注意,上圖中U1就是重新生成的電感模型,這個(gè)LTspice軟件打開(kāi)spice文件,然后自動(dòng)創(chuàng)建的電感模型,所以在LTspice看來(lái),它是一個(gè)模塊,位號(hào)就成了U1,大家知道這是我生成的電感模型就好。

可以看到自諧振頻率大概是100Mhz,這個(gè)模型應(yīng)該是比較準(zhǔn)確的,看起來(lái)是那么回事。

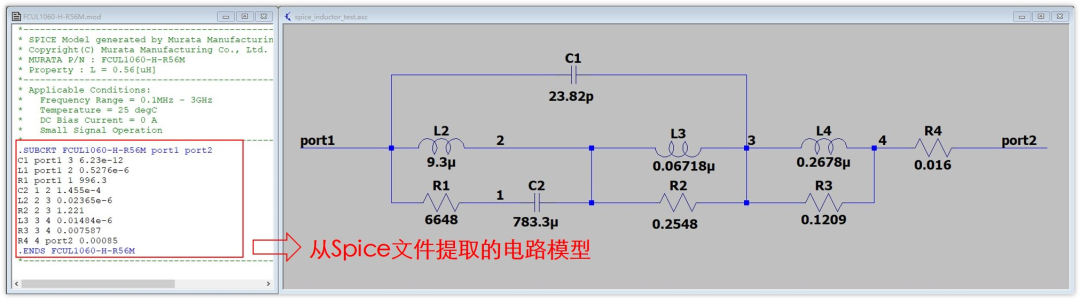

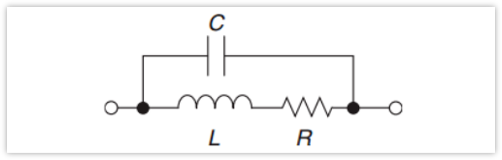

其實(shí)我們也可以從spice文件提取出這個(gè)電感的等效電路模型,spice文件本質(zhì)來(lái)說(shuō)就是個(gè)網(wǎng)表

上圖是我根據(jù)spice文件畫(huà)出的等效電路模型,仿真一下會(huì)發(fā)現(xiàn)阻抗曲線與前面的一模一樣。

可以看到,這個(gè)官網(wǎng)提供的電感的spice文件還是挺復(fù)雜的,它創(chuàng)建的電感的模型應(yīng)是更為準(zhǔn)確的。

我們平時(shí)可能會(huì)說(shuō)電感的高頻模型是下圖這樣的。這也不能說(shuō)錯(cuò),只能說(shuō)不夠準(zhǔn)確,因?yàn)槲覀兤綍r(shí)也不需要那么精確,因此下圖也就夠用了。

而這次我們需要更精準(zhǔn)的模型,所以用廠家官網(wǎng)提供的spice文件是最好的。

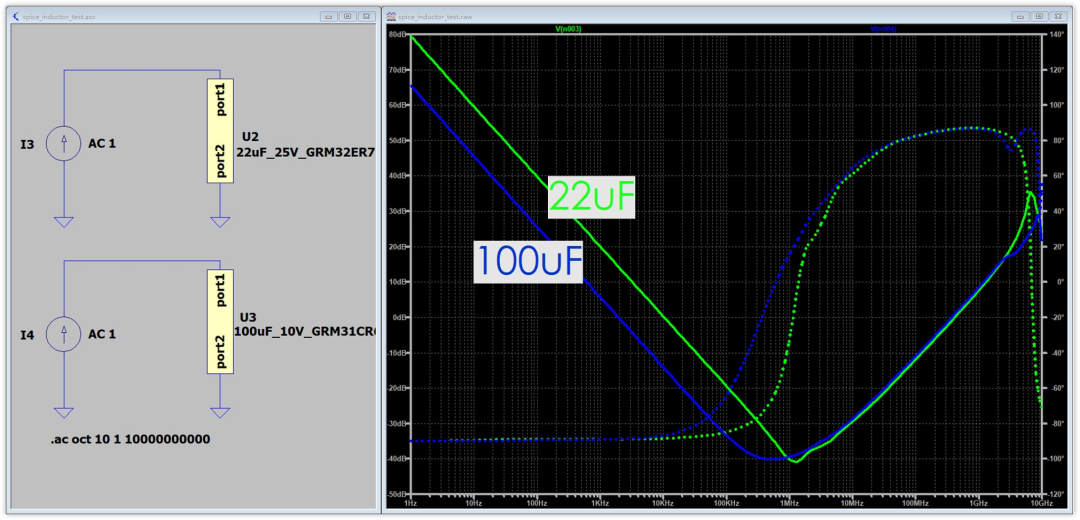

更新電容模型

同樣的方法,我從官網(wǎng)下載我使用的22uF和100uF電容的spice文件,構(gòu)成新的模型,測(cè)試阻抗曲線如下圖所示

同樣,實(shí)線是阻抗,虛線是相位

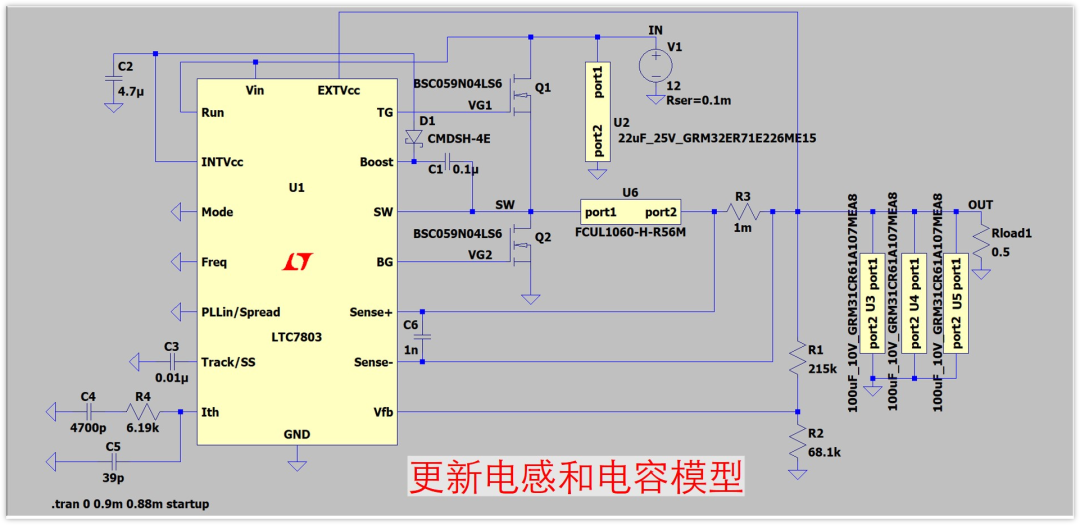

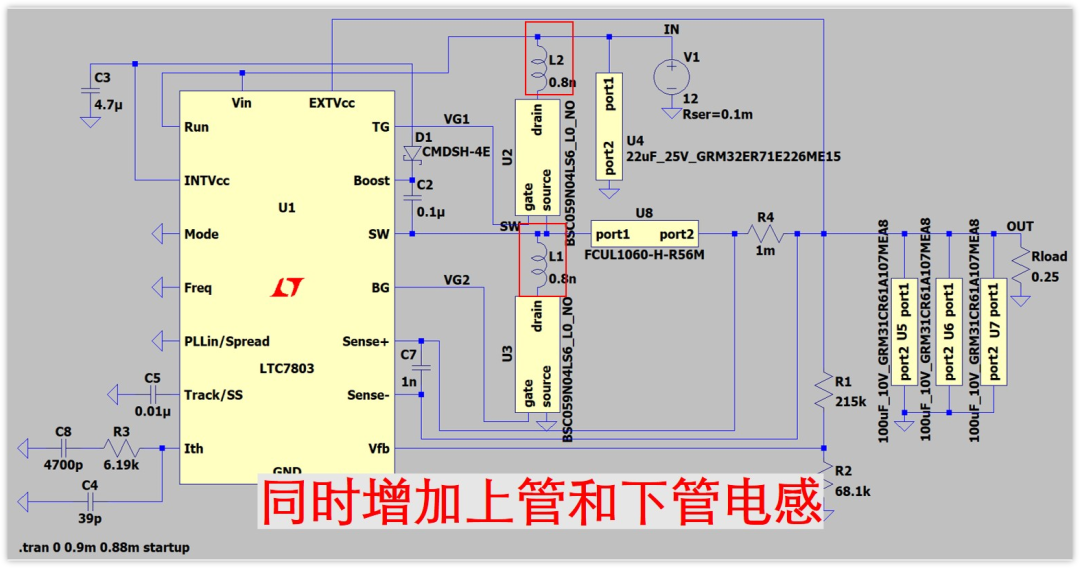

使用新的電感和電容模型,放入到原來(lái)的電路中,電路如下所示:

電感和濾波電容均使用了從官網(wǎng)下載的spice文件構(gòu)建的模型,仿真SW的波形如下圖:

與更新模型之前相比,基本沒(méi)差別,這說(shuō)明問(wèn)題不在更新的模型上面。

LTC7803只是一個(gè)驅(qū)動(dòng)芯片,產(chǎn)生Vgs信號(hào),用作驅(qū)動(dòng)MOS管開(kāi)關(guān),拋開(kāi)開(kāi)關(guān)速度不談的話,應(yīng)該跟尖峰關(guān)系不大。那就只剩下MOS管的原因了。

我們接著看

更新MOS管模型

從前面知道,LTspice軟件自帶的模型很可能是簡(jiǎn)易的,也就是說(shuō)是不夠精確的,NMOS管很有可能也是如此。

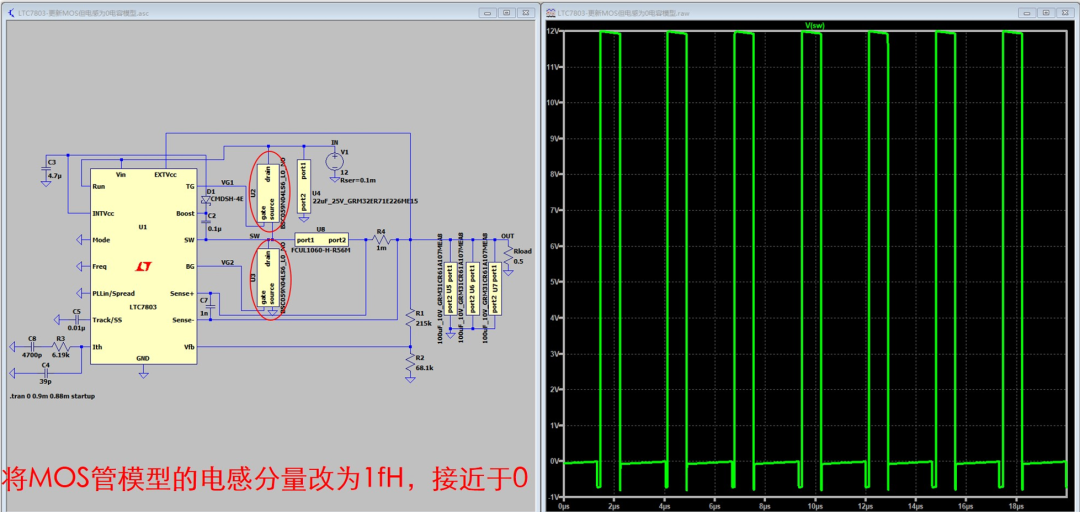

電路圖中MOS管使用的是BSC059N04LS6,廠家是Infineon,我從官網(wǎng)上面下載spice文件,根據(jù)spice構(gòu)建新的模型,換到前面的電路中,電路更新如下圖:

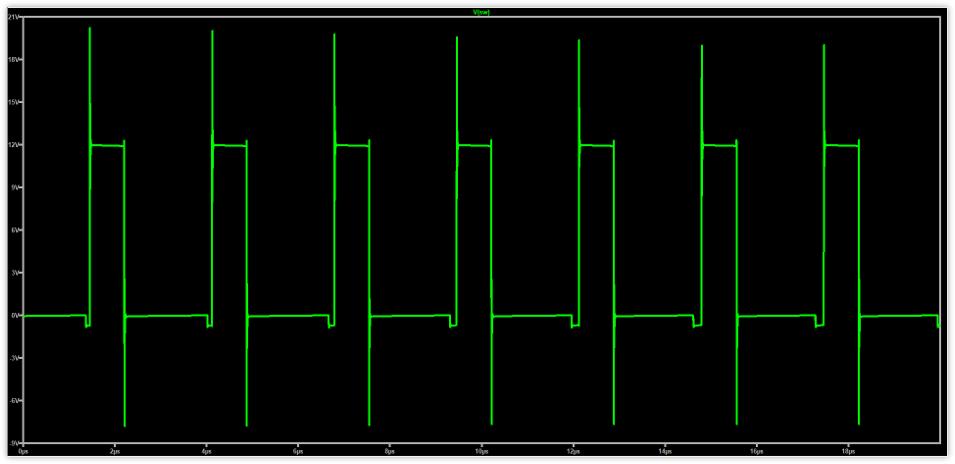

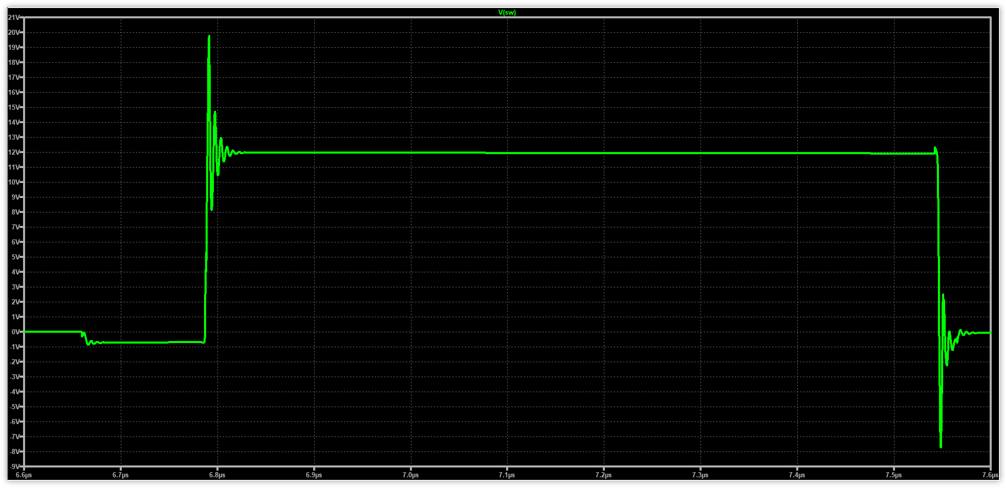

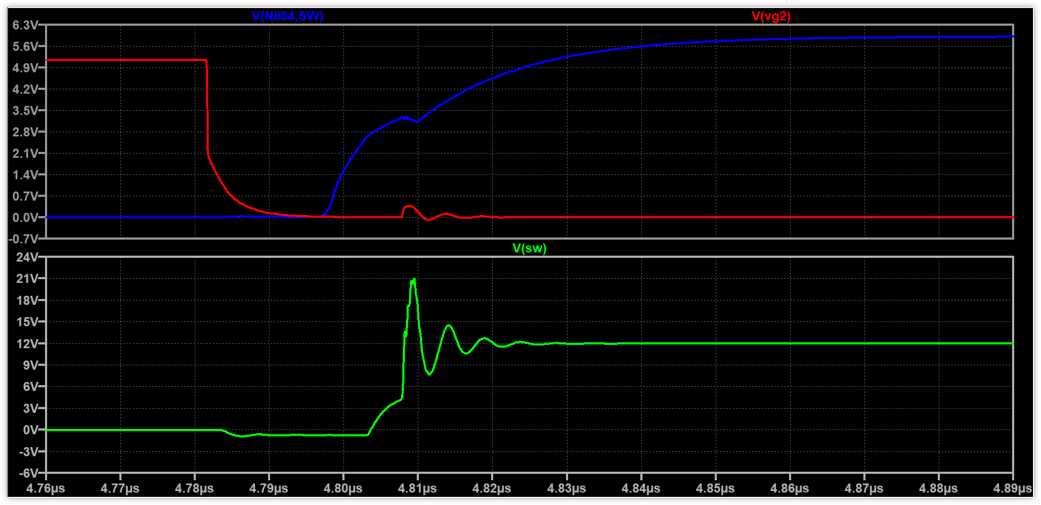

仿真SW波形如下圖:

久違的振蕩尖峰終于出現(xiàn)了。。。有一絲興奮。。。

上下尖峰幅度差不多,大概有8V。

現(xiàn)在已經(jīng)看到了類(lèi)似于我們現(xiàn)實(shí)中的尖峰,那么問(wèn)題來(lái)了,這個(gè)尖峰到底是怎么產(chǎn)生的呢?目前看到的就是我們換了一個(gè)MOS管的模型就出現(xiàn)了。

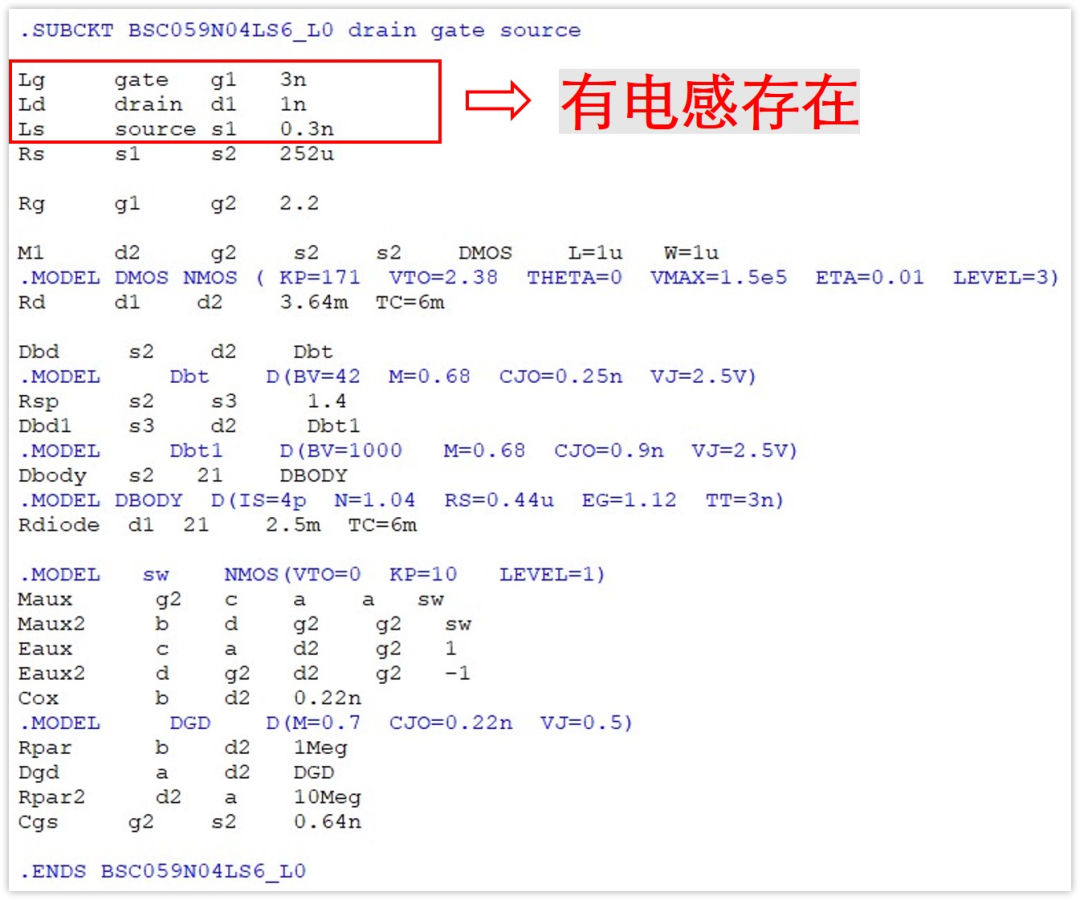

這個(gè)官網(wǎng)提供的MOS管模型到底有什么不同呢?

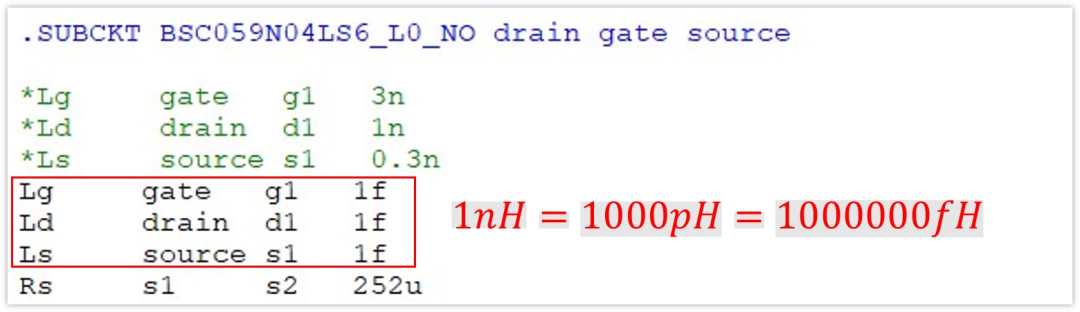

上圖是官網(wǎng)下載的MOS管的spice文件,需要特別注意的是有三個(gè)參數(shù),Lg,Ld,Ls這是3個(gè)電感分量。

它的意思是,在MOS管的G,D,S極上面分別串聯(lián)了電感。

因此,我猜測(cè)就是因?yàn)橐肓诉@3個(gè)電感分量,所以才有了振蕩尖峰。

之所以有此猜測(cè),是因?yàn)檎袷幖夥瀹a(chǎn)生的原因一般就是因?yàn)長(zhǎng)C阻尼振蕩,MOS管的模型一般都不會(huì)少了電容,而電感卻不一定有。

為了驗(yàn)證到底是不是這三個(gè)電感的原因,我將Lg,Ld,Ls都改成了1fH,1fH等于10的負(fù)六次方納亨。其實(shí)我是想改為0的,只不過(guò)改為0后仿真出現(xiàn)不收斂的情況,因此就改成了1fh,這也足夠小了。

將電感參數(shù)改為1fH。

創(chuàng)建一個(gè)新的模型,替換到電路中,再次仿真一下。

會(huì)看到SW的尖峰沒(méi)有了,所以可以肯定的是,MOS管上面串聯(lián)的電感是產(chǎn)生尖峰的必要條件。

那問(wèn)題又來(lái)了?

能不能直接從拓?fù)浣Y(jié)構(gòu)分析下,電感是產(chǎn)生尖峰的必要條件?

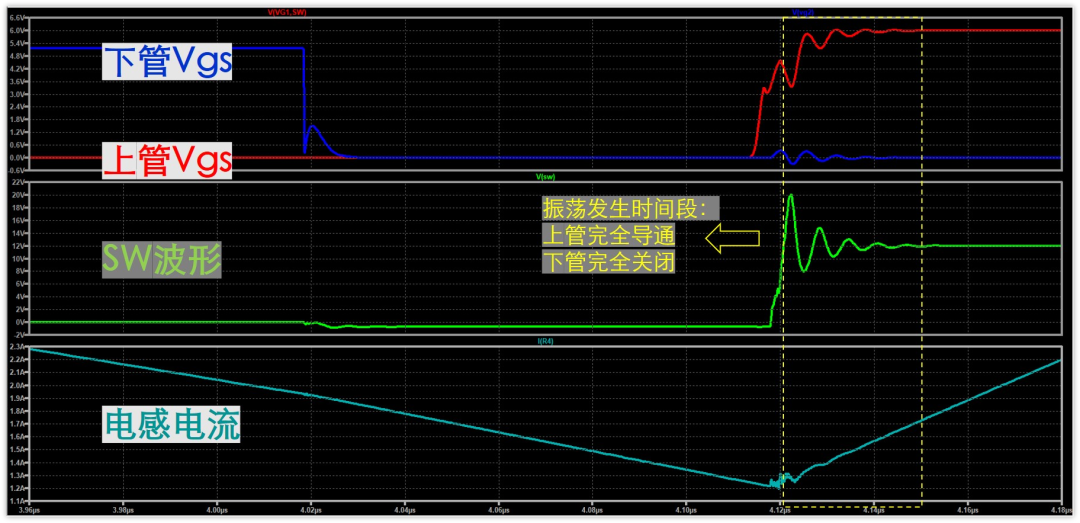

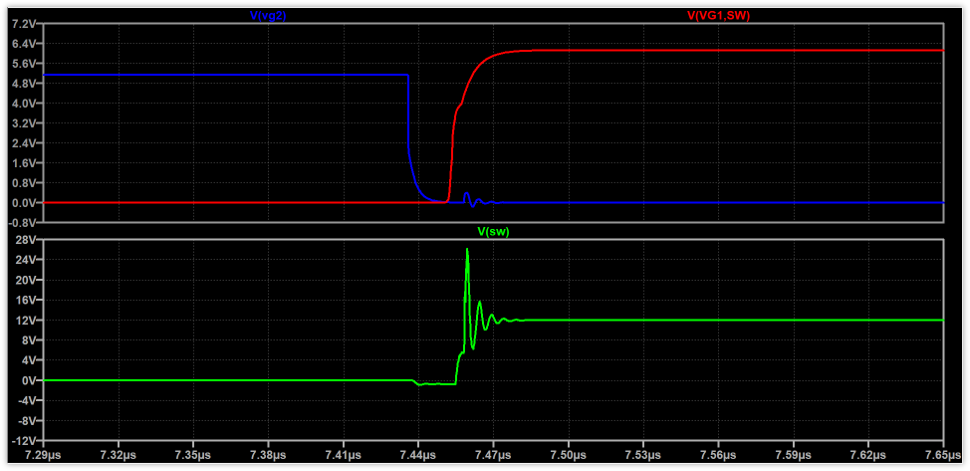

先來(lái)看產(chǎn)生尖峰的時(shí)候,兩個(gè)開(kāi)關(guān)管的開(kāi)通與關(guān)閉情況。

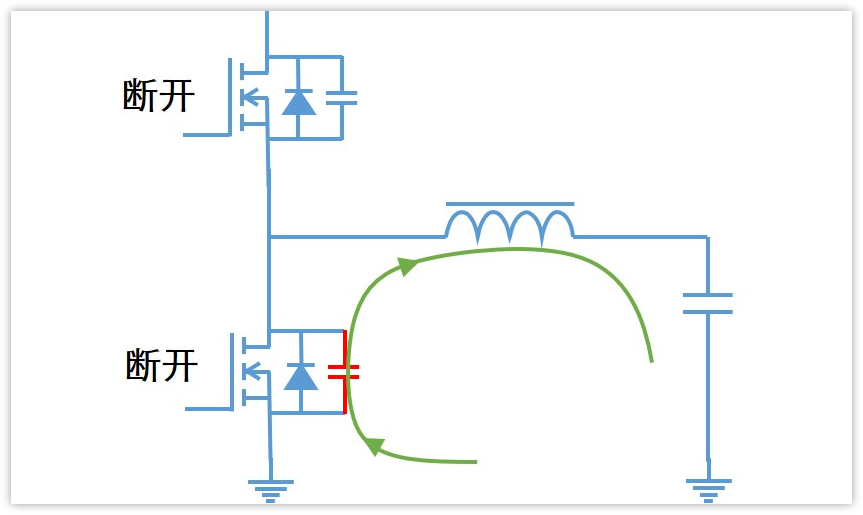

以上升尖峰為例。

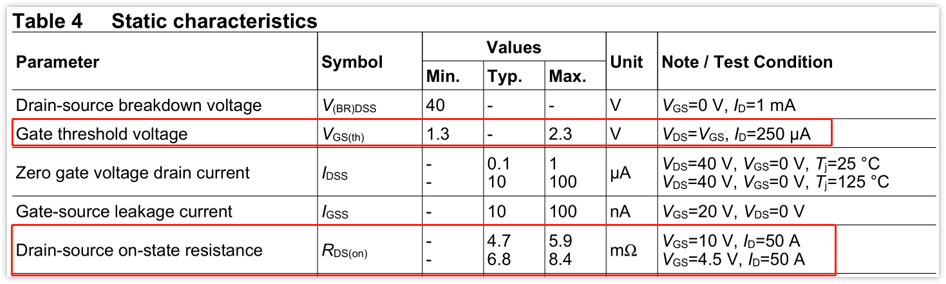

紅色的波形是上管的Vgs電壓,藍(lán)色的是下管的Vgs電壓,綠色的為SW電壓,最下面的為電感電流。

MOS管使用的是BSC059N04LS6,我們查看芯片手冊(cè),會(huì)發(fā)現(xiàn)在Vgs的開(kāi)啟門(mén)限最大是2.3V。而在在SW處產(chǎn)生尖峰振蕩的時(shí)候,Vgs都在3.5V以上,也就是說(shuō)上管已經(jīng)完全導(dǎo)通了,而此時(shí)下管是完全關(guān)閉的,這可以從上圖中的波形中看出來(lái)。

也就是說(shuō),上尖峰振蕩的時(shí)候,上管完全導(dǎo)通,下管完全關(guān)閉,不是在開(kāi)關(guān)開(kāi)始切換,半導(dǎo)體的時(shí)間段。

上管完全導(dǎo)通說(shuō)明什么呢?

盡管上管有寄生電容,但是此時(shí)上管完全導(dǎo)通,導(dǎo)通電阻只有幾毫歐,所以這個(gè)寄生電容也被短路了。

如果沒(méi)有串聯(lián)的寄生電感存在,那么就相當(dāng)于是輸入電源直接通過(guò)幾毫歐的電阻接到了SW管腳,而輸入電源電壓可以認(rèn)為是基本不變的。

所以沒(méi)有電感的話,SW處不可能產(chǎn)生高達(dá)8V的尖峰振蕩。

只有中間存在寄生電感,才會(huì)因?yàn)殡娏髯兓浅?欤阋栽陔姼猩厦娈a(chǎn)生8V的電壓。

那具體過(guò)程是怎么樣呢?

在上管導(dǎo)通之前,功率電感從下管的體二極管續(xù)流,下管的寄生電容C2電壓為0。

在上管導(dǎo)通之后,其導(dǎo)通電阻只有幾毫歐,因此C1相當(dāng)于被短路。下管完全斷開(kāi),但是上面有寄生電容C2。

我們看SW節(jié)點(diǎn),因?yàn)槲覀儸F(xiàn)在分析的是很小的一段時(shí)間,所以功率電感此時(shí)可以看作恒流,電流方向流向負(fù)載。

可能有人會(huì)認(rèn)為功率電感也有寄生電容參數(shù),能走高頻電流,所以不能看作恒流源。關(guān)于這一點(diǎn),其實(shí)我也懷疑過(guò),這也是我要更新模型的原因。

不過(guò)查看功率電感的電流波形,在振蕩時(shí)間段,確實(shí)是基本不變的。

另外我們知道,振蕩頻率是百兆量級(jí)的,而我們查看這個(gè)功率電感的阻抗曲線,其自諧振頻率就在100Mhz左右,此時(shí)阻抗最大,阻抗達(dá)到了上千歐姆,所以它是無(wú)法通過(guò)高頻的電流的。

我們繼續(xù)。

我們知道,SW節(jié)點(diǎn)處穩(wěn)定之后基本等于電源電壓。

在開(kāi)關(guān)導(dǎo)通之后,SW從0V電壓開(kāi)始上升,那么C2在被充電,電源需要通過(guò)L1提供功率電感L3的續(xù)流以及對(duì)C2的充電。

也就是說(shuō):L1的電流=功率電感L3的電流+C2的充電電流

隨著SW節(jié)點(diǎn)的電壓升高,一直到SW電壓和Vin一樣,這時(shí)候電壓為什么不停止上升呢,直接達(dá)到穩(wěn)態(tài)呢?

這是因?yàn)長(zhǎng)1的電流=功率電感L3的電流+C2的充電電流,也就是說(shuō)在SW電壓達(dá)到Vin之前,L1的電流》功率電感電流。

在SW電壓達(dá)到Vin時(shí),如果電壓不再上升,那么意味著C2不再被充電,即流過(guò)C2的 電流為0,那么L1的電流=功率電感電流。

而事實(shí)是L1的電流》功率電感電流。

所以在SW達(dá)到Vin電壓之后,SW電壓繼續(xù)上升,會(huì)大于Vin,此時(shí)電感L1兩端的電壓反向,電流開(kāi)始減小。

隨著SW電壓上升,那么C2繼續(xù)被充電。

當(dāng)L1的電流減小到和功率電感一樣的時(shí)候。

因?yàn)長(zhǎng)1的電流=功率電感L3的電流+C2的充電電流。那么意味著C2的充電電流為0,就不能通過(guò)L1接著對(duì)C2進(jìn)行充電了。

此時(shí)SW電壓達(dá)到最高,但它也不能保持住,為啥呢?

因?yàn)榇藭r(shí)SW的電壓大于Vin,電感L1的電流要繼續(xù)減小。而功率電感L3的電流不變,所以功率電感必須從C2抽取電流,這意味著C2開(kāi)始放電。

C2開(kāi)始放電后,SW電壓開(kāi)始降低,然后SW的電壓降低到Vin,此時(shí)L1的電流達(dá)到最小。再之后C2繼續(xù)放電(因?yàn)長(zhǎng)1電流小,不足以提供功率電感的續(xù)流),SW電壓繼續(xù)降低,L1兩端電壓反向,L1的電流開(kāi)始增大,直到L1電流大小達(dá)到功率電感的電流。

此時(shí)C2停止放電,SW電壓達(dá)到最低,然后C2開(kāi)始被充電,SW電壓開(kāi)始升高,如此循環(huán)往復(fù),SW處電壓看起來(lái)就是振蕩了。

當(dāng)然整個(gè)過(guò)程中因?yàn)橛须娮璺至浚哉袷幏凳窃絹?lái)越小的,本質(zhì)就是LCR阻尼振蕩。

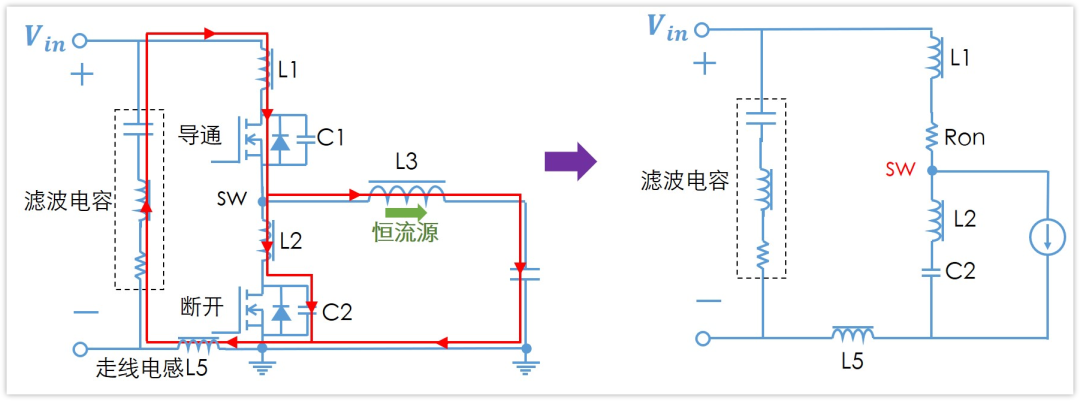

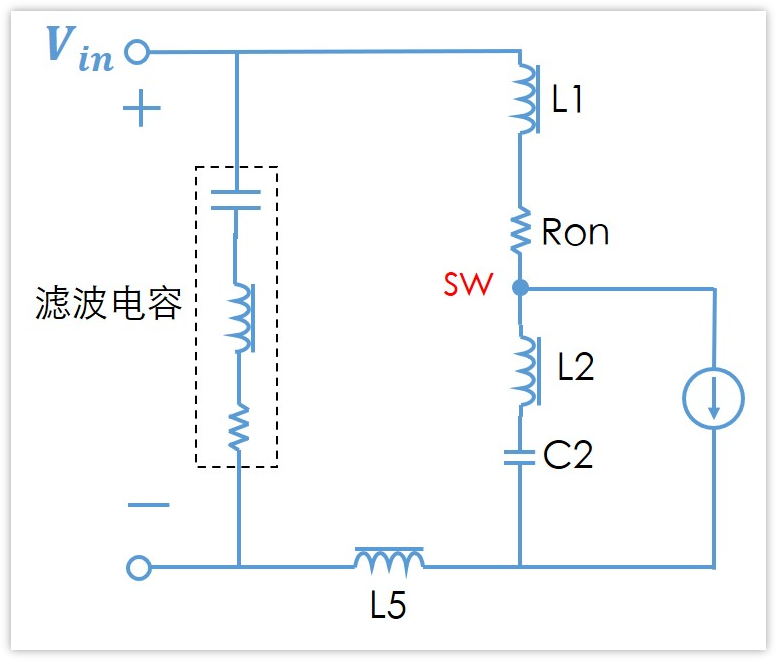

簡(jiǎn)易的等效電路如下:

濾波電容的寄生電感,電阻,還有回路中的走線電感,電阻,都是處于振蕩回路。

上管到輸入濾波電容之間的電感量對(duì)上升沿尖峰的大小起了決定性的作用,因?yàn)榧夥宓拇笮』揪偷扔贚1的兩端電壓(忽略Ron兩端的電壓)。如果沒(méi)有L1的存在,振蕩雖然還存在,但是SW處的電壓基本是不變的,就越等于Vin。

很明顯,如果寄生電感L1比較大,那么產(chǎn)生的尖峰電壓肯定是越大的。

那負(fù)載電流大小與振蕩尖峰的大小有關(guān)系嗎?

關(guān)系是有的,負(fù)載電流越大,那么意味著功率電感電流越大,在SW從0上升到Vin電壓時(shí),寄生電感L1得到的電流也越大,L1獲得的用于振蕩的能量也是越大的。用于振蕩的能量越大,那么振蕩尖峰自然也就越高。

也就是說(shuō)負(fù)載電流越大,參與振蕩的能量越多,那么產(chǎn)生的尖峰也是越高的。

同樣的,開(kāi)關(guān)速度越快,寄生電感電流上升的速度也越快,在SW從0上升到Vin電壓時(shí),寄生電感L1得到的電流也越大,參與振蕩的能量也越多,所以尖峰也越高。

以上就是上尖峰的分析過(guò)程如果從文字描述的過(guò)程看,相當(dāng)?shù)膹?fù)雜,下尖峰也就不分析了,疲了。。。。

我們來(lái)看點(diǎn)輕松的,直接看實(shí)驗(yàn)過(guò)程。

如何看寄生電感的影響有多大呢?

前面我們不是將Lg,Ld,Ls三個(gè)參數(shù)改成接近于0的值,重新構(gòu)建模型,尖峰就消失了么?

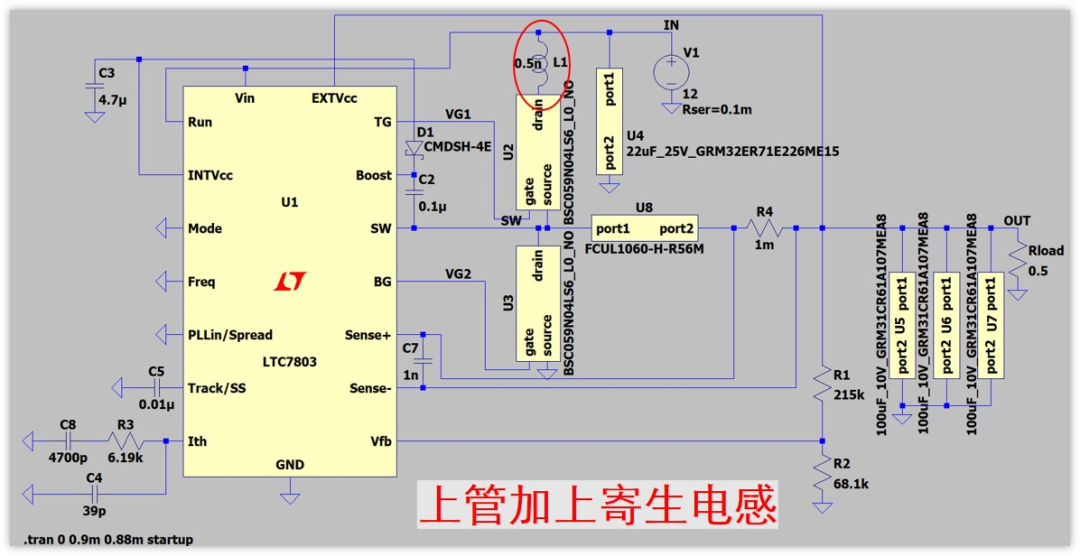

我們繼續(xù)使用該模型,然后手動(dòng)在電路上面串聯(lián)電感,然后修改不同的電感值,看看尖峰的大小。

1、只在上管串聯(lián)0.5nH電感,下管沒(méi)有串聯(lián)電感,負(fù)載為0.5Ω,電壓為3.3V,那么負(fù)載電流為6.6A。

可以看到此時(shí)上尖峰最高為4V,而下尖峰是沒(méi)有的(負(fù)的電平為死區(qū)時(shí)間的0.7V體二極管壓降)

這說(shuō)明上尖峰的大小是由上管的寄生電感決定的,下尖峰的大小是由下管的寄生電感決定的。

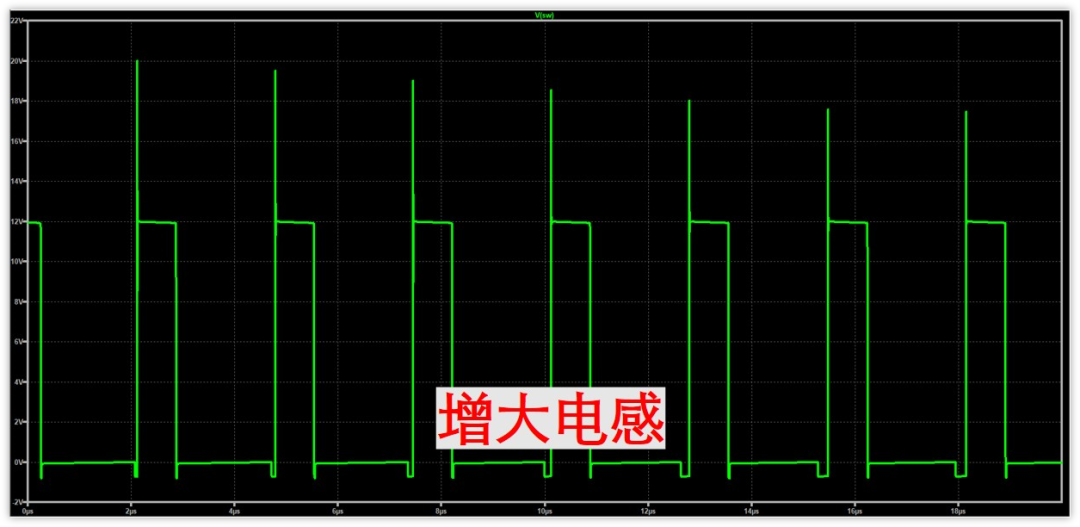

2、將上管串聯(lián)0.5nH電感改為0.8nH

可以看到上尖峰最高為8V,比原來(lái)4V高了不少,這說(shuō)明電感越大,尖峰越大

3、我們順便還可以改變一下負(fù)載,看一下電流對(duì)尖峰的影響。

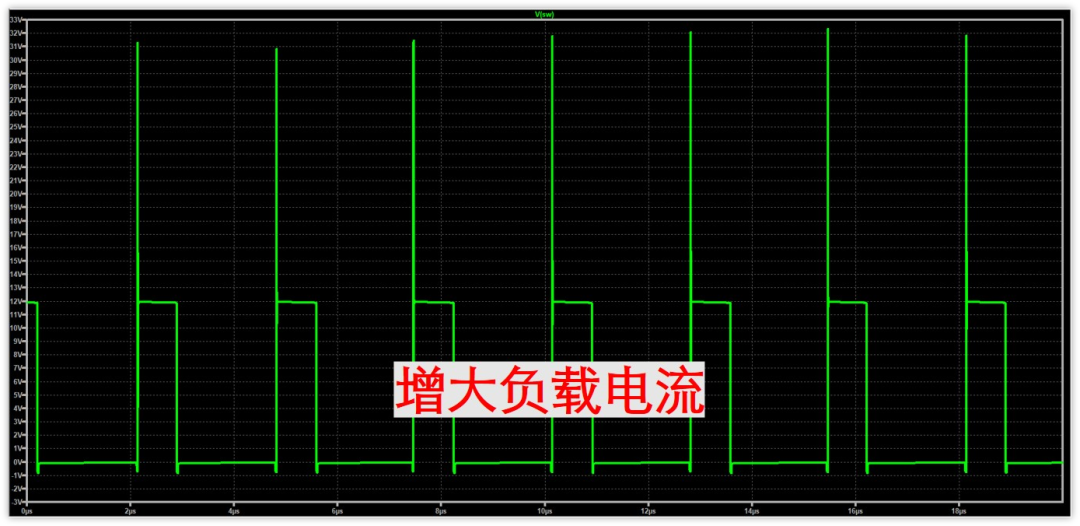

保持上管串聯(lián)0.8nH,負(fù)載電阻減小一倍,即負(fù)載電流增加1倍,為13.2A。

可以看到,上尖峰達(dá)到了19V,增大了很多。這說(shuō)明了負(fù)載電流越大,尖峰越大。

這跟前面分析是一致的,負(fù)載電流越大,上下管切換的時(shí)候,寄生電感獲得的參與振蕩的能量越高,尖峰也越大。

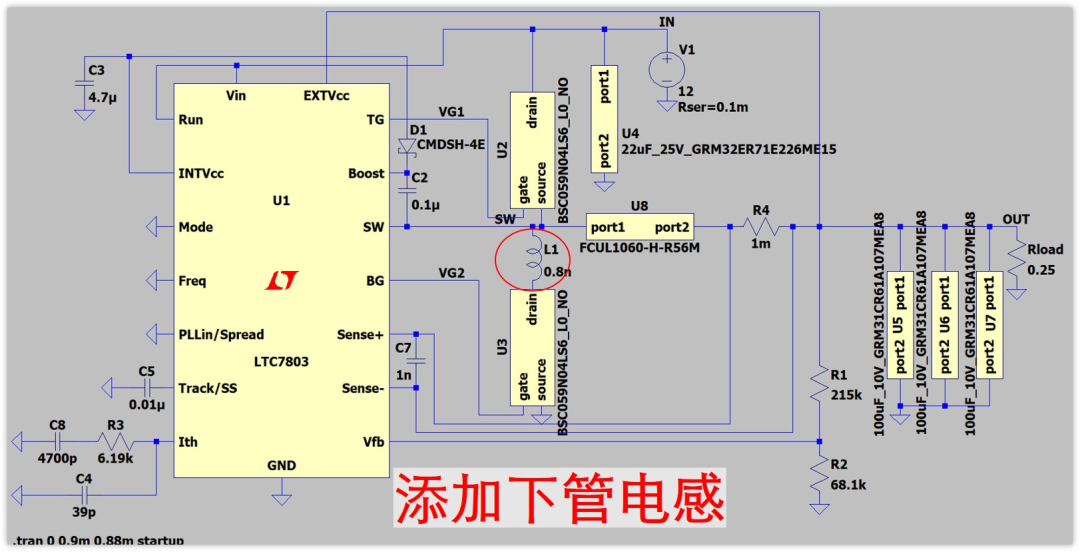

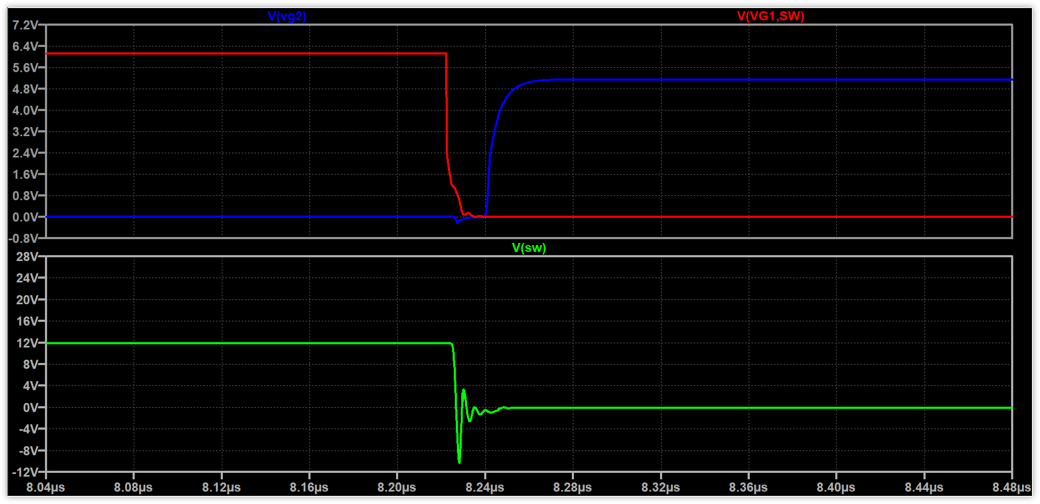

4、我們?nèi)サ羯瞎艿拇?lián)電感,下管串聯(lián)0.8nH,負(fù)載電流還是13.2A

電路圖如下圖:

仿真的SW波形如下圖:

可以看到,沒(méi)有上尖峰,下尖峰大概有10.5V,這說(shuō)明了下尖峰的大小是由下管的寄生電感決定的。

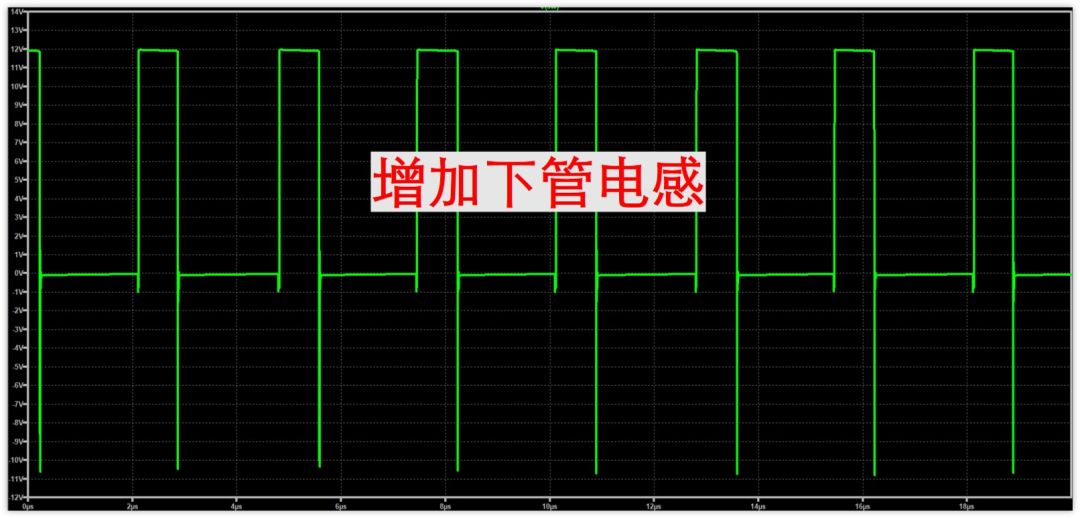

5、我們給上管和下管都加上0.8nH的電感,負(fù)載電流還是為13.2A

電路圖如下:

仿真的SW波形如下圖:

這時(shí),可以看到,上下尖峰同時(shí)存在。

上尖峰是14V左右,下尖峰是10V左右。

這里又存在一個(gè)問(wèn)題了。。。

為什么電感都是0.8nH,下尖峰的值更小?

我同時(shí)查看Vgs與SW波形,發(fā)現(xiàn),上尖峰振蕩發(fā)生在上管導(dǎo)通,下管不導(dǎo)通的時(shí)間段

而下尖峰發(fā)生在死區(qū)時(shí)間,上下管子都不導(dǎo)通

死區(qū)時(shí)間,意味著功率電感的續(xù)流是通過(guò)下管的體二極管,我們知道體二極管有壓降,會(huì)損失能量。

所以說(shuō)下尖峰比上尖峰多了一個(gè)體二極管的損失能量,所以尖峰更小。

寄生電感相同時(shí),那么下管尖峰一定比上管小嗎?

我們接著看

6、上管和下管都加0.8nH電感,負(fù)載電阻增大到0.5Ω,負(fù)載電流減小一半,為6.6A

可以看到,電流改小之后,上下尖峰都減小了,這也與前面的分析一致。

不過(guò)現(xiàn)在上下尖峰都是7V左右,二者差不多,并沒(méi)有像前面說(shuō)的下尖峰更小,這又是為什么呢?

我們?cè)俅蜷_(kāi)功率電感電流和Vgs的波形

上升沿尖峰時(shí),功率電感電流是最小的,功率電感續(xù)流需要走上管,也就是說(shuō)最終上管的0.8nH所需要的達(dá)到的電流較小,這會(huì)導(dǎo)致尖峰比較小。

而下尖峰時(shí),功率電感電流是最大的,功率電感續(xù)流需要走下管,也就是說(shuō)最終下管的0.8nH所需要的達(dá)到的電流較大。這會(huì)導(dǎo)致尖峰比較大。

所以,上下尖峰的大小誰(shuí)大誰(shuí)小,視情況而定。

我們極端一點(diǎn),如果這個(gè)buck工作在斷續(xù)模式,那么意味著上管導(dǎo)通時(shí),功率電感電流是0,也就是說(shuō)功率電感需要通過(guò)上管續(xù)的電流為0,那豈不是上尖峰應(yīng)該消失呢?

我們來(lái)看一下。

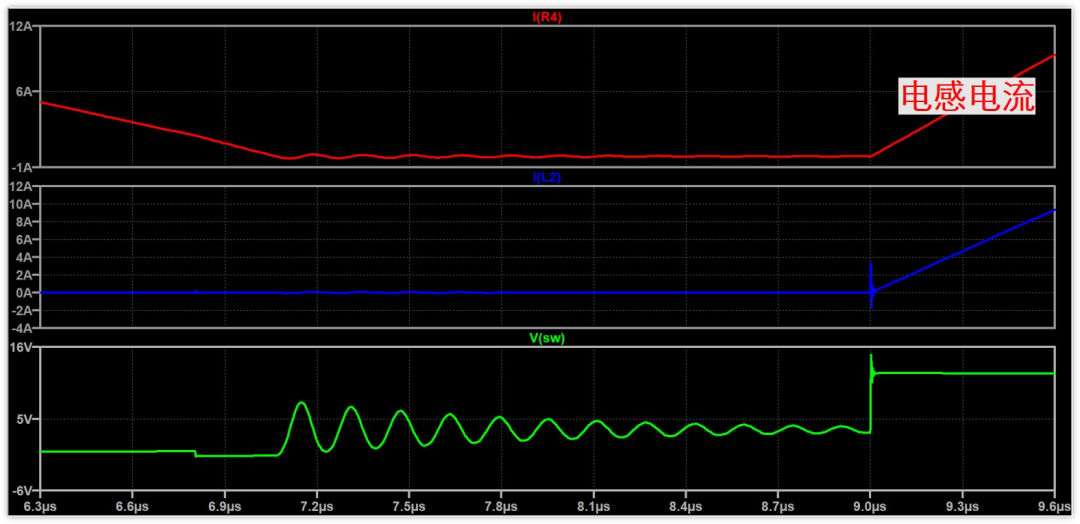

7、將負(fù)載電阻改為1Ω,負(fù)載電流為3A,buck進(jìn)入斷續(xù)模式,我們來(lái)看看上尖峰是否為0

SW波形如下:

可以看到,上升沿尖峰并沒(méi)有消失,好像與前面的分析不符啊,什么情況呢?

我們看一下上管0.8nH的電感電流,功率電感電流在上升沿時(shí)的情況。

可以看到,在上升沿時(shí),功率電感的電流確實(shí)為0,但是上升尖峰還是存在,因?yàn)?.8nH的電感是有電流存在的。

那這是為什么呢?

這是因?yàn)榈腗OS管的DS的兩端有寄生電容Coss,在上升沿之前,下管導(dǎo)通,Coss的電壓為0V,而導(dǎo)通之后,最終Coss的電壓是為12V的,這期間就構(gòu)成了LC的振蕩電路。

除了以上這些,尖峰的大小還與哪些因素有關(guān)系呢?

很容易想到的就是MOS管的開(kāi)關(guān)速度,這個(gè)我們可以在柵極加電阻,來(lái)增加導(dǎo)通時(shí)間。導(dǎo)通時(shí)間增加,在開(kāi)關(guān)管切換的時(shí)候,

8、開(kāi)關(guān)速度對(duì)尖峰大小的影響

在上下管串聯(lián)0.8nh電感,負(fù)載電流為13.2A,MOS管柵極沒(méi)有串聯(lián)電阻時(shí)。

MOS導(dǎo)通時(shí)間大概是7ns左右,上尖峰高度為14V

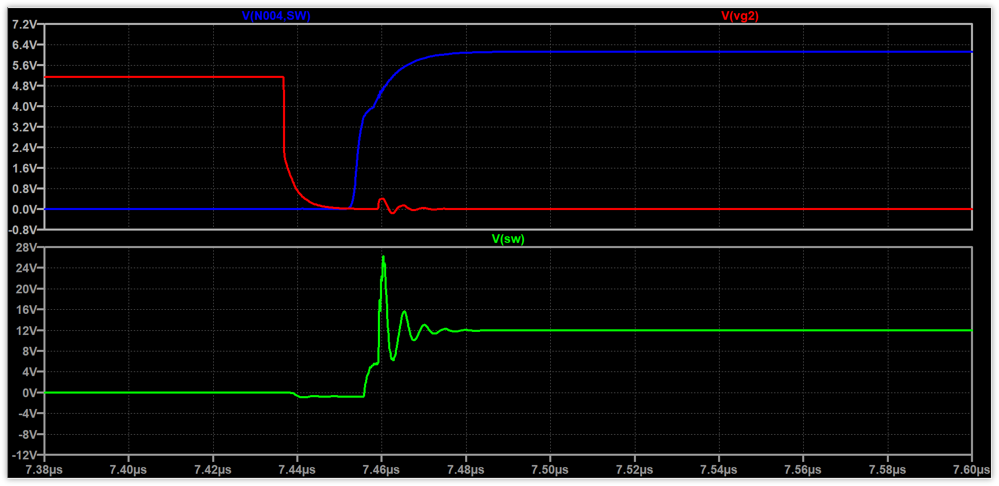

我們?cè)谏瞎軚艠O添加10歐姆電阻,電路如下

運(yùn)行,Vgs的電壓與SW波形如下圖。

可以看到,上MOS管柵極加了10歐姆電阻之后,從截止到導(dǎo)通的時(shí)間大概是13ns,比原來(lái)7ns時(shí)間更長(zhǎng),另外,SW的尖峰幅度也從14V降低了到9V

總的來(lái)說(shuō),BUCK上下尖峰的產(chǎn)生,與線路中的電感是密不可分的,電感越大,尖峰也就會(huì)越大。如果上下管沒(méi)有電感的存在,是產(chǎn)生了尖峰的。

除此之外,還與開(kāi)關(guān)管的開(kāi)通速度也有很大的關(guān)系,開(kāi)通越快,產(chǎn)生的振鈴尖峰也越高。

這個(gè)我估計(jì)有人就說(shuō)了,你廢了半天牛勁,整出一堆沒(méi)用的。

我們一般用的BUCK芯片都是集成的,內(nèi)部集成了MOS管,我們?cè)诰€路上面也不會(huì)額外加電感,有什么用呢?

實(shí)際電路中的電感是如何存在的?

前面做的一系列實(shí)驗(yàn),那個(gè)0.5nH/0.8nH電感,可以看作是線路中的寄生電感。

實(shí)際電路很復(fù)雜,芯片內(nèi)部引線電感,PCB走線電感,濾波電容的等效ESL等等。

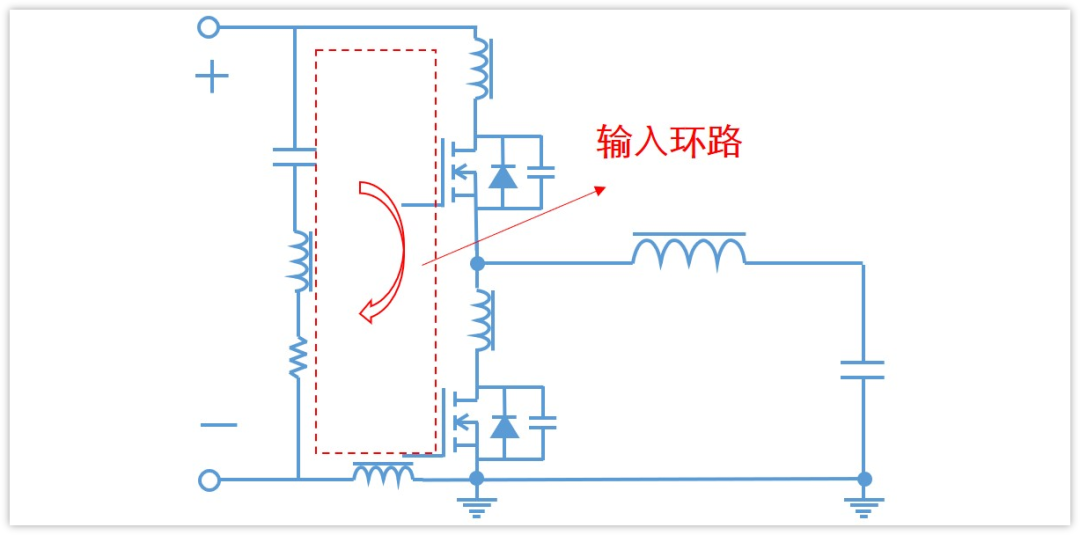

當(dāng)然,芯片內(nèi)部我們沒(méi)法改變,我們能改變的就是輸入濾波電容的位置,芯片好好接地。通過(guò)優(yōu)化PCB Layout降低走線電感量。

可能有人就說(shuō)了,走線電感,聽(tīng)著這么玄乎,真的有這么大的影響嗎?

確實(shí)是真的。

我上面仿真電路放的電感最大也才0.8nH,可以看到,引起的尖峰已經(jīng)很大了。

而0.8nH的電感量什么概念呢?到底大不大?

如圖所以,1盎司銅厚,線寬50mil,走線長(zhǎng)度10mm的電感量是6.52nH。可能我們輸入濾波電容會(huì)放得很近,但是一般距離也有個(gè)2mm左右吧,這樣走線電感也差不多1nH。

所以呢,在研究振蕩尖峰這個(gè)問(wèn)題時(shí),走線電感是不能忽略的。

而事實(shí)確實(shí)也是如此,我們用示波器測(cè)量實(shí)際電路的時(shí)候,都是會(huì)量到這個(gè)振蕩尖峰的,只不過(guò)有大有小而已。

在設(shè)計(jì)中,選定了BUCK芯片之后,我們能做的其實(shí)不多。

就是盡可能的將輸入濾波電容放得離芯片更近,巴不得直接將輸入濾波電容跨接在芯片的輸入管腳和地管腳上面,這樣輸入環(huán)路最小。

這一點(diǎn)也應(yīng)該是PCB layout里面最重要的一點(diǎn)吧。

有的DCDC芯片的管腳分布并不好,PCB layout時(shí)可能需要將輸入濾波電容放到PCB板背面去,這個(gè)時(shí)候就需要特別注意了,過(guò)孔一定要盡可能多打幾個(gè)。

為啥要多打過(guò)孔呢?

自然是因?yàn)檫^(guò)孔的寄生電感也是不能忽略的。

10/20mil的過(guò)孔的寄生電感達(dá)到了1nH,這電感量也是不小的。

所以我們?cè)赑CB layout的時(shí)候,如果是電容放置在背面,一定要多打些過(guò)孔,因?yàn)殡姼胁⒙?lián),總電感量是減小的。

多打過(guò)孔并不僅僅是考慮過(guò)流能力

在過(guò)流能力夠的情況下,如果一個(gè)老工程師要求你打幾個(gè)孔,或者把孔徑加大。或許你認(rèn)為是在為難你,也許是別人站的高度更高。

小結(jié)

文章有點(diǎn)長(zhǎng),做了大量的仿真與分析,主要結(jié)論如下:

1、死區(qū)時(shí)間是同步buck中必然存在的,如果用示波器測(cè)到在開(kāi)關(guān)切換時(shí),有個(gè)負(fù)壓的臺(tái)階,請(qǐng)不要驚慌,那是正常現(xiàn)象

2、寄生電感是BUCK上下沿振蕩尖峰存在的必要條件。在做電路設(shè)計(jì)時(shí)一定要注意減小寄生電感。

3、開(kāi)關(guān)速度越快,寄生電感越大,那么振蕩尖峰也會(huì)越大。

4、振蕩尖峰與PCB Layout的關(guān)系非常大。

1、文檔

關(guān)于振蕩尖峰的,我有看到一個(gè)非常好的資料,大家也可以看一看。里面有說(shuō)如何加RC緩沖電路(Snubber電路),如何在自舉電路上面串聯(lián)電阻降低開(kāi)關(guān)速度等,也做了較多實(shí)驗(yàn)。

文件是在Richtek網(wǎng)站上下載的,文件名是《消除 Buck 轉(zhuǎn)換器中的 EMI 問(wèn)題》

2、我用LTspice仿真文件:包括原理圖,spice文件,自建的模型庫(kù),大家有需要自提。

需要注意,拿到我仿真文件直接運(yùn)行可能不行,需要添加庫(kù)的路徑,修改下自薦模型的屬性。

編輯:jq

-

芯片

+關(guān)注

關(guān)注

454文章

50460瀏覽量

421971 -

二極管

+關(guān)注

關(guān)注

147文章

9581瀏覽量

165954 -

pcb

+關(guān)注

關(guān)注

4318文章

23022瀏覽量

396424 -

MOS管

+關(guān)注

關(guān)注

108文章

2397瀏覽量

66623

原文標(biāo)題:Buck的振鈴實(shí)驗(yàn)與分析

文章出處:【微信號(hào):gh_3a15b8772f73,微信公眾號(hào):硬件工程師煉成之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

請(qǐng)問(wèn)PCM2903C的溫度范圍到底是多少呢?

功放和運(yùn)放到底是什么區(qū)別?

LMH6502的輸入電壓到底是多少?

開(kāi)關(guān)電源尖峰干擾的產(chǎn)生原因和抑制方法

運(yùn)放旁路電容必須靠近芯片引腳的原因到底是什么呢?

MOS管尖峰產(chǎn)生的原因

共享單車(chē)到底是什么通信原理

晶體振蕩器三態(tài)輸出技術(shù)到底是什么?

SiC MOSFET驅(qū)動(dòng)電壓尖峰的抑制方法簡(jiǎn)析(下)

SiC MOSFET驅(qū)動(dòng)電壓尖峰與抑制方法分析(上)

BUCK到底是怎么產(chǎn)生尖峰振蕩呢?

BUCK到底是怎么產(chǎn)生尖峰振蕩呢?

評(píng)論