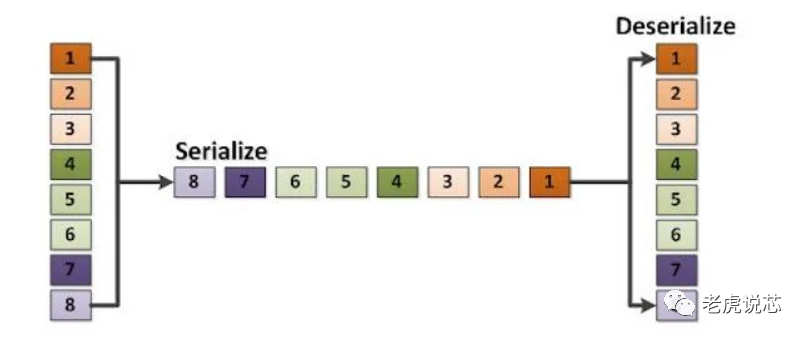

盡管SERDES(SERializer/DESerializer)擁有十分復雜的設計和驗證過程,但已成為SoC中不可或缺的組成部分。成熟穩定的SERDESIP,降低了設計成本和風險,加快了產品SoC產品上市的速度。

如今,PCIe、HDMI以及USB這樣的高速接口已變得不可或缺,但20年前的情況并不是這樣,過去的20年中,串行接口應用數量經歷了爆炸性的增長。

從上世紀九十年代末開始,SERDES二十年的革命之路。本文將通過一些底層技術的簡單介紹,嘗試解釋下為什么串行接口(以SERDES為代表)變得如此流行。

起源和演化

SERDES在光纖和同軸鏈路通信場景下廣為使用,其原因顯而易見,使用串行傳輸而非并行傳輸可以節約電纜數量!對于僅有的幾條線纜,最大限度的提高其吞吐量顯得尤為重要,這種情況下SERDES的面積和功耗則成了次要考慮的因素。

在上世紀80年代中期,串口上的數據速率很大程度上是由電信需求決定的(同步光纖網絡SONET)。在這段時期,若以今天的標準(51.84Mb/s,155.52Mb/s)看來,OC(光載OpticalCarrier)-1和OC-3的要求不算太高。OC-24要求單通道的傳輸速率要超過1Gb/s(1244.16Mb/s),它使用的是1990年左右最先進的雙極(bipolar)和砷化鎵(GaAs)工藝。

上世紀90年代后期,是SERDES歷史上的一個重要時期:OC-24(2488.32Mb/s)開始投入使用,同時速度大約為10Gb/s的OC-192也在規劃之中。幾年后(2000年代初),10Gb/s線速的以太網面世,與

XAUI不同,XAUI使用4個通道合并從而達到10Gb/s(XAUI接口讀作“Zowie”,其中的“AUI”部分指的是以太網連接單元接口(EthernetAttachmentUnitInterface);“X”代表羅馬數字10,它意味著每秒萬兆(10Gbps))。

接下來,SERDES另一個重要的發展時期開始了——SERDES正越來越多地用于PCB底板上的片間通信,以取代并行接口。這個進步把SERDES從一個重要的長途通信電路變成了SoC上的關鍵模塊。在這一點上也許PCIe是最好的例子,PCIe在2002年開始使用2.5Gbps的帶寬,并在2000年代中期開始變得流行起來。

各種串行數據標準的推出和SERDES研究的狀態如圖1所示。他們包括:

光纖傳輸:OC-192,OC-768,SONET

PC內部接口:PCIe1-5代

存儲:光纖通道(FibreChannel),SATA,SAS

視頻顯示:顯示接口(DisplayPort),HDMI

網絡:SGMII,1-Gb以太網,10-Gb以太網,25/100-Gb以太網

注:SATA:一種串行數據傳輸總線,SATA是SerialATA的縮寫,即串行ATA。它是一種電腦總線,主要功能是用作主板和大量存儲設備(如硬盤及光盤驅動器)之間的數據傳輸。

SAS:用于外設數據傳輸。串行SCSI(SAS:SerialAttachedSmallComputerSystemInterface)是一種電腦集線的技術,其功能主要是做外設的數據傳輸,如:硬盤、CD-ROM等設備而設計的接口。

SGMII:是一個普通高速串行信號,SGMII--SerialGigabitMediaIndependentInterface,用于MAC和PHY之間的傳輸。SGMII接口就是使用了SerDes技術的GMII接口。

自此以后,各類接口的速率開始毫無意外地以指數級增長,其中以光纖傳輸速率尤為明顯。上面還都僅是使用NRZ(PAM2)標準的接口,PAM4標準則以50Gb/s的傳輸速度起步并脫穎而出。

為了讓大家更好地理解電路級上的創新如何推動SERDES地發展進程,使用IEEE的Xplore數字圖書館查詢了國際固態電路會議(ISSCC)的出版物,生成了ISSCC出版物列表,其中包括關鍵字“時鐘和數據恢復”和“SERDES”。然后將數據集分解為一下4類:

工藝類型:CMOS和非CMOS(bipolar、biCMOS、HBT等)

工藝節點:65nm,40nm,7nm等。

信號傳輸標準:PAM2、PAM4

組織出版:工業、學術

注:HBT-heterojunctionbipolartransistor,異質結雙極型晶體管,其原理是因為不同的半導體材質,其能帶結構不一樣,兩者相處時的界面會因為能帶(費米能級相同)形成獨特的過渡層,因為多一個自由度,而能夠提取出優異的(同質結所沒有的)高速特性。

基于這些數據,以線速為縱軸,論文出版年份為橫軸繪制出下圖。據估計,電路設計完成時間大約在出版前一年,然而,新技術可能在出版幾年后才會在工業應用上出現。

線速-出版文獻年份分布情況(根據工藝類型劃分)

這個圖表明bipolar,biCMOS和HBT技術在2005年之前就已被大量研究,但是2005年以后就很少了。這些2005年前的論文描述了驅動光纖網絡應用的技術,其中線速是最重要的,而功耗、外形、集成則是次要的考慮因素。

對于具有更大容量的SERDES應用案例,如PC、存儲、視頻顯示和網絡,線速不再是人們考慮的唯一因素,成本、功耗、形狀以及和大規模數字處理器的集成都變成了必須要考慮的重要因素。

按照學術界和工業界以及PAM2和PAM4劃分的ISSCC數據情況。值得注意的一點是,PAM4和PAM2的論文大致以28Gb/s線速上下來劃分。這與串行數據標準的未來預期大致吻合。

CMOS工藝節點和線速之間的關系:90nm以下的工藝節點的大部分線速都在10Gb/s以上。另外,PAM4由于通常需要和ADC/DSP高度集成并且對帶寬有著非常高的要求(這是PAM2不具備的),因此通常在28nm工藝以下。

學術界關于PAM4的論文很少,這可能是由于設置了搜索條件引起的。學術界常常出版和PAM4“部件”相關的論文,但卻很少出版論述“完整”PAM4收發器的文獻。PAM4的系統太過龐大(包括ADCs,DACs,DSP,PLLs,CDRs等),并且先進的CMOS工藝(如7nm,14/16nm)的成本和獲取途徑對學術界并不友好。

將串行鏈路發布和串行數據率標準的搜索結果結合在一起,可以得到圖5中的信息,ISSCC的先進CMOS電路設計出版物在從網絡到顯示器的高容量串行數據標準方面領先了好幾年。PAM2CMOS的研究已經讓PCIe1到PCIe5(32Gb/s)、28Gb/s以太網線路速率等成果成為現實。

編輯:jq

-

串行接口

+關注

關注

3文章

326瀏覽量

42572

原文標題:SerDes的好處在哪里(上)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

scsi接口是串行還是并行

串行接口PCB設計指南:優化布局與布線策略

國產車載SerDes百花齊放,12G以上已是“基本操作”

串行接口的工作原理和結構

ASP4644在FPGA SERDES供電中的應用

FPGA的sata接口設計時需要注意哪些問題

簡單認識串行解串器

車載SerDes技術概述、特點和應用詳解

高速接口SerDes基礎知識總結

為什么串行接口(以SERDES為代表)變得如此流行

為什么串行接口(以SERDES為代表)變得如此流行

評論