電子發(fā)燒友網報道(文/周凱揚)隨著人工智能和機器學習的崛起,人工成本的提高,不少人類崗位被機器所替代,甚至許多重度依靠腦力活動的工作也在被危及,后端設計工程師就是其中之一。 EDA在不斷的迭代升級下,工程師們用起來也越來越得心應手,工作量都得到了簡化。但諸位后端設計工程師有沒有害怕自己吃飯的工具變得越來越智能,最終有一天替代自己?EDA

引入機器學習,是威脅還是福利?

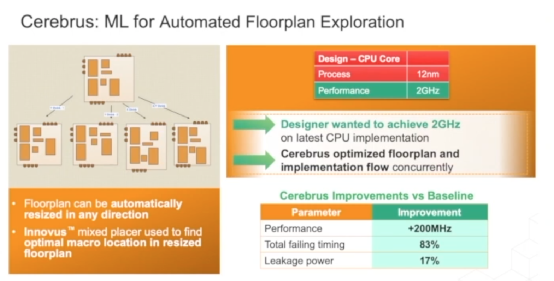

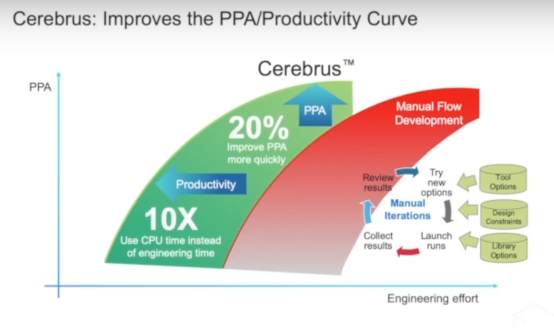

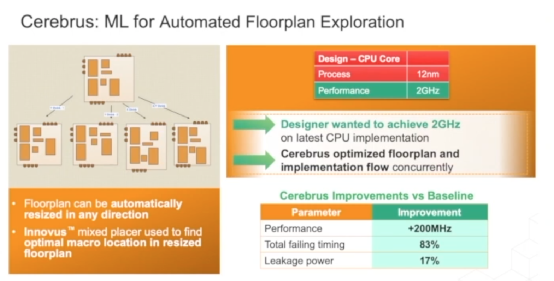

Cerebrus floorplan自動優(yōu)化 / Cadence 在Cadence給出的演示中,5nm手機CPU需要工程師團隊數月的工作,最終實現了3.5GHz的頻率。而在運用Cerebrus的幫助下,1名工程師在10天內的時間里就將頻率提升了420MH。這樣的生產力提升升可能是每個芯片設計公司都想要看到的結果,因為它消耗更多是CPU的時間而不是工程師自己的時間,更不用說可觀的性能提升了。 考慮到Cerebrus正是希臘神話中看守地獄的三頭犬Cerberus的易位詞,說不定對許多初級工程師來說真的象征著“地獄”之門大開。 但它真正的象征意義可能更接近于大腦“Cerebrum”,為工程師們提供一個擁有自主思考能力的工具,同時也幫助工程師構思更好的芯片設計。據外媒Anandtech了解到,Cadence提供的工具里還會加入回放功能。回放功能會記錄增強學習的過程中每一次迭代,這讓工程師可以更好地確定設計過程,并理解最終設計。

Cerebrus floorplan自動優(yōu)化 / Cadence 在Cadence給出的演示中,5nm手機CPU需要工程師團隊數月的工作,最終實現了3.5GHz的頻率。而在運用Cerebrus的幫助下,1名工程師在10天內的時間里就將頻率提升了420MH。這樣的生產力提升升可能是每個芯片設計公司都想要看到的結果,因為它消耗更多是CPU的時間而不是工程師自己的時間,更不用說可觀的性能提升了。 考慮到Cerebrus正是希臘神話中看守地獄的三頭犬Cerberus的易位詞,說不定對許多初級工程師來說真的象征著“地獄”之門大開。 但它真正的象征意義可能更接近于大腦“Cerebrum”,為工程師們提供一個擁有自主思考能力的工具,同時也幫助工程師構思更好的芯片設計。據外媒Anandtech了解到,Cadence提供的工具里還會加入回放功能。回放功能會記錄增強學習的過程中每一次迭代,這讓工程師可以更好地確定設計過程,并理解最終設計。

芯片設計上的人類VS機器學習,已有敗績

引入機器學習,是威脅還是福利?

許多頂尖的IC設計都需要在設計上進行優(yōu)化,從而改善我們常說的PPA(性能、功率、面積,有時還有成本)。在規(guī)劃好芯片架構,確定了工藝節(jié)點后,剩下的開發(fā)工作就是設計了。不少設計工作,需要工程師團隊數月的優(yōu)化,EDA廠商推出云方案之后,也有部分公司借助云方案來完成優(yōu)化和驗證工作,以求節(jié)省總開發(fā)周期。 以上過程的主導者依然是設計者本身,甚至不少設計者認為當今的芯片復雜度是機器學習和AI無法企及的,而且還在飛速增長中。然而在機器學習的演進下,EDA一直在研究如何將其引入軟件中去,為芯片設計帶來顛覆性的改變。

芯片設計上的人類VS機器學習,已有敗績

在這場人類與機器學習的設計大戰(zhàn)里,其實人類已經有過敗績了。今年6月9日,谷歌在《自然》雜志上發(fā)表了一篇論文,就講述了谷歌計劃用AI來設計下一代AI加速器(TPU)。 該論文著重說明了在機器學習在布局上的優(yōu)勢,自動布局布線已經不是什么新鮮事了,然而機器學習的引入還是為其算法帶來了大革新。論文稱復雜芯片的設計需太過耗時,工程師需要花上大量時間來布局和迭代其設計,每次設計后最多還要72小時來評估,最終導致工程時長拖到數月之久。 這在AI芯片公司尤其常見,不少大會上AI芯片公司大肆宣揚其核心設計,但最終芯片成品可能要數個月乃至一年后才能推出。只有設計評估工作順利進行,才會擁有比上一版更優(yōu)秀的PPA。 在谷歌的實驗中,他們根據大量網表和布局建立了一個神經網絡。同樣在6個小時的設計流程下,該方法生成的floorplan從各個層面上都優(yōu)于或近似于人類手工設計。

人機對比 / Nature

上圖就是谷歌曾經展示過的人機大戰(zhàn)結果,左圖為人工設計的floorplan,花費了6至8周的工作時間。而右圖是AI設計的floorplan,僅僅花費了24個小時。不過因為包含了機密設計,兩張圖都已經經過了模糊處理。

盡管從這些例子看來,工程師的位置岌岌可危,但這些并不是EDA引入機器學習的意義。Synopsys其實也早在去年推出了AI驅動的設計系統(tǒng)方案DSO.ai,其團隊在官方采訪中提到:DSO.ai之類方案并非芯片設計的“綠色按鈕”,一鍵按下交由AI自行操作。真正的權力依然掌握在設計者手中,只不過將不少設計工作從手動變?yōu)榱苏嬲饬x上的自動而已。

結語

雖然EDA確實都在逐步引入機器學習,但這與過去的升級其實性質無差,仍然是在為工程師省去重復性的優(yōu)化排錯工作。目前這些工具所能提供的依然是“AI輔助芯片設計”,而不是“AI自動設計芯片”。

“自己設計的AI芯片替代自己”的情況在很長一段時間內都不會發(fā)生的。再者,編者的工作可能會比諸位工程師更早一步被機器學習和AI替代,屆時,它們寫出的文章可能會換上一個更有威懾力的標題。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯系本站處理。

舉報投訴

-

eda

+關注

關注

71文章

2712瀏覽量

172939 -

后端設計

+關注

關注

0文章

13瀏覽量

8602

發(fā)布評論請先 登錄

相關推薦

eda在機器學習中的應用

在機器學習項目中,數據預處理和理解是成功構建模型的關鍵。探索性數據分析(EDA)是這一過程中不可或缺的一部分。 1. 數據清洗 數據清洗 是機器學習

【試用評選】為昕原理圖設計EDA軟件(Jupiter)試用活動評選結果公布

流程,功能設計更智能化,界面操作更人性化,讓硬件工程師使用得更愉悅、順暢。為昕科技旨在通過新技術提高硬件工程師設計原理圖的效率,加速完善國產EDA布局,面向電子系統(tǒng)/產品研發(fā)全流程,提供更高效、更智能

發(fā)表于 07-22 17:07

嵌入式軟件工程師和硬件工程師的區(qū)別?

、機器人等。 定義和工作職責 嵌入式軟件工程師的主要職責包括但不限于:設計、開發(fā)、測試和調試嵌入式軟件應用程序,以滿足特定硬件和軟件要求。他們需要理解并掌握嵌入式系統(tǒng)的基本原理,熟悉相關硬件接口

發(fā)表于 05-16 11:00

豪威集團 天津 招聘模擬電路設計工程師

工作職責

完成模擬電路的設計、仿真和驗證;

與版圖工程師密切合作,優(yōu)化版圖質量;

負責產品設計相關技術文檔的編寫和整理;

協作完成產品的測試規(guī)劃、設計驗證、調試、失效分析等工作。

任職資格

微電子

發(fā)表于 11-30 17:09

EDA引入機器學習,后端設計工程師集體失業(yè)?!

EDA引入機器學習,后端設計工程師集體失業(yè)?!

評論