最近,中科院微電子研究所劉明院士、李泠研究員團(tuán)隊(duì)在先進(jìn)邏輯工藝可靠性問題的緊湊模型取得最新研究成果,此研究成果以題為“A Unified Physical BTI Compact Model in Variability-Aware DTCO Flow: Device Characterization and Circuit Evaluation on Reliability of Scaling Technology Nodes”的文章入選2021 VLSI Technology。

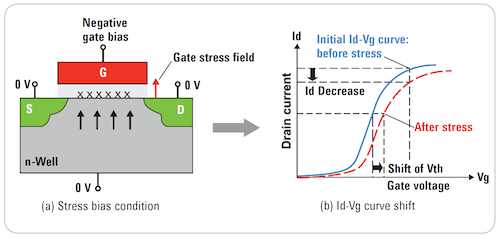

BTI效應(yīng)會(huì)影響到器件的使用,并隨著技術(shù)節(jié)點(diǎn)的降低,BTI逐漸成為器件可靠性的瓶頸,因此如何降低BTI效應(yīng)是器件可靠性的重要研究方向。下圖是PMOS碰到BTI問題后,器件性能受到影響,同樣NMOS也會(huì)有類似的問題,假如這種問題發(fā)生在像高密度的SRAM應(yīng)用中,會(huì)嚴(yán)重影響 static noise margin (SNM) and write noise margin (WNM) 。

圖1 PMOS NBTI的原理,和對(duì)器件性能的影響

在這種背景下,偏置溫度不穩(wěn)定(BTI)效應(yīng)成為集成電路(IC)器件可靠性的關(guān)鍵問題之一,微電子所團(tuán)隊(duì)開發(fā)了一個(gè)統(tǒng)一的物理和統(tǒng)計(jì)緊湊模型,可以預(yù)測(cè)BTI對(duì)不同工藝節(jié)點(diǎn)的器件及電路(低至14nm)的影響,包含復(fù)雜的應(yīng)力/恢復(fù)模式表征、超長期老化預(yù)測(cè)和工藝統(tǒng)計(jì)變量(TSV)的影響,實(shí)現(xiàn)cycle to cycle/device to device的可靠性評(píng)估。

該模型基于2/4態(tài)的缺陷中心(DC)理論,針對(duì)缺陷的物理特性(如能級(jí)分布、占據(jù)概率等)建模。通過TCAD仿真驗(yàn)證和對(duì)鰭狀場(chǎng)效應(yīng)晶體管(FinFET)、平面晶體管等可靠性實(shí)驗(yàn)測(cè)試結(jié)果的校準(zhǔn),成功地嵌入了BSIM-CMG通用模型,用于器件及電路的動(dòng)態(tài)時(shí)間演化和動(dòng)態(tài)電壓縮放分析。這種物理的、可變性的和具有耐久性感知的緊湊模型有潛力將VLSI可靠性設(shè)計(jì)技術(shù)協(xié)同優(yōu)化(DTCO)流程提升到下一代技術(shù)節(jié)點(diǎn)。

隨著節(jié)點(diǎn)的提升,Design for reliability 變得越來越重要,因?yàn)橐淮瘟髌O(shè)計(jì)價(jià)格不菲,很多中小企業(yè)禁不起幾輪流片失敗。因此,如何把BTI等可靠性模型嵌入現(xiàn)有設(shè)計(jì)中,顯得尤其重要。同時(shí),如果有了這個(gè)武器,設(shè)計(jì)帶來的附加價(jià)值和壽命就會(huì)明顯提高。

隨著電子產(chǎn)品應(yīng)用的廣泛,在不同領(lǐng)域,比如汽車、醫(yī)療、工業(yè)、航天天空及國防應(yīng)用等產(chǎn)品都會(huì)遇到生命週期可靠性的問題,因此,在這個(gè)層面,基于半導(dǎo)體廠工藝的模型開發(fā)是重中之重,同時(shí)如何和EDA廠商合作,獲得接近產(chǎn)品實(shí)際特性的仿真結(jié)果也有很多協(xié)同工作要做。

有一點(diǎn)可以確認(rèn),模型從業(yè)人員通過模型二次開發(fā)的核心價(jià)值來獲得獨(dú)特的設(shè)計(jì)這個(gè)角度去看,相信將來會(huì)有很多基于模型擴(kuò)展基礎(chǔ)上的小而美的設(shè)計(jì)公司創(chuàng)立,因?yàn)闅W洲已經(jīng)有很多創(chuàng)新公司值得我們借鑒。

編輯:jq

-

器件

+關(guān)注

關(guān)注

4文章

307瀏覽量

27796

原文標(biāo)題:偏置溫度不穩(wěn)定(BTI)的模型開發(fā)應(yīng)用

文章出處:【微信號(hào):弘模半導(dǎo)體,微信公眾號(hào):弘模半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于偏置溫度不穩(wěn)定(BTI)的技術(shù)

基于偏置溫度不穩(wěn)定(BTI)的技術(shù)

評(píng)論