本文主要包含MultiBoot的功能簡介、流程介紹和工程實現(xiàn)幾個部分的講解。

我們先從它的功能介紹講起來;MultiBoot功能是大部分Xilinx FPGA可以實現(xiàn)的固有特性;其主要優(yōu)點如下所示:

1、我們可以把多個bitstream存儲在配置Flash中,通過MultiBoot功能來實現(xiàn)多個bitstream之間的動態(tài)切換,從而達到使用FPGA來實現(xiàn)多種任務(wù);

2、在一個工程里面實現(xiàn)多個功能模塊,而每個功能模塊不需要同時運行的情況,可以通過MultiBoot功能使用相對小規(guī)模的FPGA來實現(xiàn)其功能,從而提高性價比;

3、MultiBoot和Fallback可以支持實現(xiàn)FPGA遠程在線升級,當升級bit有錯誤可以觸發(fā)Fallback來返回到Golden Image去正常運行。

Golden Image里面正常會包含F(xiàn)PGA實現(xiàn)的基本功能,例如外設(shè)配置和初始化、遠程升級等等客戶需要的基本功能;如果Golden Image損壞的情況下,F(xiàn)PGA是無法工作的,需要返回工廠重新手動燒寫bit文件到Flash中。

Golden Image設(shè)計要求主要包含下面幾點:

1、IPROG(Internal program) command在Golden Image里面可以通過設(shè)置bitstream setting里面的next configuration address (BITSTREAM.CONFIG.NEXT_CONFIG_ADDR),或者在HDL代碼使用ICAPE3原語來設(shè)定加載地址值;通過設(shè)置BITSTREAM.CONFIG.NEXT_CONFIG_REBOOTDISABLE來把

IPROG command關(guān)掉,在這種情況下上電后會直接去加載Golden Image;

2、跳轉(zhuǎn)地址寄存器WBSTAR(warm boot start address)可以在bitstream或者ICAP里面來設(shè)定;

3、MultiBoot Image必須存儲在WBSTAR設(shè)置的Flash地址位置;

4、Watchdog timer包含configuration monitor和user logic monitor兩種模式;在配置模式下面,Timer times out情況下,配置電路會去加載fallback bitstream。Watchdog Timer可以在bitstream options里面使能。

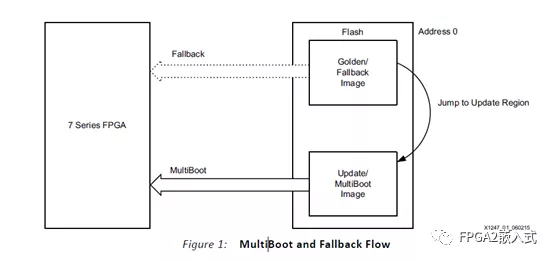

Golden Image是從Flash中的0地址開始存儲;其幀頭會包括WBSTAR(next_config_addr)寄存器里面指定的upper address space等信息。FPGA器件上電后會從0地址開始加載Golden Image后,會根據(jù)里面的設(shè)定來決定加載Golden Image還是直接跳轉(zhuǎn)到MultiBoot Image存儲地址去執(zhí)行MultiBoot Image;當MultiBoot Image加載時候遇到錯誤,F(xiàn)allback電路會觸發(fā)去重新從0地址去加載Golden Image。

MultiBootImage是從設(shè)定好的upper address space去加載運行;如果加載出現(xiàn)問題,F(xiàn)allback電路會去加載Golden Image。我們可以在Golden Image里面去修復(fù)Multiboot Image里面的錯誤等等問題。所以說MultiBoot Image里面運行的就是我們要實現(xiàn)的具體業(yè)務(wù)功能,可以是多個Multiboot Image。

Golden Image設(shè)計要求主要包含下面幾點:

1、WBSTAR里面的值要指向MultiBoot存儲位置;

2、Watchdog Timer功能要bitstream options里面使能;

3、代碼里面可以通過IPROG命令去運行ICAPE3來跳轉(zhuǎn)想要運行其他的MultiBoot Image。

在配置過程中遇到IDCODE error、CRC error、Watchdog timer timeout error、BPI address wraparound error情況會觸發(fā)fallback。Fallback功能可以通過使能bitstream.config.configfallback enable里面的ConfigFallback選項來實現(xiàn)。當fallback運行時,Watchdog TimerIPROG是disable的;另外當fallback重新配置FPGA出錯情況下,配置電路會停止工作同時會把INIT_BDone保持為低電平。

MultiBoot功能可以通過設(shè)置下面bitstream里面的參數(shù)來實現(xiàn)。這些參數(shù)可以通過Tcl console或者寫入到XDC文件里面來實現(xiàn)其功能。

在前面介紹其功能作用和含義等等后,下面我們開始工程實現(xiàn)。

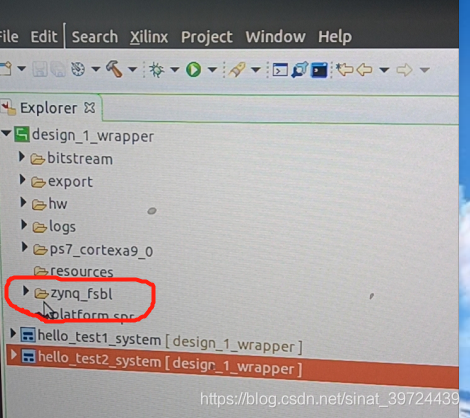

本人使用Vivado版本為2020.2;硬件基于米聯(lián)客設(shè)計的KU040板卡。先建立Golden Image的工程,里面包括HDL文件和XDC約束。

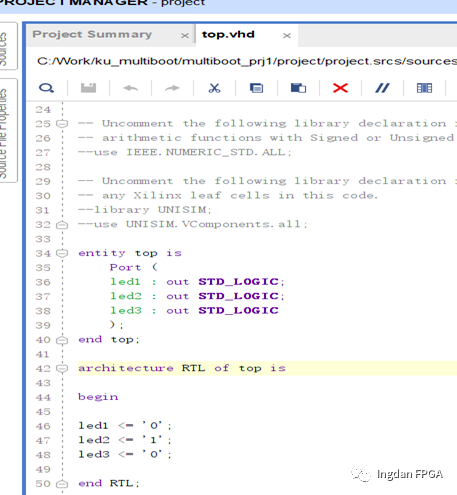

GoldenImage的工程里面代碼主要是把led1燈點亮。XDC里面包括IO約束信息等等,其中0x040000是Multiboot Image存放Flash里面的物理地址。

Multiboot Image led2的工程里面代碼主要是把led1燈點亮。XDC里面包括IO約束和配置約束信息等等,可以看到是和Golden Image工程里面約束是有差異的。

在工程建立完成后開始合并bit文件并燒入到板卡里面:

1、使用下面tcl去把兩個bit文件合為一個mcs文件;

2、通過Hardware Manager去燒入到板卡的Flash中;3、燒寫完成后選擇Boot from Configuration Memory Devive去加載FPGA。4、在FPGA加載后可以看到板卡上面LED2燈點亮。

5、在Hardware Device Properties的BOOT_STATUS里面可以看到INTERNAL_PROG使能;由于加載沒有錯誤,目前運行的是Multiboot程序。CONFIG_SATUS里面可以看到DON_PIN拉高。

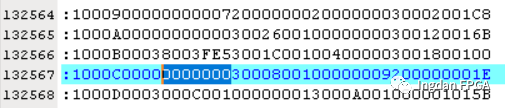

下面我們嘗試把multiboot image里面的IDCODE修改掉,人為的造成錯誤來驗證板卡是否會跳轉(zhuǎn)到Golden Image去執(zhí)行。1、使用UltraEdit把ku_multiboot_spix4.mcs打開后,搜索到Update.bit里面的KU040的IDCODE3822093,并把它修改為0;重新生成ku_multiboot_spix4 _id.mcs文件燒入到FPGA.

2、按照前面流程合成bit文件后燒入到Flash中并上電;3、在FPGA加載后可以看到板卡上面LED1燈點亮;證明Fallback功能生效,當Multiboot Image損壞后可以安全加載Golden Image。

4、在Hardware Device Properties的BOOT_STATUS里面可以看到INTERNAL_PROG使能,ID_ERROR拉高;這時候Multiboot Image加載遇到ID錯誤,F(xiàn)PGA返回到Golden Image去運行。

我們可以再嘗試把multiboot image其他部分破壞掉導(dǎo)致CRC出錯來驗證功能。

1、使用UltraEdit把ku_multiboot_spix4.mcs打開后,在Update.bit里面做如下修改來驗證CRC錯誤情況。

2、燒入到板卡上電后;由于multiboot image里面有CRC錯誤,所以板卡還是返回到Golden Image去運行。

除了前面我們在bitstream里面去實現(xiàn)Multiboot功能,我們還可以在代碼里面嵌入IPROG的命令來實現(xiàn)Image的跳轉(zhuǎn)功能。

我們可以在點亮LED2的那個工程來做相關(guān)修改:

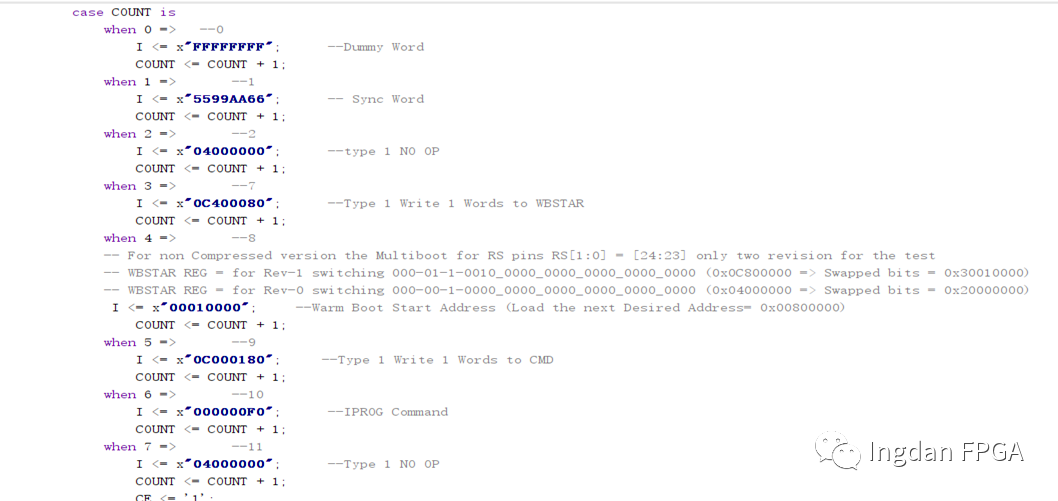

1、我們在點LED2燈的MultiBoot Image LED2工程里面加入ICAPE3代碼;

2、根據(jù)前面命令流程圖在代碼里面實現(xiàn)其功能;其中Warm Boot Start Address要跟bit文件在Flash里面位置對應(yīng)起來,不然跳轉(zhuǎn)后會找不到對應(yīng)的image導(dǎo)致失敗。

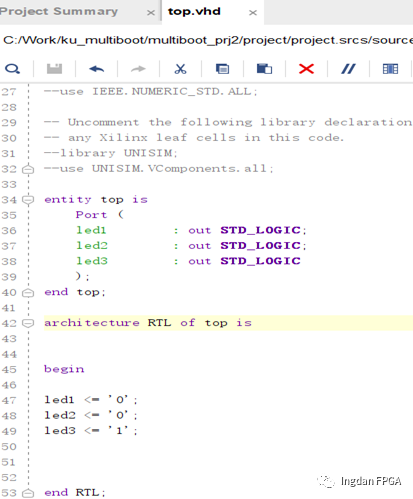

3、建立點亮MultiBoot Image LED3工程來配合前面IPROG命令功能;這樣可以通過MultiBoot Image LED2 工程里面的IPROG命令在FPGA不斷電的情況下實時把切換MultiBoot Image LED3到工程來點亮LED3。

4、使用下面tcl去把兩個bit文件合為一個mcs文件;

5、燒寫完成后選擇Boot from Configuration Memory Devive去加載FPGA,然后通過外置按鍵來執(zhí)行MultiBoot Image LED2 工程里面的IPROG命令去實現(xiàn)跳轉(zhuǎn)。

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1626文章

21671瀏覽量

601914

原文標題:Xilinx FPGA的MultiBoot功能介紹和實現(xiàn)

文章出處:【微信號:TheAlgorithm,微信公眾號:算法與數(shù)據(jù)結(jié)構(gòu)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

AMD Xilinx 7系列FPGA的Multiboot多bit配置

7 series FPGAs SPI MultiBoot應(yīng)用筆記

有什么辦法可以更快地為Main_multiboot.mcs獲得總的舞會校驗和嗎?

如何為MultiBoot生成SPIx4模式閃存文件

如何使用BPI閃存的Spartan 6 Multiboot功能

如何創(chuàng)建Golden鏡像和Multiboot鏡像?

Xilinx-Spartan6 FPGA實現(xiàn)MultiBoot

如何使用FPGA的Multiboot功能實現(xiàn)系統(tǒng)升級更新

關(guān)于Xilinx公司出品的Spartan6系列FPGA的MultiBoot設(shè)計方案詳解

屏障定時器流程測試方法以及使用此方法

7 eries FPGAs SPI MultiBoot實現(xiàn)方式

在FPGA中如何通過ICAP原語實現(xiàn)Multiboot?

深入探究Xilinx Multiboot實例

multiboot什么意思 MultiBoot的功能簡介、流程介紹

multiboot什么意思 MultiBoot的功能簡介、流程介紹

評論