最近在準備MBA,就經(jīng)常會聊到行業(yè)。一說我在做芯片,在半導(dǎo)體行業(yè),其它行業(yè)的兄弟姐妹們都會覺得這個行業(yè)很高大上。但其實,半導(dǎo)體也是發(fā)展了好幾十年了,這個行業(yè)很類似于房地產(chǎn)。下面我就用房地產(chǎn)舉例子來和大家說說半導(dǎo)體。

那么,到底什么是芯片呢?就是縮微的小區(qū)樓盤。

第一步:前期規(guī)劃

在首先要做一顆芯片,需要公司做市場調(diào)研,確定市場的需求,比如最近比較火爆的人工智能芯片、5G芯片、物聯(lián)網(wǎng)芯片等,對大方向做設(shè)定。

接著是芯片規(guī)格的制定,這是最重要的步驟,包括芯片需要達到的具體功能和性能方面的要求。它就像是在設(shè)計建筑前,先決定要幾間房間、浴室,有什么建筑法規(guī)需要遵守。

在確定好功能和性能之后,接著是察看有哪些協(xié)定要符合,才能確保設(shè)計出來的芯片不會有任何差錯。像無線網(wǎng)卡的芯片就需要符合IEEE 802.11等規(guī)范,不然,設(shè)計出來的芯片將無法和市面上的產(chǎn)品相容。

最后則是確立這顆IC的實作方法,將不同功能分配成不同的單元,并確立不同單元間連結(jié)的方法,規(guī)格的制定就完成了。

第二步:設(shè)計并畫圖紙

根據(jù)客戶提出的規(guī)格要求,制定設(shè)計解決方案和具體實現(xiàn)架構(gòu),劃分模塊功能,然后就是設(shè)計芯片的細節(jié)了。這個步驟就像初步記下建筑的規(guī)畫,將整體輪廓描繪出來,方便后續(xù)制圖。在IC芯片中,使用硬件描述語言(VHDL,Verilog HDL,業(yè)界公司一般都是使用后者)將模塊功能以代碼來描述實現(xiàn),也就是將實際的硬件電路功能通過HDL語言描述出來,形成RTL(寄存器傳輸級)代碼。

接著就是仿真驗證,它是檢驗編碼設(shè)計的正確性,看設(shè)計是否精確地滿足了規(guī)格中的所有要求。規(guī)格是設(shè)計正確與否的黃金標準,一切違反,不符合規(guī)格要求的,就需要重新修改設(shè)計和編碼。設(shè)計和仿真驗證是反復(fù)迭代的過程,直到驗證結(jié)果顯示完全符合規(guī)格標準。

仿真驗證通過,進行邏輯綜合

有了完整規(guī)劃后,接下來便是畫出平面的設(shè)計藍圖。在IC設(shè)計中,邏輯綜合是將電路的行為級描述,特別是RTL級描述轉(zhuǎn)化成為門級表達的過程,也就是將代碼翻譯成各種實際的元器件。綜合需要設(shè)定約束條件,就是你希望綜合出來的電路在面積,時序等目標參數(shù)上達到的標準。邏輯綜合需要基于特定的綜合庫,不同的庫中,門電路基本標準單元(standard cell)的面積,時序參數(shù)是不一樣的。所以,選用的綜合庫不一樣,綜合出來的電路在時序,面積上是有差異的。一般來說,綜合完成后需要再次做仿真驗證。

接著就是靜態(tài)時序分析,也就是套用特定的時序模型,針對特定電路分析其是否違反設(shè)計者給定的時序限制。然后是形式驗證,這也是驗證范疇,它是從功能上(STA是時序上)對綜合后的網(wǎng)表進行驗證。

從設(shè)計程度上來講,前面操作的結(jié)果就是得到了芯片的門級網(wǎng)表電路。

然后是DFT(可測性設(shè)計)?單元布局((FloorPlan) ?時鐘樹綜合(CTS) ?布線(Place & Route) ? 版圖物理驗證

DFT(可測性設(shè)計)。芯片內(nèi)部往往都自帶測試電路,DFT的目的就是在設(shè)計的時候就考慮將來的測試,目的是在設(shè)計的時候就考慮將來的測試。

時鐘樹綜合(CTS):簡單點說就是時鐘的布線。由于時鐘信號在數(shù)字芯片的全局指揮作用,它的分布應(yīng)該是對稱式的連到各個寄存器單元,從而使時鐘從同一個時鐘源到達各個寄存器時,時鐘延遲差異最小。這也是為什么時鐘信號需要單獨布線的原因。

布線(Place & Route):包括各種標準單元(基本邏輯門電路)之間的走線。

版圖物理驗證:對完成布線的物理版圖進行功能和時序上的驗證。

整個IC設(shè)計流程都是一個迭代的過程,每一步如果不能滿足要求,都要重復(fù)之前的過程,直至滿足要求為止,才能進行下一步。

物理版圖驗證完成也就是整個芯片設(shè)計階段完成,下面的就是芯片制造了。

第三步,打地基,選材料

晶圓(wafer),是制造各式電腦芯片的基礎(chǔ)。我們可以將芯片制造比擬成用樂高積木蓋房子,經(jīng)過一層又一層的堆疊,完成自己期望的造型(也就是各式芯片)。然而,如果沒有良好的地基,蓋出來的房子就會歪來歪去,不合自己所意,為了做出完美的房子,便需要一個平穩(wěn)的基板。對芯片制造來說,這個基板就是接下來將描述的晶圓。

晶圓的概念

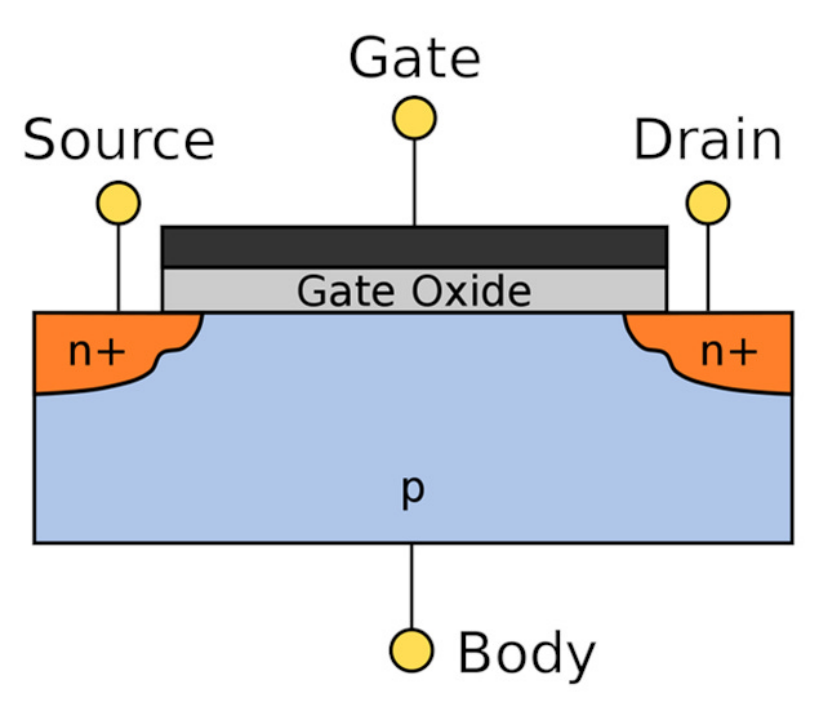

晶圓是指硅半導(dǎo)體集成電路制作所用的硅晶片,由于其形狀為圓形,故稱為晶圓;在硅晶片上可加工制作成各種電路元件結(jié)構(gòu),而成為有特定電性功能的IC產(chǎn)品。

首先,先回想一下小時候在玩樂高積木時,積木的表面都會有一個一個小小圓型的凸出物,經(jīng)過這個構(gòu)造,我們可將兩塊積木穩(wěn)固的疊在一起,且不需使用膠水。芯片制造,也是以類似這樣的方式,將后續(xù)添加的原子和基板固定在一起。因此,我們需要尋找表面整齊的基板,以滿足后續(xù)制造所需的條件。

在固體材料中,有一種特殊的晶體結(jié)構(gòu)──單晶(Monocrystalline)。它具有原子一個接著一個緊密排列在一起的特性,可以形成一個平整的原子表層。因此,采用單晶做成晶圓,便可以滿足以上的需求。

一整條的硅柱并無法做成芯片制造的基板,為了產(chǎn)生一片一片的硅晶圓,接著需要以鉆石刀將硅晶柱橫向切成圓片,圓片再經(jīng)由拋光便可形成芯片制造所需的硅晶圓。經(jīng)過這么多步驟,芯片基板的制造便大功告成,下一步便是堆疊房子的步驟,也就是芯片制造。

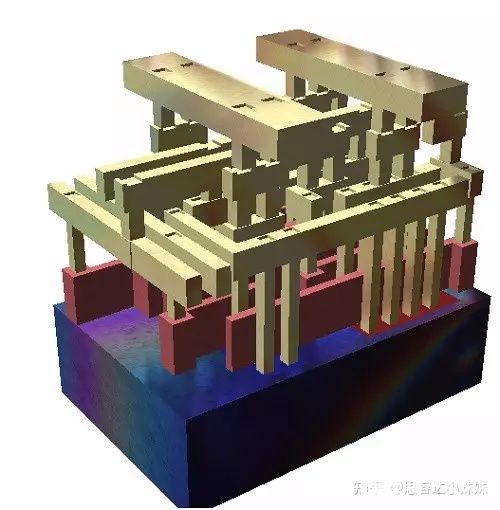

IC,全名積體電路(Integrated Circuit),由它的命名可知它是將設(shè)計好的電路,以堆疊的方式組合起來。使用這個方法,我們可以減少連接電路時所需耗費的面積。下圖為 IC電路的3D圖,從圖中可以看出它的結(jié)構(gòu)就像房子的樑和柱,一層一層堆疊,這也就是為何會將IC制造比擬成蓋房子。

▲ IC芯片的3D剖面圖。(Source:Wikipedia)

▲ IC芯片的3D剖面圖。(Source:Wikipedia)

第四步:裝修——芯片叫封裝測試

什么是封裝?

是指安裝半導(dǎo)體集成電路芯片用的外殼,起著安放、固定、密封、保護芯片和增強電熱性能的作用,是溝通芯片內(nèi)部世界與外部電路的橋梁(芯片上的接點用導(dǎo)線連接到封裝外殼的引腳上,這些引腳又通過印制板上的導(dǎo)線與其它器件建立連接)。

芯片封裝的作用主要有四個方面:固定引腳系統(tǒng)、物理性保護、環(huán)境性保護和增強散熱。

按照包裝材料,封裝可以分為:金屬封裝、陶瓷封裝和塑料封裝。

按照封裝外形可分類為:SOT、QFN、SOIC、TSSOP、QFP、BGA、CSP,這個是按照封裝形式和工藝越來越高級和復(fù)雜來排序。

完成封裝后,便要進入測試的階段。

芯片測試的過程是將封裝后的芯片置于各種環(huán)境下測試其電氣特性,如消耗功率、運行速度、耐壓度等。經(jīng)測試后的芯片,依其電氣特性劃分為不同等級。而特殊測試則是根據(jù)客戶特殊需求的技術(shù)參數(shù),從相近參數(shù)規(guī)格、品種中拿出部分芯片,做有針對性的專門測試,看是否能滿足客戶的特殊需求,以決定是否須為客戶設(shè)計專用芯片,正確無誤之后便可出貨給組裝廠,做成我們所見的電子產(chǎn)品。至此,半導(dǎo)體產(chǎn)業(yè)便完成了整個生產(chǎn)的任務(wù)。

第五步:對外銷售

房地產(chǎn)大家遇到的套路很多,芯片的叫做推廣,英文是“Promote"。一般房子銷售都是各種推介會,各種小廣告,芯片銷售跟這個有點類似,但也不一樣。比如都要打廣告、舉辦各種線下會議,讓人家知道你。還有,就是房子銷售要定制化需求,通過裝修滿足你的定制化需求,而芯片則是通過方案商完成差異化定制化。

第六步:售后

房子售后就是物業(yè)管理,如果房子有點小問題,物業(yè)要及時解決,讓業(yè)主住的舒心。如果地產(chǎn)商口碑好,則以后的房子大家都愿意買。芯片售后也是一樣的道理,要客戶用的安心,如果有小問題要及時解決,這樣客戶就會一直使用你的產(chǎn)品。如果口碑好,更多人就愿意用你的芯片。

通過以上的解釋,希望大家對半導(dǎo)體、對芯片有一個更為鮮活的了解。小編不易,歡迎贊賞!

-

芯片

+關(guān)注

關(guān)注

453文章

50406瀏覽量

421813 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27010瀏覽量

216295 -

封裝

+關(guān)注

關(guān)注

126文章

7784瀏覽量

142723 -

芯片設(shè)計

+關(guān)注

關(guān)注

15文章

1001瀏覽量

54811

發(fā)布評論請先 登錄

相關(guān)推薦

中國半導(dǎo)體的鏡鑒之路

使用tSPI協(xié)議減少下一個多電機BLDC設(shè)計的布線

使用CS1232 采集一個小信號,信號有可能是正,也可能是負 ,是不知道怎么回事情?

半導(dǎo)體發(fā)展的四個時代

半導(dǎo)體發(fā)展的四個時代

半導(dǎo)體放電管TSS:原理及在電子領(lǐng)域的應(yīng)用?|深圳比創(chuàng)達電子EMC a

半導(dǎo)體放電管TSS:原理及在電子領(lǐng)域的應(yīng)用?|深圳比創(chuàng)達電子EMC

為什么GaN被譽為下一個主要半導(dǎo)體材料?

三防加固平板在房地產(chǎn)行業(yè)的應(yīng)用

萬業(yè)企業(yè)年報預(yù)告:房地產(chǎn)利潤下滑,半導(dǎo)體設(shè)備收入飆升

半導(dǎo)體芯片結(jié)構(gòu)分析

半導(dǎo)體的特征及工藝介紹

1分鐘讀懂芯片設(shè)計 何為半導(dǎo)體?它可能是下一個房地產(chǎn) 比一比

1分鐘讀懂芯片設(shè)計 何為半導(dǎo)體?它可能是下一個房地產(chǎn) 比一比

評論