隨著設(shè)計(jì)復(fù)雜度和調(diào)用IP豐富度的增加,在調(diào)試時(shí)序約束的過(guò)程中,用戶常常會(huì)對(duì)除了自己設(shè)定的約束外所涉及的繁雜的時(shí)序約束感到困惑而無(wú)從下手。舉個(gè)例子,我的XDC里面并沒(méi)有指定set_false_path,為什么有些路徑在分析時(shí)忽略了?我怎么去定位這些約束是哪里設(shè)定的?

事實(shí)上,Vivado集成設(shè)計(jì)環(huán)境提供了很多輔助工具來(lái)協(xié)助用戶完成時(shí)序約束的分析。

本文結(jié)合一個(gè)具體案例,闡述了如何追溯同一時(shí)鐘域內(nèi)partial false path的來(lái)源,希望為開(kāi)發(fā)者的設(shè)計(jì)調(diào)試提供一些技巧和竅門(mén)。

首先來(lái)看問(wèn)題。

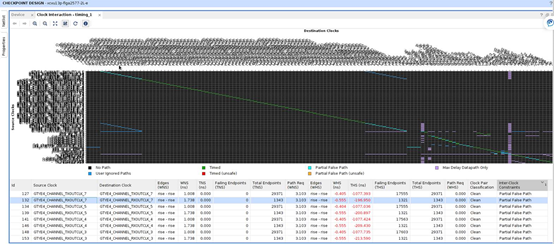

在此設(shè)計(jì)中,當(dāng)用report clock interaction查看時(shí)鐘關(guān)系時(shí),注意到不少單時(shí)鐘域被標(biāo)注成了partial false path。對(duì)于一個(gè)約束文件眾多,約束較為復(fù)雜的設(shè)計(jì),如何進(jìn)一步推斷partial false path有哪些路徑,是被哪些約束覆蓋了呢?

以其中的一個(gè)時(shí)鐘域GTYE4_CHANNEL_RXOUTCLK_7為例:

Step1:關(guān)閉merging timing exceptions

運(yùn)行Tcl命令讓時(shí)序工具不要合并時(shí)序異常約束。

config_timing_analysis -merge_exceptions false

要注意的是,這種模式會(huì)導(dǎo)致更長(zhǎng)的運(yùn)行時(shí)間和更大的內(nèi)存占用,因此不推薦默認(rèn)情況下將時(shí)序工具保持在此模式下。

調(diào)試完成后,要恢復(fù)到默認(rèn)模式,請(qǐng)將-merge_exceptions 的值設(shè)置為 True。

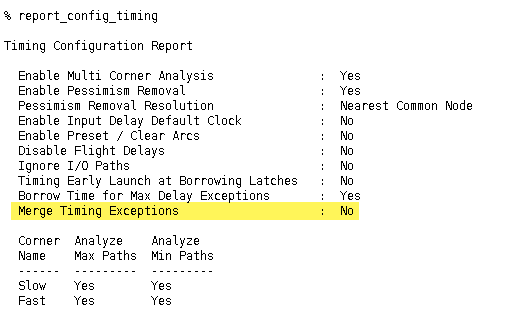

你可以用report_config_timing來(lái)報(bào)告exception merge的情況。

Step2:產(chǎn)生詳細(xì)的時(shí)序路徑報(bào)告

如果你只是要快速瀏覽路徑的起始元件,可運(yùn)行以下Tcl命令:

join [get_timing_paths -max_paths 100 -user_ignored -from [get_clocks GTYE4_CHANNEL_RXOUTCLK_7] -to [get_clocks GTYE4_CHANNEL_RXOUTCLK_7]]

返回會(huì)分行顯示partial false path的startpoint和endpoint。

{gen_die_comm_top[1].leda_die_comm_top_int/gen_cmac[3].u_hard_caui4_top_wrapper_inst/u_cmac_usplus_0/inst/i_cmac_usplus_0_cmac_cdc_sync_gt_txresetdone_int3/s_out_d4_reg/C --》 gen_die_comm_top[1].leda_die_comm_top_int/gen_cmac[3].u_hard_caui4_top_wrapper_inst/u_cmac_usplus_0/inst/i_cmac_usplus_0_top/obsibdaaf4ker2wujpra0sjb/RX_SERDES_RESET[0]}

{gen_die_comm_top[1].leda_die_comm_top_int/gen_cmac[3].u_hard_caui4_top_wrapper_inst/u_cmac_usplus_0/inst/i_cmac_usplus_0_cmac_cdc_sync_gt_txresetdone_int3/s_out_d4_reg/C --》 gen_die_comm_top[1].leda_die_comm_top_int/gen_cmac[3].u_hard_caui4_top_wrapper_inst/u_cmac_usplus_0/inst/i_cmac_usplus_0_top/obsibdaaf4ker2wujpra0sjb/RX_SERDES_RESET[3]}

{gen_die_comm_top[1].leda_die_comm_top_int/gen_cmac[3].u_hard_caui4_top_wrapper_inst/u_cmac_usplus_0/inst/i_cmac_usplus_0_cmac_cdc_sync_gt_txresetdone_int3/s_out_d4_reg/C --》 gen_die_comm_top[1].leda_die_comm_top_int/gen_cmac[3].u_hard_caui4_top_wrapper_inst/u_cmac_usplus_0/inst/i_cmac_usplus_0_top/obsibdaaf4ker2wujpra0sjb/RX_SERDES_RESET[2]}

{gen_die_comm_top[1].leda_die_comm_top_int/gen_cmac[3].u_hard_caui4_top_wrapper_inst/u_cmac_usplus_0/inst/i_cmac_usplus_0_cmac_cdc_sync_gt_txresetdone_int3/s_out_d4_reg/C --》 gen_die_comm_top[1].leda_die_comm_top_int/gen_cmac[3].u_hard_caui4_top_wrapper_inst/u_cmac_usplus_0/inst/i_cmac_usplus_0_top/obsibdaaf4ker2wujpra0sjb/RX_SERDES_RESET[1]}

為了得到我們所需的更詳細(xì)信息,可在Clock Interaction Report表格中,選中GTYE4_CHANNEL_RXOUTCLK_7這個(gè)時(shí)鐘域,右鍵菜單選擇Report Timing,

并且在設(shè)置對(duì)話框的Advanced標(biāo)簽卡中勾選Report user ignored paths選項(xiàng)。

對(duì)應(yīng)的Tcl命令為:

report_timing -from [get_clocks GTYE4_CHANNEL_RXOUTCLK_7] -to [get_clocks GTYE4_CHANNEL_RXOUTCLK_7] -delay_type min_max -max_paths 10 -sort_by group -input_pins -routable_nets -user_ignored -name timing_3

當(dāng)然,你可以根據(jù)需要增大max_paths的數(shù)目,以便更完整地包含所有路徑。

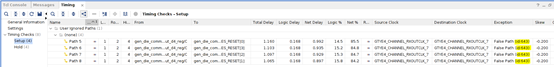

運(yùn)行結(jié)果如下圖,可以看到,除了常規(guī)的時(shí)序路徑信息,Exception一列還額外羅列了約束ID。

Step3:查找約束ID

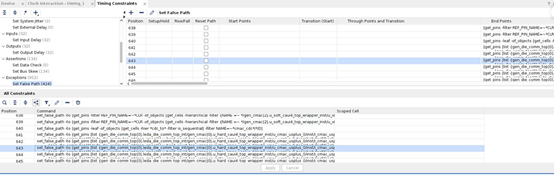

這個(gè)ID反映的是Constraint position,我們可以打開(kāi)Timing Constraints窗口,非常直觀方便地定位這個(gè)ID所對(duì)應(yīng)的約束語(yǔ)句。

Timing Constraints窗口僅對(duì)Synthesized Design或Implemented Design適用。你可以通過(guò)以下三種方式之一找到其入口(截圖匹配Vivado 2020.2版本):

Open Synthesized/Implemented Design,選擇菜單Windows 》 Timing Constraints

Open Synthesized Design,選擇Flow Navigator里Synthesized Design部分的Edit Timing Constraints

Open Implemented Design,選擇Flow Navigator里Implemented Design部分的Edit Timing Constraints

打開(kāi)后,在All Constraints子窗口下拉找到Position一列為643的約束語(yǔ)句,如圖所示:

選中此行約束,可以看到右上可視化表格的同條約束也自動(dòng)被選中,向右拉到Source File一列可以看到約束所在的XDC文件,或者在All Constraints窗口上翻到此約束所在的層次,同樣會(huì)列出XDC文件的具體信息。

如果你偏好Tcl模式,也可以用write_xdc導(dǎo)出帶有ID的所有時(shí)序約束。

write_xdc -type timing -write_id timing.xdc

不過(guò)-write_id選項(xiàng)僅在2020.2及之后版本才支持。

至此,我們已經(jīng)定位了partial false path的路徑細(xì)節(jié)及約束來(lái)源。

如前所述,調(diào)試完約束后,請(qǐng)將-merge_exceptions設(shè)回默認(rèn)值true,以免對(duì)運(yùn)行時(shí)間及內(nèi)存產(chǎn)生負(fù)面影響。

文中的方式可以應(yīng)用到所有諸如此類(lèi)“哪些約束覆蓋了此路徑“的疑問(wèn)解答上,希望對(duì)各位開(kāi)發(fā)者的時(shí)序調(diào)試有所幫助。

編輯:jq

-

True

+關(guān)注

關(guān)注

0文章

9瀏覽量

11946 -

TCL

+關(guān)注

關(guān)注

10文章

1715瀏覽量

88471 -

集成設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

4瀏覽量

7499 -

Vivado

+關(guān)注

關(guān)注

19文章

808瀏覽量

66329

原文標(biāo)題:開(kāi)發(fā)者分享 | 約束調(diào)試案例分析-如何判斷路徑的 timing exception 約束來(lái)自哪里?

文章出處:【微信號(hào):TheAlgorithm,微信公眾號(hào):算法與數(shù)據(jù)結(jié)構(gòu)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA設(shè)計(jì)中有多個(gè)時(shí)鐘域時(shí)如何處理?

【時(shí)序約束】和阿東一起學(xué)習(xí)時(shí)序約束之異步時(shí)鐘約束 set_false_path

【時(shí)序約束】和阿東一起學(xué)習(xí)時(shí)序約束之異步時(shí)鐘約束 set_false_path

【時(shí)序約束】關(guān)于設(shè)置FALSE PATH

跨時(shí)鐘域的時(shí)鐘約束介紹

為什么Vivado沒(méi)有在CCIO的同一時(shí)鐘區(qū)域選擇MMCM?

同步從一個(gè)時(shí)鐘域到另一個(gè)時(shí)鐘域的多位信號(hào)怎么實(shí)現(xiàn)?

基于FALSE PATH的設(shè)置

硬件設(shè)計(jì)中教你如何正確的約束時(shí)鐘

如何判斷路徑的timing exception約束

CDC跨時(shí)鐘域的基礎(chǔ)概念

CDC跨時(shí)鐘域的基礎(chǔ)概念介紹

跨時(shí)鐘域CDC之全面解析

STA學(xué)習(xí)記錄-時(shí)鐘定義

如何做一條合格的path?同一條path在物理設(shè)計(jì)不同階段的變化

如何追溯同一時(shí)鐘域內(nèi)partial false path的來(lái)源

如何追溯同一時(shí)鐘域內(nèi)partial false path的來(lái)源

評(píng)論