Q1

QFP的封裝,MCU的RTC功能,外部32.768K晶振不起振,把MCU重新焊接一下就好了,晶振電路沒有動。可以排除晶振外部電路的焊接問題和芯片boot strapping問題。這個可能是什么原因?需要做什么分析?嘗試改過MCU內部晶振電路驅動能力,還有晶振的負載電容,和反饋電阻,但都沒有效果。懷疑溫度導致MCU的這兩個晶振管腳電氣特性發生變化,變好了。客戶端懷疑芯片封裝問題,高溫改變了管腳封裝的內部晶圓阻抗特性等。

A

可能的原因:

1、確認晶振選型是否合適,例如看匹配電容參數。

2、確認不同溫度條件下晶振是否能起振,如果室溫就不能起振、低溫條件下也要驗證一下。天干物燥、重新焊接等等環境變化,都會導致該管腳輕微的量級變化,從而導致芯片出現完全不同的狀態。

3、Boot Strapping配置問題。舉個例子,STM32 MCU 的Boot0管腳如果不接GND,而是懸空,那么就會導致有時候能啟動,有時候不能啟動。對于芯片的啟動配置管腳,如果懸空,芯片內部也沒有上下拉,那么這個管腳就會出于未知狀態。當這個管腳積累的電荷比較少,就會以低電平方式啟動芯片,當電荷積累的較多,就會以高電平配置方式啟動芯片。

4、焊接問題,可以用3D Xray看看是否有焊接問題。

分析:要做FA分析,看看Bonding線和 First Pad, Second Pad是否有連接問題。測一下起振電流的大小,一般起振電流都不大,如果焊接或者封裝不良導致寄生的電路會影響起振。

Q2

植球產品做完PCT168試驗后測試Fail,SEM看到有PI crack。錫球UBM看著很奇怪,打了EDS成分里有錫,PI 表面沾污里也有。PCT試驗會導致這種情況嗎?

A

PCT實驗條件中121℃不會導致PI/ubm成分中含錫,但是植球后需要reflow,可能導致EDS分析含錫。

Q3

有個FC產品要做solder bump,bump pitch 150;封裝廠建議我們bump diameter最大90,我們想bump diameter盡可能高,方便EMC填充,但是兩家bumping廠給出的最大bump height 差異太大,不知道那個正確?

A

工廠都應該給出schematic,標示具體各個部位的尺寸。或者選Filler size比較小的CPD填充,比改Bumping會更省力點。

Q4

是否碰到過BHAST后Vmin漂移的情況,同晶圓還是封裝工藝相關性強些?Vmin是電源有拉偏,呈增加的趨勢。有些像HTOL之后的。

A

建議看看該電源壓力測試前后漏電情況有沒有變化,并嘗試相應FA分析。

Q5

封裝用的是fanout封裝,但是我們發現經過溫度循環后部分芯片測試失效,有IQ失效也有短路,結果發現裸die背面有不同程度裂紋,有橫向也有豎向,方向都不一致,并且有個缺口大一點,一個點,幫忙分析下什么原因造成的?

A

建議在TC前后進行40x鏡檢,確保疑似裂紋不是測試時導入。

Q6

QFN的產品,做完預處理+BHAST后再激光開蓋,做拉力和推力,這個數據情況和試驗前做會有差異嗎?現在的情況是發現有2個球脫落了,如果對其他沒掉的球做拉力和推力,怎么去判斷這個結果?

A

通常,拉力和推力都較之前的Qual數據低了,但是也有可能是開蓋過程中有損傷了。樣品出現拉力球脫或者推力很小,那就是不正常的。可以后續分析下球脫怎么失效的,和同顆芯片未失效的做下對比。

Q7

這種圖片,是SMT之后取下來的圖片。板廠說電鍍有問題,封裝廠說板廠SMT有問題

大家覺得可能的問題是什么?很困惑。這些都是一顆樣品上的不同管腳的圖片。

A

可以檢查下有沒有高溫翹曲,或者看看出現non-wetting的位置有沒有共性。

Q8

整機的環境測試。芯片規格書工作溫度-40到125℃,那點溫計點殼溫應該保證殼溫在多少度合適呢?

A

這個芯片工作的環境溫度就是125度,只要環境溫度不超過125度都是合規的。

Q9

copper pillar,側爬錫嚴重,造成void,擔心有橋接;各位有改善側爬方法嗎?(不加Ni)。Solder Mask厚度為15~20um。

A

既然不想它往上爬,SR window科實嘗試開大一些,還有,Warpage可能對此也有影響,在Reflow工藝上面想想辦法。或者,做下這個仿真一下就知道了,設計不同,影響因素相對多了點。

Q10

芯片內部水汽入侵的話,芯片表面形貌會體現出來嗎?有沒有典型圖能學習一下?

A

芯片有水汽入侵的判斷方法:過三遍回流焊,有水汽,SAT會有紅區,TSCAN,芯片下面有紅區,甚至過三遍回流焊,后去做推拉力實驗。或者開蓋,看看表面是否有侵蝕痕跡,下圖是decap后的圖片。

Q11

封裝中的打廢治具是必須的嗎?以前都沒有聽說過這個東西。封裝過程中標記reject的,比如內部打線不良的,塑封后就看不到了,需要標記出來,切割后就打廢掉不進入包裝。

A

根據工廠的現狀,每家要求不一樣。比如系統比較好的有mapping+Jig saw就可以直接踢出不良。系統不完善的,就只能手工記錄, Tape saw就更不易操作了。

Q12

合封的費用比普通封裝的費用大概會貴多少?比如都是wire bond BGA256,一個是單顆die,一個是兩顆die(兩顆die之間只有不到10個引腳互聯),合封的價格大概會貴多大比例?

A

這個不好說,UPH什么的都要考慮進去。UPH=unit per hour,每小時產量。

Q13

封裝可能會影響MCU系統時鐘的頻率嗎?我們有款產品在兩家封裝廠封裝出來的產品有一家封裝片測出來的系統時鐘跟CP校準后的相比偏差很大,另外一家沒有問題,有沒有遇到過類似問題?

A

RC震蕩電路的R/C值會引起頻率變化。不知道你是那種頻率發生器。可以找設計來解釋。

編輯:jq

-

mcu

+關注

關注

146文章

17003瀏覽量

350335 -

封裝

+關注

關注

126文章

7789瀏覽量

142734 -

RC

+關注

關注

0文章

225瀏覽量

48761

原文標題:季豐電子IC運營工程技術知乎 – 21W35

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

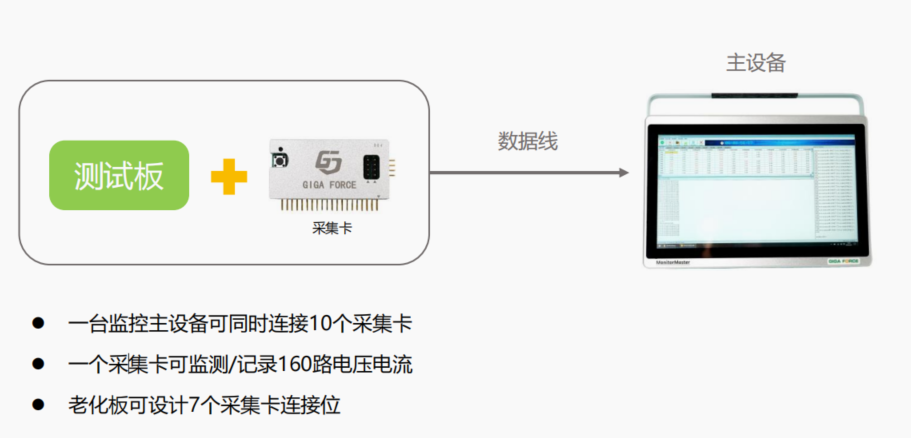

季豐電子MonitorMaster系統在BHAST實驗中的應用

衢州季豐獲得CMA擴項資質認定證書

2024季豐電子技術交流研討會深圳站圓滿結束

衢州季豐獲得CNAS擴項認證

杭州季豐成功獲得CNAS認可證書

季豐電子與數字電源設計公司華源智信攜手建立聯合實驗室

季豐電子成功通過IECQ換證審核

珠海中京電子成功獲得“廣東省電子電路工程技術研究中心”認定

季豐電子IC運營工程技術問答

季豐電子IC運營工程技術問答

評論