原理

關(guān)于Multiboot的原理參考《Xilinx 7系列FPGA Multiboot介紹-遠(yuǎn)程更新》,基本原理都在此文寫(xiě)的很清楚,本文主要從實(shí)例出發(fā)演示Multiboot。

補(bǔ)充

FPGA SPI閃存配置接口

7系列FPGA和具有x1數(shù)據(jù)寬度的SPI閃存之間的基本連接。讀取和地址指令通過(guò)主輸出-從輸入(MOSI)引腳從FPGA發(fā)送到SPI閃存。數(shù)據(jù)通過(guò)主輸入從輸出(MISO)引腳從SPI閃存返回。SCK是時(shí)鐘引腳,SS是低電平從選擇引腳。

參考:UG470

Vivado工具流程(Multiboot大致流程)

為Multiboot程序準(zhǔn)備bit流

本節(jié)概述了為多引導(dǎo)應(yīng)用程序創(chuàng)建和更新比特流所需的比特流屬性。對(duì)于未指定的位流選項(xiàng),請(qǐng)使用默認(rèn)設(shè)置。

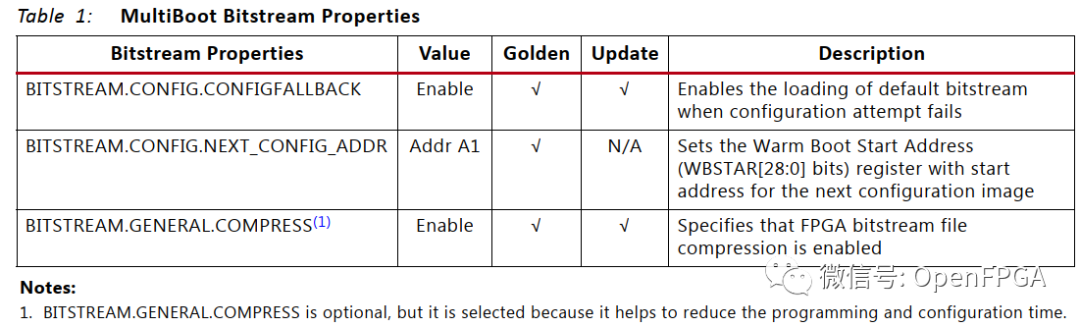

表1概述了用于生成和更新具有每個(gè)屬性描述的位流的基本多引導(dǎo)位流屬性。有關(guān)這些屬性的詳細(xì)說(shuō)明,請(qǐng)參閱Vivado Design Suite用戶指南:編程和調(diào)試(UG908)。

具體含義如下:

啟用在配置嘗試失敗時(shí)加載默認(rèn)位流

使用下一個(gè)配置映像的啟動(dòng)地址設(shè)置熱啟動(dòng)啟動(dòng)啟動(dòng)地址(WBSTAR[28:0]位)寄存器

指定啟用FPGA位流文件壓縮

在Vivado中打開(kāi)黃金設(shè)計(jì)實(shí)現(xiàn)(Golden)的約束文件(.xdc)。將以下內(nèi)容復(fù)制粘貼到約束文件中,然后保存對(duì).xdc文件所做的更改:

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

set_propertyBITSTREAM.CONFIG.NEXT_CONFIG_ADDR0x0400000[current_design]

set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design]

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

上述不理解沒(méi)關(guān)系,后續(xù)實(shí)例會(huì)有使用教程。

接下來(lái),可以在更新設(shè)計(jì)(將要更新的文件)中打開(kāi)約束文件(.xdc),并將以下比特流屬性添加到約束文件中,然后保存:

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design]

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

注:默認(rèn)情況下,SPI_BUS為x1,如果未使用默認(rèn)x1模式,請(qǐng)確保設(shè)置此屬性。

生成SPI閃存編程文件

具體查看《【Vivado那些事】Vivado兩種生成、固化燒錄文件》。

使用write_cfgmem Tcl命令創(chuàng)建閃存編程文件(.mcs)。

write_cfgmem獲取FPGA位流(.bit)并生成可用于編程SPI閃存的閃存文件(.mcs)。

例如,生成包含兩個(gè)FPGA位流(.bit文件)的閃存編程文件(.mcs)文件,如下所示:

write_cfgmem-formatmcs-interfaceSPIX1-size16-loadbit"up0/golden.bitup

0x0400000/update.bit" /filename.mcs

注:地址值0x0400000是參考設(shè)計(jì)中使用的示例。應(yīng)使用黃金圖像(更新圖像的起始地址)中設(shè)置的Addr A1值(見(jiàn)表1)。

請(qǐng)參閱Vivado Design Suite用戶指南:編程和調(diào)試(UG908或使用Vivado中的-help命令,以了解每個(gè)write_cfgmem命令選項(xiàng)的詳細(xì)說(shuō)明:

write_cfgmem -help

硬件驗(yàn)證

硬件驗(yàn)證其實(shí)很簡(jiǎn)單,我們分別建立兩個(gè)工程,兩個(gè)工程都是流水燈程序,分別從左到右和從右到左流水燈,這樣可以很清楚知道FPGA運(yùn)行了哪個(gè)程序。接下來(lái)破壞golden程序,按照上述制作MCS文件后運(yùn)行,看下運(yùn)行哪個(gè)程序。

建立工程

詳細(xì)的Verilog文件如下:

golden工程

moduleTop_MultiBoot_Module_A(

inputCLK,

outputreg[3:0]LED_Out

);

////////////////////////////////////////////

wireRESET;

assignRESET=1'b1;

////////////////////////////////////////////

//

//首先定義一個(gè)時(shí)間計(jì)數(shù)寄存器counter,每當(dāng)達(dá)到預(yù)定的100ms時(shí),

//計(jì)數(shù)寄存器就清零,否則的話寄存器就加1??//然后計(jì)算計(jì)數(shù)器計(jì)數(shù)的最大值。時(shí)鐘頻率為12MHZ??//也就是周期為1/12M ??3ns,要計(jì)數(shù)的最大值為T(mén)100MS= 100ms/83ns-1 = 120_4818??//

reg[31:0]counter;

parameterT100MS=25'd920_4818;

always@(posedgeCLK)

if(counter==T100MS)

counter<=25'd0;

else

counter<=counter+1'b1;

////////////////////////////////////////////

always@(posedgeCLKornegedgeRESET)

if(!RESET)

LED_Out<=4'b0001;//初值,最低位led[0]燈亮

elseif(counter==T100MS)

begin

if(LED_Out==4'b0000)//當(dāng)溢出最高位時(shí)

LED_Out<=4'b0001;//回到復(fù)位時(shí)的狀態(tài)

else

LED_Out<=LED_Out<<1;?????//循環(huán)左移一位?

?end

endmodule?//?Run_LED

update工程

moduleTop_MultiBoot_Module_B(

inputCLK,

outputreg[3:0]LED_Out

);

////////////////////////////////////////////

wireRESET;

assignRESET=1'b1;

////////////////////////////////////////////

//

//首先定義一個(gè)時(shí)間計(jì)數(shù)寄存器counter,每當(dāng)達(dá)到預(yù)定的100ms時(shí),

//計(jì)數(shù)寄存器就清零,否則的話寄存器就加1??//然后計(jì)算計(jì)數(shù)器計(jì)數(shù)的最大值。時(shí)鐘頻率為12MHZ??//也就是周期為1/12M ??3ns,要計(jì)數(shù)的最大值為T(mén)100MS= 100ms/83ns-1 = 120_4818??//

reg[31:0]counter;

parameterT100MS=25'd920_4818;

always@(posedgeCLK)

if(counter==T100MS)

counter<=25'd0;

else

counter<=counter+1'b1;

////////////////////////////////////////////

always@(posedgeCLKornegedgeRESET)

if(!RESET)

LED_Out<=4'b0001;//初值,最低位led[0]燈亮

elseif(counter==T100MS)

begin

if(LED_Out==4'b0000)//當(dāng)溢出最高位時(shí)

LED_Out<=4'b0001;//回到復(fù)位時(shí)的狀態(tài)

else

LED_Out<=LED_Out<<1;?????//循環(huán)左移一位?

?end

endmodule?//?Run_LED

兩個(gè)工程基本一樣,流水的操作是在約束里實(shí)現(xiàn)的。

golden工程約束

#CLOCKS

#SYSCLK

set_propertyIOSTANDARDLVCMOS18[get_portsCLK]

set_propertyPACKAGE_PIND27[get_portsCLK]

#GPIOLEDs

#set_propertyPACKAGE_PINAB8[get_portsLED_REVXX[7]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[7]]

#set_propertyPACKAGE_PINAA8[get_portsLED_REVXX[6]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[6]]

#set_propertyPACKAGE_PINAC9[get_portsLED_REVXX[5]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[5]]

#set_propertyPACKAGE_PINAB9[get_portsLED_REVXX[4]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[4]]

#set_propertyPACKAGE_PINAE26[get_portsLED_Out[3]]

#set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[3]]

set_propertyPACKAGE_PINT21[get_portsLED_Out[2]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[2]]

set_propertyPACKAGE_PINT20[get_portsLED_Out[1]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[1]]

set_propertyPACKAGE_PINR24[get_portsLED_Out[0]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[0]]

#CFGBVSandSPImodeproperties

set_propertyCFGBVSVCCO[current_design]

set_propertyCONFIG_VOLTAGE2.5[current_design]

set_propertyCONFIG_MODESPIX1[current_design]

#Compressthebitstreamtofiton128MQSPIoftheK7

set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design]

#BITSTREAMPROPERTIESREQUIREDFORGOLDENIMAGE:

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

set_propertyBITSTREAM.CONFIG.NEXT_CONFIG_ADDR0x0400000[current_design]

#(IftheSPIflashisequaltoorgreaterthan256Mb,uncommenttheconstraintbelow):

#set_propertyBITSTREAM.CONFIG.SPI_32BIT_ADDRYES[current_design]

這里解釋一下,前面物理約束不重要,因?yàn)椤案F”,我的板子只有3顆LED,所以只進(jìn)行了三個(gè)物理約束。

CFGBVS and SPI mode properties及Compress the bitstream to fit on 128M QSPI of the K7、BITSTREAM PROPERTIES REQUIRED FOR GOLDEN IMAGE是重點(diǎn)約束的對(duì)象,具體解釋看下表一。

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

set_propertyBITSTREAM.CONFIG.NEXT_CONFIG_ADDR0x0400000[current_design]

這三個(gè)約束是和UPDATE工程有關(guān),一個(gè)是SPI的BUSWIDTH,一個(gè)是否開(kāi)啟CONFIGFALLBACK,最后一個(gè)是地址,這是非常重要的。

接下來(lái)是update工程的約束文件

#CLOCKS

#SYSCLK

set_propertyIOSTANDARDLVCMOS18[get_portsCLK]

set_propertyPACKAGE_PIND27[get_portsCLK]

#GPIOLEDs

#set_propertyPACKAGE_PINAB8[get_portsLED_REVXX[7]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[7]]

#set_propertyPACKAGE_PINAA8[get_portsLED_REVXX[6]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[6]]

#set_propertyPACKAGE_PINAC9[get_portsLED_REVXX[5]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[5]]

#set_propertyPACKAGE_PINAB9[get_portsLED_REVXX[4]]

#set_propertyIOSTANDARDLVCMOS15[get_portsLED_REVXX[4]]

#set_propertyPACKAGE_PINAE26[get_portsLED_Out[3]]

#set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[3]]

set_propertyPACKAGE_PINR24[get_portsLED_Out[2]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[2]]

set_propertyPACKAGE_PINT20[get_portsLED_Out[1]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[1]]

set_propertyPACKAGE_PINT21[get_portsLED_Out[0]]

set_propertyIOSTANDARDLVCMOS33[get_portsLED_Out[0]]

#CFGBVSandSPImodeproperties

set_propertyCFGBVSVCCO[current_design]

set_propertyCONFIG_VOLTAGE2.5[current_design]

set_propertyCONFIG_MODESPIX1[current_design]

#Compressthebitstream

set_propertyBITSTREAM.GENERAL.COMPRESSTRUE[current_design]

#BITSTREAMPROPERTIESREQUIREDFORGOLDENIMAGE:

set_propertyBITSTREAM.CONFIG.SPI_BUSWIDTH1[current_design]

set_propertyBITSTREAM.CONFIG.CONFIGFALLBACKENABLE[current_design]

#(IftheSPIflashisequaltoorgreaterthan256Mb,uncommenttheconstraintbelow):

#set_propertyBITSTREAM.CONFIG.SPI_32BIT_ADDRYES[current_design]

物理約束同樣不重要,重要的還是下面的和multiboot相關(guān)的約束,具體解釋和上面一樣。

生成Bit流并運(yùn)行

上述兩個(gè)工程分別生成Bit流并運(yùn)行,查看兩個(gè)流水燈是否是兩個(gè)不同方向的。

合成MCS文件并運(yùn)行

將兩個(gè)BIT流文件合成一個(gè)MCS文件,命令如下:

write_cfgmem-formatmcs-interfaceSPIX1-size16-loadbit"up0/golden.bitup

0x0400000/update.bit" /filename.mcs

兩個(gè)bit流文件位置;

filename: mcs文件名稱。

將上訴mcs文件下載到FPGA開(kāi)發(fā)板上,可以看見(jiàn)update工程文件運(yùn)行。

破壞Golden文件

回退到Golden可以通過(guò)不同的方式觸發(fā)。主要有以下幾種方式:

- ID Code錯(cuò)誤

- CRC錯(cuò)誤

- Watchdog超時(shí)

- BPI地址越界

有關(guān)更多信息,請(qǐng)參閱UG470中的重新配置和多引導(dǎo)章節(jié)。

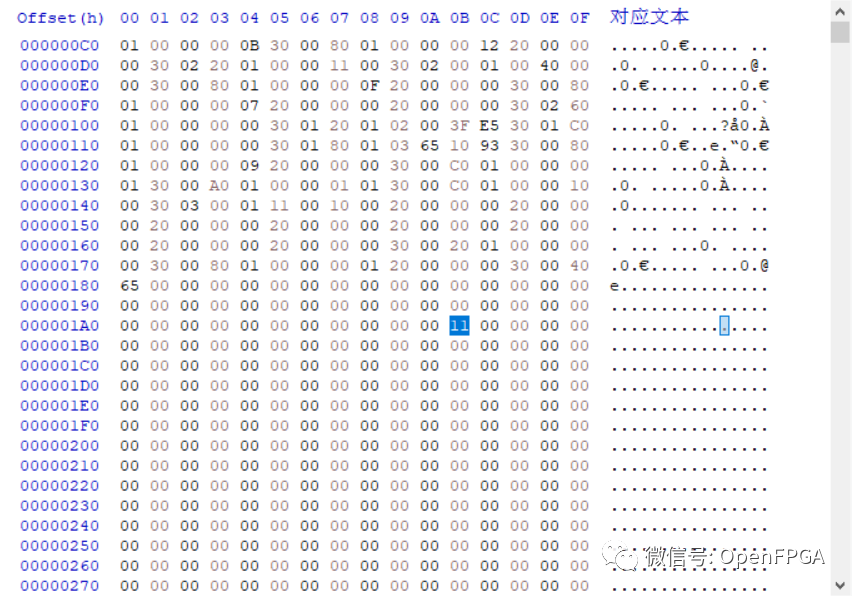

本應(yīng)用說(shuō)明演示了由CRC錯(cuò)誤觸發(fā)的回退。可以手動(dòng)損壞更新位流以導(dǎo)致CRC錯(cuò)誤。在RESET CRC命令和CRC命令之間有許多可以翻轉(zhuǎn)位的位置。下圖顯示了一個(gè)示例。

- 1.使用十六進(jìn)制編輯器(HxD Hex Editor)中打開(kāi)更新(update)比特流(.bit),在比特流中間翻轉(zhuǎn)一些數(shù)據(jù)字節(jié),例如從00到11,如圖所示。

為了保證破壞徹底,可以多更改幾處。

- 保存損壞的更新位流,并使用此損壞的位流生成新的閃存編程文件(.mcs)。

write_cfgmem-formatmcs-interfaceSPIX1-size16-loadbit"up0/golden.bitup

0x0400000/update.bit" /filename.mcs

- 3.重新下載文件

觀察是Golden還是update文件運(yùn)行,同理可以將上訴命令修改,將golden和update更換一下mcs文件位置,對(duì)比測(cè)試,上訴兩個(gè)情況本人都有親自測(cè)試過(guò),都是golden文件運(yùn)行,證明multiboot已經(jīng)生效。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21671瀏覽量

601914 -

led

+關(guān)注

關(guān)注

242文章

23141瀏覽量

658540 -

閃存編程

+關(guān)注

關(guān)注

0文章

9瀏覽量

6654

原文標(biāo)題:Xilinx Multiboot實(shí)例演示

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何申請(qǐng)xilinx IP核的license

【AG32開(kāi)發(fā)板體驗(yàn)連載】AG32VF407啟動(dòng)與探究

深入探究石英可編程 DXO/VCXO 振蕩器 SWPQ201 系列(10MHz 至 1500 MHz)

Python在AI中的應(yīng)用實(shí)例

深入探究 MEMS LVCMOS 振蕩器 SiT1602 系列 52 種標(biāo)準(zhǔn)頻率

基于PyTorch的卷積核實(shí)例應(yīng)用

神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu)類型和應(yīng)用實(shí)例

步進(jìn)電機(jī)的控制原理與應(yīng)用實(shí)例

飛天技術(shù)沙龍回顧:業(yè)務(wù)創(chuàng)新新選擇,倚天Arm架構(gòu)深入探討

高效節(jié)能的DC電源模塊技術(shù)探究

EMC技術(shù):未來(lái)趨勢(shì)下的應(yīng)用與發(fā)展探究?

Xilinx fpga芯片系列有哪些

AMD Xilinx 7系列FPGA的Multiboot多bit配置

簡(jiǎn)述Xilinx 7系列FPGA芯片相關(guān)知識(shí)

深入探究Xilinx Multiboot實(shí)例

深入探究Xilinx Multiboot實(shí)例

評(píng)論