當(dāng)今的設(shè)計(jì)工程師受到面積、功率和成本的約束,不能采用GHz級(jí)的計(jì)算機(jī)實(shí)現(xiàn)嵌入式設(shè)計(jì)。在嵌入式系統(tǒng)中,通常是由相對(duì)數(shù)量較少的算法決定最大的運(yùn)算需求。使用設(shè)計(jì)自動(dòng)化工具可以將這些算法快速轉(zhuǎn)換到硬件協(xié)處理器中。然后,協(xié)處理器可以有效地連接到處理器,產(chǎn)生“GHz”級(jí)的性能。

本文主要研究了代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法。我們還分析了通過一個(gè)涉及到基于輔助處理器單元(APU)的實(shí)際圖像顯示案例的基準(zhǔn)數(shù)據(jù)均衡決策的過程。該設(shè)計(jì)使用了在一個(gè)平臺(tái)FPGA中實(shí)現(xiàn)的一個(gè)嵌入式PowerPC。

協(xié)處理器的意義

協(xié)處理器是一個(gè)處理單元,該處理單元與一個(gè)主處理單元一起使用來(lái)承擔(dān)通常由主處理單元執(zhí)行的運(yùn)算。通常,協(xié)處理器功能在硬件中實(shí)現(xiàn)以替代幾種軟件指令。通過減少多種代碼指令為單一指令,以及在硬件中直接實(shí)現(xiàn)指令的方式,從而實(shí)現(xiàn)代碼加速。

最常用的協(xié)處理器是浮點(diǎn)單元(FPU),這是與CPU緊密結(jié)合的唯一普通協(xié)處理器。沒有通用的協(xié)處理器庫(kù),即使是存在這樣的庫(kù),將依然難以簡(jiǎn)單地將協(xié)處理器與一個(gè)CPU(例如Pentium 4)連接。Xilinx Virtex-4 FX FPGA擁有一個(gè)或兩個(gè)PowerPC,每個(gè)都有一個(gè)APU接口。通過在FPGA中嵌入一個(gè)處理器,現(xiàn)在就有機(jī)會(huì)在單芯片上實(shí)現(xiàn)完整的處理系統(tǒng)。

帶APU接口的PowerPC使得在FPGA中得以實(shí)現(xiàn)一個(gè)緊密結(jié)合的協(xié)處理器。因?yàn)轭l率的需求以及管腳數(shù)量的限制,采用外部協(xié)處理器不大可行。因此可以創(chuàng)建一個(gè)直接連接到PowerPC的專用應(yīng)用協(xié)處理器,大大地提高了軟件速度。因?yàn)镕PGA是可編程的,你可以快速地開發(fā)和測(cè)試連接到CPU的協(xié)處理器解決方案。

協(xié)處理器連接模型

協(xié)處理器有三種基本的形式:與CPU總線連接的、與I/O連接的和指令流水線連接(Instruction Pipeline Connection)。此外,還存在一些這些形式的混合形式。

1. CPU總線連接

處理器總線連接加速器需要CPU在總線上移動(dòng)數(shù)據(jù)以及發(fā)送命令。通常,單個(gè)數(shù)據(jù)處理就需要很多的處理器時(shí)鐘周期。因?yàn)榭偩€仲裁以及總線驅(qū)動(dòng)的時(shí)鐘是處理器時(shí)鐘的分頻,所以會(huì)降低數(shù)據(jù)處理速度。一個(gè)與總線連接的加速器可以包含一個(gè)存儲(chǔ)器存取(DMA)引擎。在增加額外的邏輯情況下,DMA引擎允許協(xié)處理器工作在位于連接到總線的存儲(chǔ)器上的數(shù)據(jù)塊,獨(dú)立于CPU。

2. I/O連接

與I/O連接的加速器直接連接到一個(gè)專用的I/O端口。通常通過GET或PUT函數(shù)提供數(shù)據(jù)和控制。因?yàn)槿鄙倭酥俨谩⒖刂茝?fù)雜度降低以及連接器件較少,因此這些接口的驅(qū)動(dòng)時(shí)鐘通常比處理器總線更快。這種接口的一個(gè)較好的例子如Xilinx Fast Simplex Link(FSL)。FSL是一種簡(jiǎn)單的FIFO接口,可以連接到Xilinx MicroBlaze軟核處理器或Virtex-4 FX PowerPC。與處理器總線接口中的數(shù)據(jù)移動(dòng)相比,通過FSL移動(dòng)的數(shù)據(jù)具有較低的延時(shí)和更高的數(shù)據(jù)速率。

3. 指令流水線連接

指令流水線連接加速器直接連接到CPU的計(jì)算內(nèi)核。通過與指令流水線連接,CPU不能識(shí)別的指令可以由協(xié)處理器執(zhí)行。操作數(shù)、結(jié)果以及狀態(tài)直接從數(shù)據(jù)執(zhí)行流水線向外傳遞,或接收。單個(gè)運(yùn)算可以實(shí)現(xiàn)兩個(gè)操作數(shù)的處理,同時(shí)返回一個(gè)結(jié)果和狀態(tài)。

作為一個(gè)直接連接的接口,連接道指令流水線的加速器可以用比處理器總線更快的時(shí)鐘驅(qū)動(dòng)。Xilinx通過APU接口實(shí)現(xiàn)這種協(xié)處理器連接模型,對(duì)于典型的雙操作數(shù)指令,在數(shù)據(jù)控制和數(shù)據(jù)傳輸上可以縮減10倍的時(shí)鐘周期。APU控制器還連接到數(shù)據(jù)緩存控制器,通過它可以執(zhí)行數(shù)據(jù)加載/存儲(chǔ)操作。因此,APU接口能在每秒內(nèi)移動(dòng)數(shù)百兆字節(jié),接近DMA速度。

I/O連接加速器或指令流水線連接加速器可以與總線連接加速器結(jié)合起來(lái)。在增加額外的邏輯條件下,可以創(chuàng)建一個(gè)加速器,這個(gè)加速器運(yùn)行在一個(gè)位于總線連接存儲(chǔ)器上的數(shù)據(jù)塊上,通過一個(gè)快速、低延時(shí)的接口接收命令并返回狀態(tài)。

在本文中介紹的C-HDL工具組可以實(shí)現(xiàn)總線連接和I/O連接加速器,它還能實(shí)現(xiàn)連接到PowerPC的APU接口的加速器。盡管APU連接是基于指令流水線的,C-HDL工具組實(shí)現(xiàn)了一種I/O流水線接口,該接口具有I/O連接加速器的典型性能。

FPGA/PowerPC/APU接口

FPGA允許硬件設(shè)計(jì)工程師利用單芯片上的處理器、解碼邏輯、外設(shè)和協(xié)處理器實(shí)現(xiàn)一個(gè)完整的計(jì)算系統(tǒng)。FPGA可以包含數(shù)千到數(shù)十萬(wàn)的邏輯單元,可以從這些邏輯單元實(shí)現(xiàn)一個(gè)處理器,如Xilinx PicoBlaze或MicroBlaze處理器,或者可以是一個(gè)或者更多的硬邏輯單元(如Virtex-4 FX PowerPC)。大量的邏輯單元使你可以實(shí)現(xiàn)數(shù)據(jù)處理單元,這些單元與處理器系統(tǒng)一起工作,由處理器對(duì)其進(jìn)行控制或監(jiān)控。

FPGA作為一種可重復(fù)編程的單元,允許你在設(shè)計(jì)過程中進(jìn)行編程并對(duì)其進(jìn)行測(cè)試。如果你發(fā)現(xiàn)了一個(gè)設(shè)計(jì)缺陷,你可以立即對(duì)其進(jìn)行重新編程設(shè)計(jì)。FPGA還允許你實(shí)現(xiàn)硬件運(yùn)算功能,而這在以前的實(shí)現(xiàn)成本是很高的。CPU流水線與FPGA邏輯之間緊密結(jié)合,這樣就可以創(chuàng)建高性能軟件加速器。

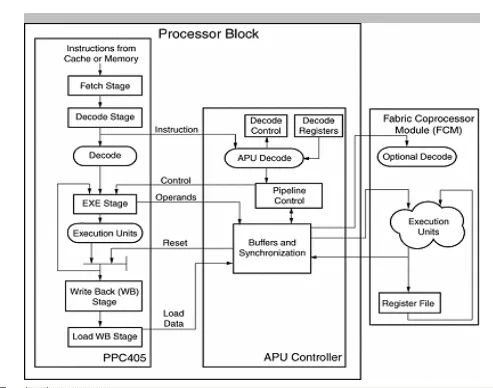

圖1的模塊框圖顯示了PowerPC、集成的APU控制器以及一個(gè)與之相連的協(xié)處理器。來(lái)自高速緩存或存儲(chǔ)器中的指令可以立即出現(xiàn)在CPU解碼器和APU控制器上,如果CPU能識(shí)別指令,則運(yùn)行這些指令。

否則,APU控制器或用戶創(chuàng)建的協(xié)處理器可以對(duì)指令做出應(yīng)答并執(zhí)行指令。一個(gè)或者兩個(gè)操作數(shù)被傳遞到協(xié)處理器,并返回一個(gè)結(jié)果或狀態(tài)。APU接口還支持用一個(gè)指令發(fā)送一個(gè)數(shù)據(jù)單元。數(shù)據(jù)單元的大小范圍從一個(gè)字節(jié)到4個(gè)32位的字。

圖1:PowerPC、集成的APU控制器和協(xié)處理器

通過一個(gè)結(jié)構(gòu)協(xié)處理器總線(FCB),可以將一個(gè)或多個(gè)協(xié)處理器連接到APU接口。連接到總線的協(xié)處理器范圍包括現(xiàn)存的內(nèi)核(例如FPU)到用戶創(chuàng)建的協(xié)處理器。一個(gè)協(xié)處理器可以連接到FCB用于控制和狀態(tài)運(yùn)算,并連接到一個(gè)處理器總線,實(shí)現(xiàn)直接存儲(chǔ)器數(shù)據(jù)塊訪問以及DMA數(shù)據(jù)傳遞。一種簡(jiǎn)化的連接方案,例如FSL,也可以在FCB和協(xié)處理器之間使用,在犧牲一定性能的條件下實(shí)現(xiàn)FIFO數(shù)據(jù)和控制通信。

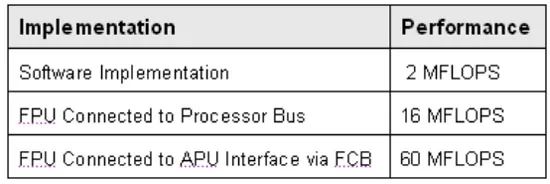

為展示指令流水線連接加速器的性能優(yōu)勢(shì),我們采用一個(gè)處理器總線連接FPU首先實(shí)現(xiàn)了一個(gè)設(shè)計(jì),然后采用APU/FCB連接的FPU實(shí)現(xiàn)設(shè)計(jì)。表1總結(jié)了兩種實(shí)現(xiàn)方式下有限脈沖響應(yīng)(FIR)濾波器的性能。如表1中所反映的一樣,連接到一個(gè)指令流水線的FPU使軟件浮點(diǎn)運(yùn)算速度增加30倍,而APU接口相比于總線連接FPU來(lái)說改善了近4倍。

表1:未加速與加速的浮點(diǎn)性能

C代碼轉(zhuǎn)換到HDL

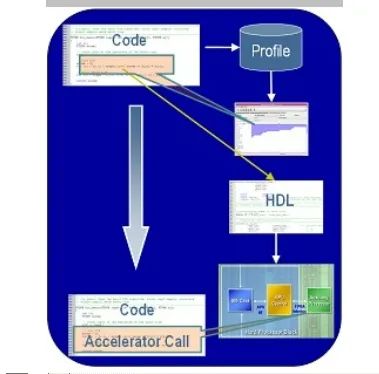

采用C到HDL的轉(zhuǎn)換工具將C代碼轉(zhuǎn)換到HDL加速器是一種創(chuàng)建硬件協(xié)處理器的高效方法。圖2所示以及下面詳述的步驟總結(jié)了C到HDL轉(zhuǎn)換的過程:

圖2:C-HDL設(shè)計(jì)流程

使用標(biāo)準(zhǔn)C工具實(shí)現(xiàn)應(yīng)用程序或算法。開發(fā)一種軟件測(cè)試向量(test bench)用于基線性能和正確性(主機(jī)或臺(tái)式電腦仿真)測(cè)試。使用一種編譯器(例如gprof)來(lái)開始確定關(guān)鍵的函數(shù)。

確定是否浮點(diǎn)到定點(diǎn)轉(zhuǎn)換適當(dāng)。使用庫(kù)或宏來(lái)輔助這種轉(zhuǎn)換,使用一個(gè)基線測(cè)試向量來(lái)分析性能和準(zhǔn)確性。使用編譯器來(lái)重新評(píng)估關(guān)鍵函數(shù)。

使用C到HDL轉(zhuǎn)換工具(如Impulse C),在每個(gè)關(guān)鍵功能上重復(fù),以實(shí)現(xiàn):將算法分割成并行的進(jìn)程;創(chuàng)建硬件/軟件進(jìn)程接口(流、共享存儲(chǔ)器、信號(hào));對(duì)關(guān)鍵的代碼段(例如內(nèi)部代碼循環(huán))進(jìn)行自動(dòng)優(yōu)化和并行化;使用桌面電腦仿真、周期準(zhǔn)確的C仿真以及實(shí)際的在系統(tǒng)測(cè)試對(duì)得到的并行算法進(jìn)行測(cè)試和驗(yàn)證。

使用C到HDL轉(zhuǎn)換工具將關(guān)鍵的代碼段轉(zhuǎn)換到HDL協(xié)處理器。

將協(xié)處理器連接到APU接口用于最終的測(cè)試。

Impulse:C到HDL轉(zhuǎn)換工具

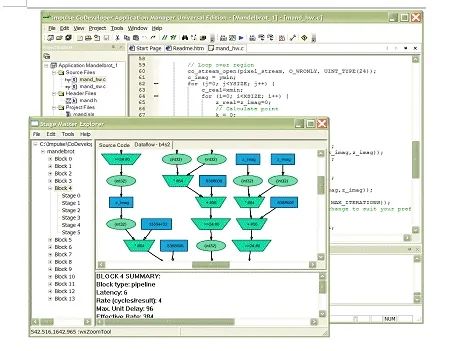

如圖3所示的Impulse C通過結(jié)合使用C兼容庫(kù)函數(shù)與Impulse CoDeveloper C代碼到硬件的編譯器,使嵌入式系統(tǒng)設(shè)計(jì)工程師能創(chuàng)建高度并行的、FPGA加速的應(yīng)用。Impulse C通過使用定義完好的數(shù)據(jù)通信、消息傳遞和同步處理機(jī)制,簡(jiǎn)化了硬件/軟件混合應(yīng)用設(shè)計(jì)。Impulse C提供了C代碼(例如循環(huán)流水線處理、展開和運(yùn)算符調(diào)度)的自動(dòng)優(yōu)化以及交互式工具,允許你對(duì)每個(gè)周期的硬件行為進(jìn)行分析。

圖3. Impulse C

Impulse C設(shè)計(jì)用于面向數(shù)據(jù)流的應(yīng)用,但是它也具有足夠的靈活性來(lái)支持其他的編程模型,包括使用共享存儲(chǔ)器。這一點(diǎn)很重要,因?yàn)榛贔PGA不同的應(yīng)用具有不同的性能和數(shù)據(jù)要求。在一些應(yīng)用中,通過塊存儲(chǔ)器讀和寫在嵌入式處理器和FPGA之間轉(zhuǎn)移數(shù)據(jù)是有意義的;在其它的情況下,流傳數(shù)通信信道可能提供更高的性能。可以快速建模、編譯和評(píng)估可選的算法的能力對(duì)于實(shí)現(xiàn)某個(gè)應(yīng)用最佳的結(jié)果來(lái)說,非常重要。

到目前為止,Impulse C庫(kù)包含以新數(shù)據(jù)類型和預(yù)定義的函數(shù)調(diào)用形式的最少C語(yǔ)言擴(kuò)展。使用Impulse C函數(shù)調(diào)用,你可以定義多個(gè)并行程序段(調(diào)用進(jìn)程),并使用流、信號(hào)和其他機(jī)制描述它們的互連。Impulse C編譯器將這些C語(yǔ)言進(jìn)程轉(zhuǎn)換并優(yōu)化成:可以綜合到FPGA的較低級(jí)HDL,或可以通過廣泛存在的C交叉編譯器編譯到支持的微處理器上標(biāo)準(zhǔn)C(帶相關(guān)的庫(kù)調(diào)用)。

完整的CoDeveloper開發(fā)環(huán)境包括與標(biāo)準(zhǔn)C編譯器和調(diào)試器(包括微軟公司的Visual Studio和GCC/GDB)兼容的臺(tái)式電腦仿真庫(kù)。使用這些庫(kù),Impulse C程序設(shè)計(jì)工程師能編譯和執(zhí)行他們用于算法驗(yàn)證和調(diào)試目的的應(yīng)用程序。C程序設(shè)計(jì)工程師還能檢驗(yàn)并行進(jìn)程,分析數(shù)據(jù)移動(dòng),并利用CoDeveloper Application Monitor解決進(jìn)程到進(jìn)程的通信問題。

在編譯時(shí),Impulse C應(yīng)用的輸出是一組硬件和軟件源文件,用于輸入到FPGA綜合工具。這些文件包括:

用于描述編譯硬件進(jìn)程的自動(dòng)產(chǎn)生的HDL文件;

用于描述連接硬件進(jìn)程到系統(tǒng)總線所需的流、信號(hào)和存儲(chǔ)器組件的自動(dòng)產(chǎn)生的HDL文件;

自動(dòng)產(chǎn)生的軟件組件(包括運(yùn)行時(shí)間庫(kù))用于建立任何硬件/軟件流連接的軟件端;

附加文件,包括腳本文件,用于輸入產(chǎn)生的應(yīng)用程序到目標(biāo)FPGA布局布線環(huán)境。這種編譯進(jìn)程的結(jié)果是一個(gè)完整的應(yīng)用,包括需要的硬件/軟件接口,用于在基于FPGA的編程平臺(tái)上實(shí)現(xiàn)。

設(shè)計(jì)實(shí)例

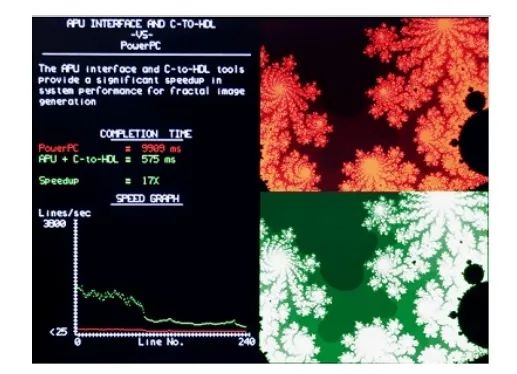

圖4所示的Mandelbrot圖是一種經(jīng)典的不規(guī)則幾何圖形,該圖形廣泛用在科學(xué)和工程學(xué)界用于仿真無(wú)序事件,例如天氣。不規(guī)則圖形也用于產(chǎn)生紋理和在視頻顯示應(yīng)用上成像。Mandelbrot圖像描述為自相似性。放大圖形的局部,可以獲得類似于整個(gè)圖形的另外一個(gè)圖形。

Mandelbrot圖形是硬件/軟件協(xié)同設(shè)計(jì)的理想選擇,因?yàn)樗哂袉蝹€(gè)運(yùn)算密集的函數(shù)。通過將關(guān)鍵的函數(shù)轉(zhuǎn)移到硬件實(shí)現(xiàn)將大大地增加整個(gè)系統(tǒng)的速度,使這個(gè)關(guān)鍵函數(shù)更快。Mandelbrot應(yīng)用還能清楚地區(qū)分硬件和軟件進(jìn)程,使用C-HDL工具很容易實(shí)現(xiàn)。

本文使用CoDeveloper工具組作為C-HDL工具組用于該設(shè)計(jì)實(shí)例,而且只修改了軟件Mandelbrot C程序以使其與C-HDL工具兼容。其中的改變包括:將軟件項(xiàng)目分割成不同的進(jìn)程(順序執(zhí)行的獨(dú)立單元);函數(shù)接口轉(zhuǎn)換(硬件到軟件)到流;增加編譯器指令來(lái)對(duì)產(chǎn)生的硬件進(jìn)行優(yōu)化。我們隨后使用CoDeveloper工具組來(lái)創(chuàng)建Pcore協(xié)處理器,將該協(xié)處理器輸入到Xilinx Platform Studio(XPS

)。利用XPS,我們將PC連接到PowerPC APU控制器接口,并測(cè)試系統(tǒng)。

Xilinx公司的應(yīng)用說明資料XAPP901中提供了該設(shè)計(jì)的全面描述和設(shè)計(jì)文件,并提供下載。同時(shí),用戶指南UG096提供一種實(shí)現(xiàn)設(shè)計(jì)實(shí)例的逐步設(shè)計(jì)指導(dǎo)。

我們對(duì)Mandelbrot圖像紋理問題、圖像濾波應(yīng)用和三倍DES加密的性能改善進(jìn)行了測(cè)量。

本文小結(jié)

受功率、尺寸和成本的約束,你可能需要做出一個(gè)并非理想的處理器選擇,通常所選擇處理器性能比期望的性能低。當(dāng)軟件代碼不能運(yùn)行足夠快時(shí),協(xié)處理器代碼加速器成為一種很有吸引力的解決方案。你可以在HDL中手動(dòng)設(shè)計(jì)加速器或使用C-HDL工具自動(dòng)將C代碼轉(zhuǎn)換成HDL。

使用Impulse C這樣的C-HDL工具能使加速器運(yùn)行更快且更簡(jiǎn)單。Virtex-4 FX FPGA具有兩個(gè)嵌入式PowerPC,能實(shí)現(xiàn)處理器指令流水線到軟件加速器之間緊密的連接。如上所述,關(guān)鍵的軟件程序增加速度10倍到30倍,使300MHz的PowerPC提供等于或高于高性能GHz級(jí)處理器的性能。上面的實(shí)例每個(gè)只需要幾天的時(shí)間來(lái)產(chǎn)生,顯示了采用C-HDL流程的快速設(shè)計(jì)、實(shí)現(xiàn)和測(cè)試

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601856 -

cpu

+關(guān)注

關(guān)注

68文章

10825瀏覽量

211150 -

數(shù)據(jù)

+關(guān)注

關(guān)注

8文章

6892瀏覽量

88828 -

fifo

+關(guān)注

關(guān)注

3文章

387瀏覽量

43553 -

APU

+關(guān)注

關(guān)注

0文章

141瀏覽量

23697

原文標(biāo)題:如何采用FPGA協(xié)處理器實(shí)現(xiàn)算法加速

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

使用TMS320C6416協(xié)處理器:Turbo協(xié)處理器(TCP)

使用TMS320C6416協(xié)處理器:Viterbi協(xié)處理器(VCP)

TMS320C6416協(xié)處理器和誤碼率

實(shí)現(xiàn)下一代具有電壓電平轉(zhuǎn)換功能的處理器、FPGA 和ASSP

淺談國(guó)產(chǎn)異構(gòu)雙核RISC-V+FPGA處理器AG32VF407的優(yōu)勢(shì)和應(yīng)用場(chǎng)景

充電也要算法??jī)?chǔ)能充電芯片中的算法處理器

請(qǐng)問ESP32s3 ULP RISC-V協(xié)處理器是否支持ADC的讀取?

基于FPGA的實(shí)時(shí)邊緣檢測(cè)系統(tǒng)設(shè)計(jì),Sobel圖像邊緣檢測(cè),FPGA圖像處理

Achronix FPGA增加對(duì)Bluespec提供的基于Linux的RISC-V軟處理器的支持,以實(shí)現(xiàn)可擴(kuò)展數(shù)據(jù)處理

fpga和risc-v處理器的區(qū)別

鴻蒙輕內(nèi)核源碼分析:MMU 協(xié)處理器

怎么用FPGA做算法 如何在FPGA上實(shí)現(xiàn)最大公約數(shù)算法

BlueNRG系列協(xié)處理器實(shí)戰(zhàn)經(jīng)驗(yàn)簡(jiǎn)介

采用FPGA協(xié)處理器實(shí)現(xiàn)算法加速教程

采用FPGA協(xié)處理器實(shí)現(xiàn)算法加速教程

評(píng)論