對于從事ASIC行業及FPGA行業的小伙伴來說,仿真是一件必不可少的事情。或許有人是驗證大拿,UVM高手,但相較于軟件豐富的驗證框架,對于各種各樣的場景單純的SV構建測試用例是否便捷值得推敲。

何為cocotb

cocotb is a coroutine based cosimulation library for writing VHDL and Verilog testbenches in Python.

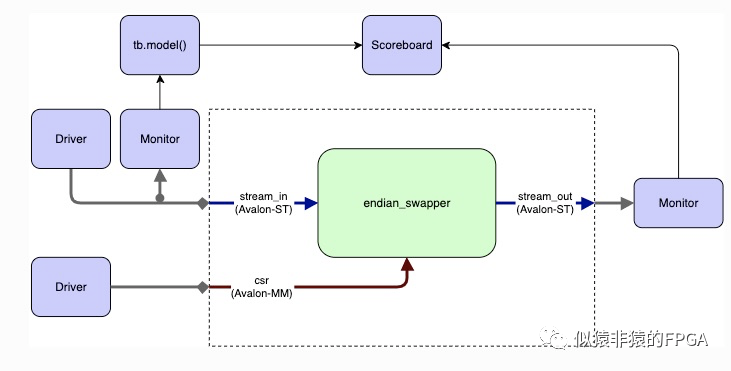

21世紀,python成了一門吃香的語言。cocotb是一套基于python的用于構建仿真及測試用例的lib庫,它的框架為:

可以看到,在cocotb的框架里,我們的待測試邏輯運行在仿真器中(VCS、Verilator等),而我們的測試框架及測試用例均以python的形式構建,雙方通過仿真器提供的各種標準接口進行通信。及設計代碼為Verilog/VHDL/Systemverilog,而測試代碼為Python。

存在即合理,為什么這么搞?因為Python寫起來簡單唄!在能夠正常實現對DUT的接口驅動的同時借助python豐富的lib庫能夠讓我們快速的構建測試用例及參考模型。而借助軟件現成的測試框架能夠極大加速驗證流程。想想單純的一個圖像處理的仿真用純Systemverilog的方式進行驗證在進行測試數據生成及最后結果對比要多少腳本……

cocotb安裝

按照cocotb手冊給出的安裝流程,在CentOS里安裝步驟為:在安裝過程中,有遇到“Python.h: No such file or directory”,解決辦法為:#Preparesudo yum install make gcc gcc-c++ libstdc++-devel python3 python3-devel python3-pip#install cocotbpip install cocotb##pip may belong to a different Python installation# to what you expect. Use pip -V to check. If this#prints “(python 2.7)”, use pip3 or python3 -m pip#inplaceofpipinthecommandshown.

安裝后可以查看到:1.可以先查看一下含python-devel的包yumsearchpython|greppython-devel2.64位安裝python-devel.x86_64,32位安裝python-devel.i686,我這里安裝:sudoyuminstallpython-devel.x86_643. 進入/usr/include/python2.7看一下現在有沒有Python.h,版本不同目錄名不同,我這里是2.7版本。其實也可以看到很多.h文件,python需要庫或頭文件都在這個地方。

對于沒有VCS等收費EDA license的小伙伴建議安裝Verilator:$cocotb-config -v1.4.1.dev0

sudo apt-get install git make autoconf g++ flex bison -y # First time prerequisitesgit clone http://git.veripool.org/git/verilator # Only first timeunsetenv VERILATOR_ROOT # For csh; ignore error if on bashunset VERILATOR_ROOT # For bashcdverilatorautoconf # Create ./configure script./configuremake -j$(nproc)sudomakeinstall

example

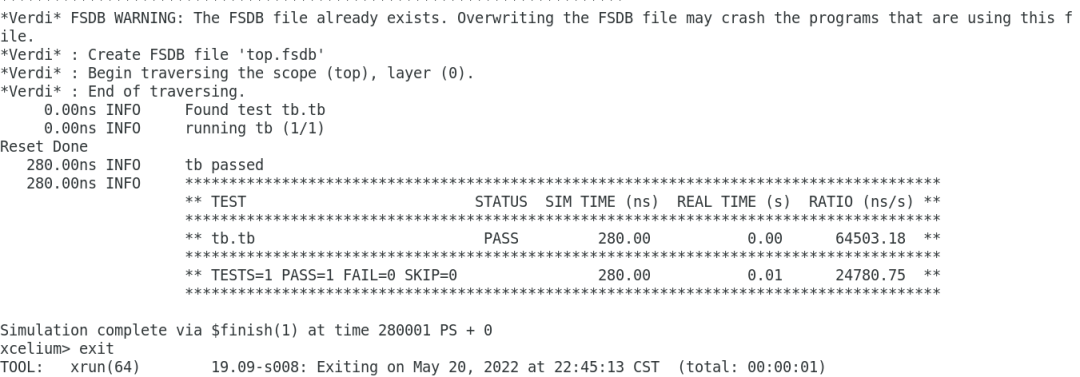

在cocotb中給出的example中,endian_swapper例子的測試框架為:

這里根據輸入的參數,factory會生成32個testcase用于測試,感覺還是蠻高效的。在仿真完成后,能夠自動匯總測試結果:factory = TestFactory(run_test)factory.add_option("data_in", [random_packet_sizes])factory.add_option("config_coroutine", [None, randomly_switch_config])factory.add_option("idle_inserter", [None, wave, intermittent_single_cycles, random_50_percent])factory.add_option("backpressure_inserter", [None, wave, intermittent_single_cycles, random_50_percent])factory.generate_tests()

寫在最后

之所以探索下cocotb,主要原因是雖然SpinalHDL測試框架和cocotb差不多,但目前SpinalHDL尚未集成對VCS仿真器的集成(而我又沒打算自己集成進去)。而在做FPGA設計時,若代碼里集成了Xilinx/Altera的IP,那么在SpinalHDL的框架里就沒辦法進行仿真了,而cocotb則是一個不錯的選擇(若可以選,我仍選SpinalHDL,設計仿真一條龍,當然現在也可以,對于Mem、FIFO等常用IP SpinalHDL還是有提供的,或者我們自己按需定制實現IP也可以的,SpinalHDL寫IP簡直不要太爽)。

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601897 -

軟件

+關注

關注

69文章

4781瀏覽量

87164

原文標題:cocotb初探

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

是德科技助力三星電子驗證FiRa 2.0安全測距測試用例

如何使用Python構建LSTM神經網絡模型

端到端測試用例怎么寫

是德科技獲得5G NR FR1 1024-QAM 解調測試用例的認證

鑒源實驗室·ISO 26262中測試用例的得出方法-等價類的生成和分析

基于python的用于構建仿真及測試用例的lib庫cocotb

基于python的用于構建仿真及測試用例的lib庫cocotb

評論