什么是阻抗

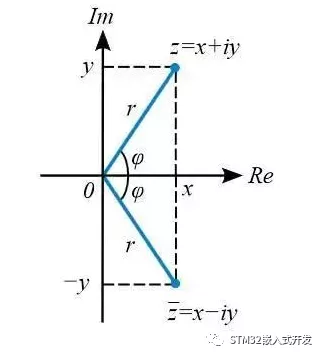

在電學中,常把對電路中電流所起的阻礙作用叫做阻抗。阻抗單位為歐姆,常用Z表示,是一個復數:

Z= R+i( ωL–1/(ωC))

具體說來阻抗可分為兩個部分,電阻(實部)和電抗(虛部)。

其中電抗又包括容抗和感抗,由電容引起的電流阻礙稱為容抗,由電感引起的電流阻礙稱為感抗。

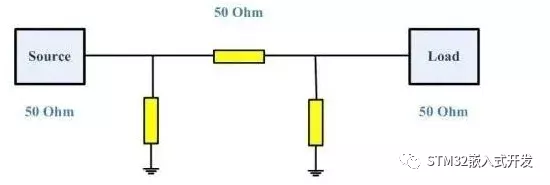

阻抗匹配的理想模型

射頻工程師大都遇到過匹配阻抗的問題,通俗的講,阻抗匹配的目的是確保能實現信號或能量從“信號源”到“負載”的有效傳送。

其最最理想模型當然是希望Source端的輸出阻抗為50歐姆,傳輸線的阻抗為50歐姆,Load端的輸入阻抗也是50歐姆,一路50歐姆下去,這是最理想的。

然而實際情況是:源端阻抗不會是50ohm,負載端阻抗也不會是50ohm,這個時候就需要若干個阻抗匹配電路。

而匹配電路就是由電感和電容所構成,這個時候我們就需要使用電容和電感來進行阻抗匹配電路調試,以達到RF性能最優。

阻抗匹配的方法

阻抗匹配的方法主要有兩個,一是改變阻抗力,二是調整傳輸線。

改變阻抗力就是通過電容、電感與負載的串并聯調整負載阻抗值,以達到源和負載阻抗匹配。

調整傳輸線是加長源和負載間的距離,配合電容和電感把阻抗力調整為零。

此時信號不會發生發射,能量都能被負載吸收。

高速PCB布線中,一般把數字信號的走線阻抗設計為50歐姆。一般規定同軸電纜基帶50歐姆,頻帶75歐姆,對絞線(差分)為85-100歐姆。

阻抗匹配應用舉例——振鈴現象

曾經做一個項目,在電信號測量時,遇到過振鈴這種問題。

由于任何傳輸線都不可避免地存在著引線電阻、引線電感和雜散電容,因此,一個標準的脈沖信號在經過較長的傳輸線后,極易產生上沖和振鈴現象。大量的實驗表明,引線電阻可使脈沖的平均振幅減小;而雜散電容和引線電感的存在,則是產生上沖和振鈴的根本原因。在脈沖前沿上升時間相同的條件下,引線電感越大,上沖及振鈴現象就越嚴重;雜散電容越大,則是波形的上升時間越長;而引線電阻的增加,將使脈沖振幅減小。

如果信號傳輸過程中感受到阻抗的變化,就會發生信號的反射。這個信號可能是驅動端發出的信號,也可能是遠端反射回來的反射信號。根據反射系數的公式,當信號感受到阻抗變小,就會發生負反射,反射的負電壓會使信號產生下沖。信號在驅動端和遠端負載之間多次反射,其結果就是信號振鈴。大多數芯片的輸出阻抗都很低,如果輸出阻抗小于PCB走線的特性阻抗,那么在沒有源端端接的情況下,必然產生信號振鈴。

在實際電路中,采用下列幾種方法來來減小和抑制上沖及振鈴。

(1)串聯電阻。利用具有較大電阻的傳輸線或是人為地串入適當的阻尼電阻,可以減小脈沖的振幅,從而達到減小上沖和振鈴程度的目的。但當傳入電阻的數值過大時,不僅脈沖幅度減小過多,而且使脈沖的前沿產生延遲。因此,串入的阻尼電阻值應適當,并且應選用無感電阻,電阻的連接位置應靠近接收端。

(2)減小引線電感。設法減小線路及傳輸線的引線電感是最基本的方法,總的原則是:

盡量縮短引線長度

加粗導線和印制銅箔的寬度

減小信號的傳輸距離

采用引線電感小的元器件,尤其是傳輸前沿很陡的脈沖信號時更應注意這些問題

(3)由于負載電路的等效電感和等效電容同樣可以影響發送端,使之脈沖波形產生上沖和振鈴,因此,應盡量減小負載電路的等效電感和電容。尤其是負載電路的接地線過長時,形成的地線電感和雜散電容相當可觀,其影響不容忽視。

(4)邏輯數字電路中的信號線可增加上拉電阻和交流終端負載,如圖6所示。上拉電阻(可取)的接入,可將信號的邏輯高電平上拉到5V。交流終端負載電路的接入不影響支流驅動能力,也不會增加信號線的負載,而高頻振鈴現象卻可得到有效的抑制。

上述振鈴除了與電路條件有關外,還與脈沖前沿的上升時間密切相關。即使電路條件相同,當脈沖前沿上升時間很短時,上沖的峰值將大大增加。一般對于前沿上升時間在1以下的脈沖,均考慮產生上沖及振鈴的可能。因此,在脈沖信號頻率的選擇問題上,應考慮在滿足系統速度要求的前提下,能選用較低頻率的信號絕不選用高頻信號;如無必要,也不應過分要求脈沖的前沿非常陡峭。這對從根本上消除上沖和振鈴視聽有利的。

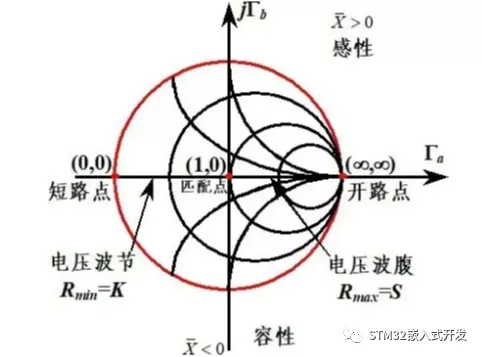

Smith圓圖在RF匹配電路調試中的應用

Smith圓圖上可以反映出如下信息: 阻抗參數Z,導納參數Y,品質因子Q,反射系數,駐波系數,噪聲系數,增益,穩定因子,功率,效率,頻率信息等抗等參數。

是不是一臉懵,我們還是來看阻抗圓圖吧:

阻抗圓圖的構圖原理是利用輸入阻抗與電壓反射系數之間的一一對應關系,將歸一化輸入阻抗表示在反射系數極坐標系中,其特點歸納如下:

上半圓阻抗為感抗,下半圓阻抗為容抗

實軸為純電阻,單位圓為純電抗

實軸的右半軸皆為電壓波腹點(除開路點),左半軸皆為電壓波節點(除短路點)

匹配點(1,0),開路點(∞,∞)和短路點(0,0)

兩個特殊圓:最大的為純電抗圓,與虛軸相切的為匹配圓

兩個旋轉方向:逆時針轉為向負載移動,順時針轉為向波源移動

導納圓圖與阻抗圓圖互為中心對稱,同一張圓圖,即可以當作阻抗圓圖來用,也可以當作導納圓圖來用,但是在進行每一次操作時,若作為阻抗圓圖用則不能作為導納圓圖。

Smith圓圖中,能表示出一些很有意思的特征:

在負載之前串聯或并聯一個可變電感/電容,將得到Smith圓圖上右側的幾條曲線。

對應Smith阻抗圓及導納圓,其運動軌跡如下:

使用Smith阻抗圓時,串聯電感順時針轉,串聯電容逆時針轉

使用Smith導納圓時,并聯

編輯:jq

-

電阻

+關注

關注

86文章

5468瀏覽量

171659 -

pcb

+關注

關注

4317文章

23006瀏覽量

396301 -

阻抗

+關注

關注

17文章

940瀏覽量

45821 -

RF

+關注

關注

65文章

3042瀏覽量

166825 -

電抗

+關注

關注

1文章

24瀏覽量

21466

原文標題:PCBLayout時,要認識到阻抗設計的重要性

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

高壓探頭阻抗的重要性

NLP技術在人工智能領域的重要性

凱迪正大對110kV電力電纜交接試驗的重要性與實施方法簡述

論RISC-V的MCU中UART接口的重要性

模擬前端電路的重要性

蜂鳴器的用途和重要性

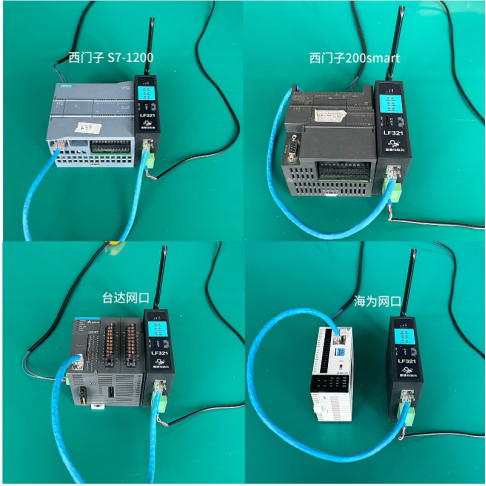

PLC網關的重要性

簡述PCBLayout時阻抗設計的重要性

簡述PCBLayout時阻抗設計的重要性

評論