近日,全球晶圓代工龍頭臺積電宣布推出4nm制程工藝——N4P,希望借此贏得明年蘋果公司A16處理器代工訂單。臺積電表示,憑借5nm(N5)、4nm(N4)、3nm(N3)、以及最新的N4P制程,將能夠?yàn)楫a(chǎn)業(yè)界提供多樣且強(qiáng)大的技術(shù)組合選擇。

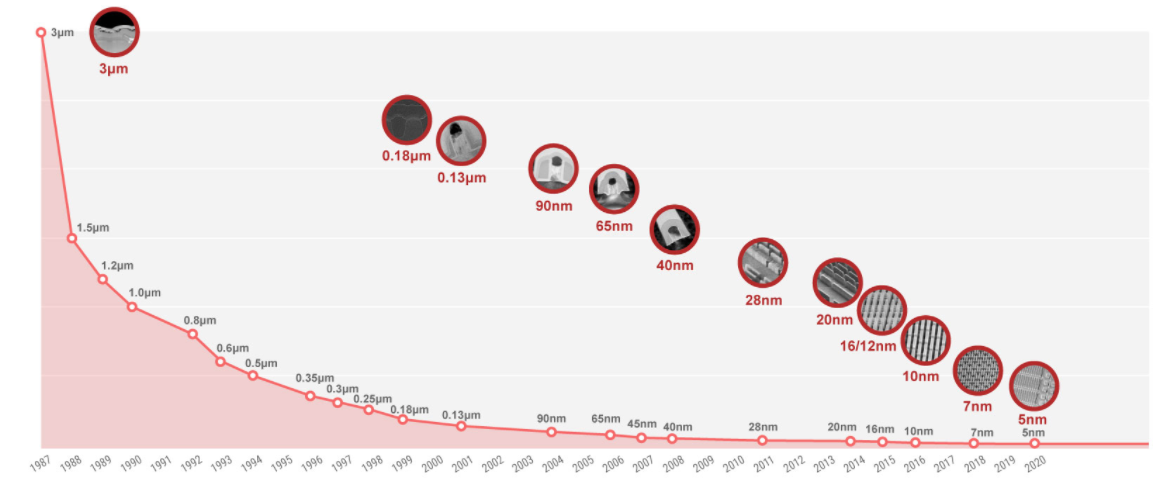

說是4nm工藝,實(shí)際上N4P和此前臺積電推出的N6性質(zhì)一樣,都是當(dāng)前工藝節(jié)點(diǎn)的進(jìn)一步增強(qiáng)版。從下圖能夠看出,在臺積電追隨摩爾定律的工藝節(jié)點(diǎn)推進(jìn)路線圖中,是沒有6nm這一標(biāo)識的。

實(shí)際上,N4P工藝是臺積電5nm工藝的第三個增強(qiáng)版本,繼N5、N5P和N4工藝之后,臺積電在N4P工藝中進(jìn)一步改善了工藝性能。根據(jù)臺積電的介紹,N4P工藝相較于第一代N5工藝,晶體管密度增加了6%,效能上提升了11%,比上一代N4工藝效能提升了6%。此外,N4P工藝進(jìn)一步降低了芯片的功耗,相較N5工藝降低了22%。

此外,在N4P工藝上,臺積電進(jìn)一步減少了光罩層數(shù),進(jìn)而降低了芯片制造的復(fù)雜度,并改善客戶產(chǎn)品的生命周期。為了方便客戶在N5和N4節(jié)點(diǎn)上進(jìn)行產(chǎn)品移植,臺積電表示,將尋求最大限度地提高 N4 和 N5 之間的設(shè)計兼容性,降低將設(shè)計完全移植到新節(jié)點(diǎn)的成本。

臺積電業(yè)務(wù)發(fā)展高級副總裁 Kevin Zhang 博士指出:“通過 N4P工藝,臺積電加強(qiáng)了我們的先進(jìn)邏輯半導(dǎo)體技術(shù)組合,每一項(xiàng)都具有獨(dú)特的性能、功效和成本組合。N4P 經(jīng)過優(yōu)化,可為 HPC 和移動應(yīng)用提供進(jìn)一步增強(qiáng)的先進(jìn)技術(shù)平臺。”

臺積電表示,N4P工藝設(shè)計將得到臺積電針對硅IP和EDA綜合設(shè)計生態(tài)系統(tǒng)的大力支持。得益于臺積電及其 Open Innovation Platform合作伙伴幫助加快產(chǎn)品開發(fā)周期,首批基于 N4P 技術(shù)的產(chǎn)品有望在 2022 年下半年流片。

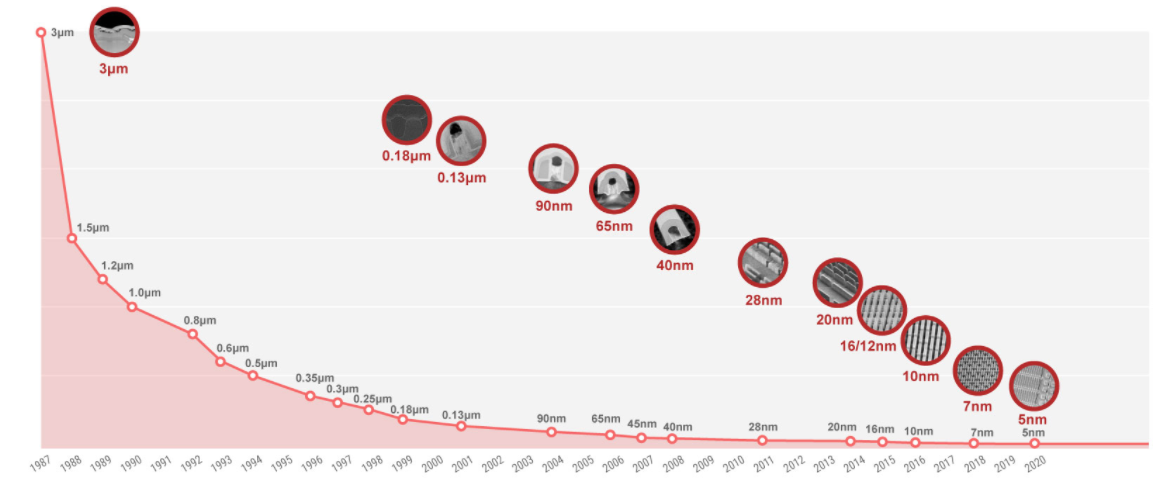

臺積電發(fā)布N4P工藝之后,WikiChip官網(wǎng)針對臺積電的技術(shù)路線進(jìn)行了擴(kuò)充,如上圖所示。我們能夠發(fā)現(xiàn)一個很有趣的現(xiàn)象,當(dāng)工藝節(jié)點(diǎn)一點(diǎn)點(diǎn)縮小后,臺積電在每一個“標(biāo)準(zhǔn)節(jié)點(diǎn)”上,分化出了越來越多的延伸工藝。有從業(yè)者認(rèn)為,臺積電此舉從側(cè)面反應(yīng)出目前摩爾定律演進(jìn)的壓力,后續(xù)N3和N2工藝節(jié)點(diǎn),預(yù)計會延伸出更多的“工藝旁支”,以掩蓋摩爾定律失速的事實(shí)。

從時間節(jié)點(diǎn)上我們不難看出,臺積電N4P工藝的目標(biāo)是明年蘋果A16處理器訂單。根據(jù)此前的報道,蘋果A16處理器確實(shí)將會采用臺積電4nm工藝,以此實(shí)現(xiàn)更強(qiáng)的性能表現(xiàn)。根據(jù)爆料消息,憑借臺積電N4P工藝,以及芯片內(nèi)部的架構(gòu)創(chuàng)新(CPU大核升級為Avalanche、小核升級為Blizzard),A16處理器相較于A15處理器的性能提升將會達(dá)到20%以上,有爆料稱是22%。

可能有人會疑惑,此前臺積電不是說2022年下半年大規(guī)模量產(chǎn)3nm嗎?N4P的出現(xiàn)是否意味著N3的延期,從目前的爆料消息來看,三星和臺積電的3nm進(jìn)展都不如預(yù)想中那么順利,存在漏電和性能提升不達(dá)標(biāo)等情況,預(yù)計臺積電3nm量產(chǎn)時間將推遲4個月左右,很有可能為蘋果A17處理器提供代工服務(wù)。

說是4nm工藝,實(shí)際上N4P和此前臺積電推出的N6性質(zhì)一樣,都是當(dāng)前工藝節(jié)點(diǎn)的進(jìn)一步增強(qiáng)版。從下圖能夠看出,在臺積電追隨摩爾定律的工藝節(jié)點(diǎn)推進(jìn)路線圖中,是沒有6nm這一標(biāo)識的。

圖源:臺積電官網(wǎng)

實(shí)際上,N4P工藝是臺積電5nm工藝的第三個增強(qiáng)版本,繼N5、N5P和N4工藝之后,臺積電在N4P工藝中進(jìn)一步改善了工藝性能。根據(jù)臺積電的介紹,N4P工藝相較于第一代N5工藝,晶體管密度增加了6%,效能上提升了11%,比上一代N4工藝效能提升了6%。此外,N4P工藝進(jìn)一步降低了芯片的功耗,相較N5工藝降低了22%。

此外,在N4P工藝上,臺積電進(jìn)一步減少了光罩層數(shù),進(jìn)而降低了芯片制造的復(fù)雜度,并改善客戶產(chǎn)品的生命周期。為了方便客戶在N5和N4節(jié)點(diǎn)上進(jìn)行產(chǎn)品移植,臺積電表示,將尋求最大限度地提高 N4 和 N5 之間的設(shè)計兼容性,降低將設(shè)計完全移植到新節(jié)點(diǎn)的成本。

臺積電業(yè)務(wù)發(fā)展高級副總裁 Kevin Zhang 博士指出:“通過 N4P工藝,臺積電加強(qiáng)了我們的先進(jìn)邏輯半導(dǎo)體技術(shù)組合,每一項(xiàng)都具有獨(dú)特的性能、功效和成本組合。N4P 經(jīng)過優(yōu)化,可為 HPC 和移動應(yīng)用提供進(jìn)一步增強(qiáng)的先進(jìn)技術(shù)平臺。”

臺積電表示,N4P工藝設(shè)計將得到臺積電針對硅IP和EDA綜合設(shè)計生態(tài)系統(tǒng)的大力支持。得益于臺積電及其 Open Innovation Platform合作伙伴幫助加快產(chǎn)品開發(fā)周期,首批基于 N4P 技術(shù)的產(chǎn)品有望在 2022 年下半年流片。

圖源:WikiChip

臺積電發(fā)布N4P工藝之后,WikiChip官網(wǎng)針對臺積電的技術(shù)路線進(jìn)行了擴(kuò)充,如上圖所示。我們能夠發(fā)現(xiàn)一個很有趣的現(xiàn)象,當(dāng)工藝節(jié)點(diǎn)一點(diǎn)點(diǎn)縮小后,臺積電在每一個“標(biāo)準(zhǔn)節(jié)點(diǎn)”上,分化出了越來越多的延伸工藝。有從業(yè)者認(rèn)為,臺積電此舉從側(cè)面反應(yīng)出目前摩爾定律演進(jìn)的壓力,后續(xù)N3和N2工藝節(jié)點(diǎn),預(yù)計會延伸出更多的“工藝旁支”,以掩蓋摩爾定律失速的事實(shí)。

從時間節(jié)點(diǎn)上我們不難看出,臺積電N4P工藝的目標(biāo)是明年蘋果A16處理器訂單。根據(jù)此前的報道,蘋果A16處理器確實(shí)將會采用臺積電4nm工藝,以此實(shí)現(xiàn)更強(qiáng)的性能表現(xiàn)。根據(jù)爆料消息,憑借臺積電N4P工藝,以及芯片內(nèi)部的架構(gòu)創(chuàng)新(CPU大核升級為Avalanche、小核升級為Blizzard),A16處理器相較于A15處理器的性能提升將會達(dá)到20%以上,有爆料稱是22%。

可能有人會疑惑,此前臺積電不是說2022年下半年大規(guī)模量產(chǎn)3nm嗎?N4P的出現(xiàn)是否意味著N3的延期,從目前的爆料消息來看,三星和臺積電的3nm進(jìn)展都不如預(yù)想中那么順利,存在漏電和性能提升不達(dá)標(biāo)等情況,預(yù)計臺積電3nm量產(chǎn)時間將推遲4個月左右,很有可能為蘋果A17處理器提供代工服務(wù)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

臺積電

+關(guān)注

關(guān)注

44文章

5609瀏覽量

166128 -

晶圓代工

+關(guān)注

關(guān)注

6文章

858瀏覽量

48539 -

5nm

+關(guān)注

關(guān)注

1文章

342瀏覽量

26050

發(fā)布評論請先 登錄

相關(guān)推薦

臺積電美國廠預(yù)計2025年初量產(chǎn)4nm制程

臺積電在美國亞利桑那州的布局正逐步展開,其位于該地的一廠即將迎來重大進(jìn)展。據(jù)悉,該廠將開始生產(chǎn)4nm制程芯片,并預(yù)計在2025年初正式實(shí)現(xiàn)量產(chǎn)。這一里程碑式的進(jìn)展標(biāo)志著

消息稱AMD將成為臺積電美國廠5nm第二大客戶

據(jù)業(yè)界最新消息,AMD即將成為臺積電位于美國亞利桑那州菲尼克斯附近的Fab 21工廠的第二大知名客戶,該工廠已經(jīng)開始試產(chǎn)包括N5、N5P、N4

今日看點(diǎn)丨臺積電美國廠試產(chǎn)5nm,AMD成第二大客戶; 消息稱蘋果正逐漸遠(yuǎn)離產(chǎn)品“一年一更”模式

。 ? 位于亞利桑那州菲尼克斯附近的臺積電Fab 21已開始試產(chǎn)其5nm節(jié)點(diǎn),該工藝節(jié)點(diǎn)系列包括N4

發(fā)表于 10-08 11:10

?840次閱讀

臺積電美國工廠4nm試產(chǎn)成功

近日,全球領(lǐng)先的半導(dǎo)體制造商臺積電傳來振奮人心的消息,其位于美國亞利桑那州的首座晶圓廠成功完成了4nm(N4)工藝的首次試產(chǎn),標(biāo)志著這一耗資

今日看點(diǎn)丨小米造芯曝料:驍龍 8 Gen 1 級別性能;比亞迪方程豹與華為智駕合作

,小米將在2025年上半年推出定制手機(jī)SoC芯片解決方案,據(jù)說該芯片的性能與高通驍龍8 Gen1相當(dāng),同時采用臺積電4nm“

發(fā)表于 08-28 11:42

?718次閱讀

4nm!小米 SoC芯片曝光!

SoC芯片解決方案,據(jù)說該芯片的性能與高通驍龍8 Gen1相當(dāng),同時采用臺積電4nm“N4P”工藝

臺積電美國廠4年未生產(chǎn)一顆芯片

年,計劃引入5nm、4nm工藝。 《紐約時報》分析認(rèn)為工作態(tài)度與生活模式上的文化差異而導(dǎo)致的文化沖突是臺積

臺積電N3P工藝新品投產(chǎn),性能提質(zhì)、成本減負(fù)

N3E工藝的批量生產(chǎn)預(yù)期如期進(jìn)行,其缺陷密度與2020年量產(chǎn)的N5工藝相當(dāng)。臺積

聯(lián)發(fā)科將發(fā)布4nm工藝天璣9300+芯片

4nm工藝打造,采用四顆超大核+四顆大核組合架構(gòu)。天璣9300?Plus處理器作為天璣9300的升級加強(qiáng)版,在配置和性能上均有了顯著提升。采用了高性能的Cortex-X4超大核設(shè)計,主頻高達(dá)3.4GHz,無論是單線程

臺積電升級4nm N4C工藝,優(yōu)化能效與降低成本

在近日舉辦的 2024 年北美技術(shù)研討會上,業(yè)務(wù)發(fā)展副總裁張凱文發(fā)表講話稱:“盡管我們的 5nm 和 4nm 工藝尚未完全成熟,但從 N5 到 N4

臺積電高雄與寶山晶圓廠擴(kuò)建,1.4nm(A14)工藝制造增添兩階段

該項(xiàng)目初期曾規(guī)劃建設(shè)用于2nm工藝的三個設(shè)施(P1、P2和P3裝置),而不僅如此,臺

今日看點(diǎn)丨傳臺積電2nm制程加速安裝設(shè)備;吉利汽車新一代雷神電混系統(tǒng)年內(nèi)發(fā)布

)架構(gòu)量產(chǎn)暖身,預(yù)計寶山P1、P2及高雄三座先進(jìn)制程晶圓廠均于2025年量產(chǎn),并吸引蘋果、英偉達(dá)、AMD及高通等客戶爭搶產(chǎn)能。臺積電對此不發(fā)

發(fā)表于 03-25 11:03

?886次閱讀

臺積電第二代3nm工藝產(chǎn)能頗受客戶歡迎,預(yù)計今年月產(chǎn)量達(dá)10萬片

據(jù)悉,臺積電自2022年12月份起開始量產(chǎn)3nm工藝,然而由于成本考量,第一代3納米工藝僅由蘋果

臺積電3nm工藝預(yù)計2024年產(chǎn)量達(dá)80%

據(jù)悉,2024年臺積電的第二代3nm工藝(稱為N3E)有望得到更廣泛運(yùn)用。此前只有蘋果有能力訂購

臺積電首次提及 1.4nm 工藝技術(shù),2nm 工藝按計劃 2025 年量產(chǎn)

12 月 14 日消息,臺積電在近日舉辦的 IEEE 國際電子器件會議(IEDM)的小組研討會上透露,其 1.4nm 級工藝制程研發(fā)已經(jīng)全面

臺積電推出N4P工藝,“真4nm”還是“數(shù)字游戲”?

臺積電推出N4P工藝,“真4nm”還是“數(shù)字游戲”?

評論