我們用Verilog、VHDL這種硬件描述語言來設計FPGA,是否有一種方式來描述電路?如果采用了這種方式,也會像HDL在FPGA、ASIC領域一樣成為一種主流的趨勢么?我們來看看SkiDL的嘗試。

SKiDL 是一個模塊,允許您使用 Python 緊湊地描述電子電路和組件的互連。 生成的 Python 程序執行電氣規則檢查以查找常見錯誤并輸出用作 PCB 布局工具輸入的網表。

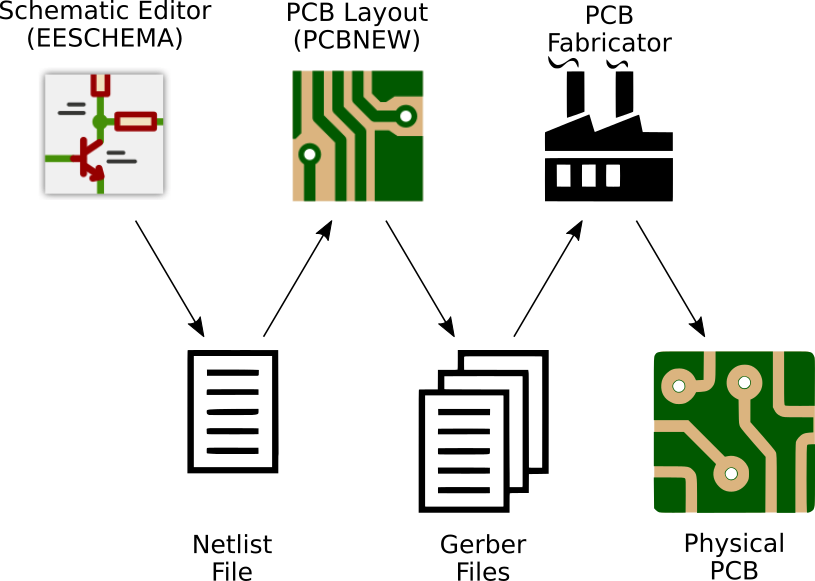

首先,讓我們看看 KiCad 中的“正常”設計流程:

在這里,您在原理圖編輯器(對于 KiCad,即 EESCHEMA)中開始并繪制原理圖。由此,EESCHEMA 生成一個網表文件,其中列出了使用的組件以及它們的引腳如何互連。然后,您將使用 PCB 布局工具(如 KiCad 的 PCBNEW)來排列零件封裝并繪制連接網表中指定的引腳的線跡。

完成后,PCBNEW 會輸出一組 Gerber 文件,這些文件將發送給 PCB 制造商,該制造商將創建物理 PCB 并將其運送給您。然后你會在 Twitter 上張貼他們的照片,然后因為你對這個項目感到厭煩而立即把它們扔進抽屜里幾年。

在基于 SKiDL 的設計流程中,您使用文本編輯器創建 Python 代碼文件,該文件使用 SKiDL 庫來描述組件的互連。該代碼文件由 Python 解釋器執行,并輸出一個網表文件。從那里開始,設計流程與基于原理圖的流程相同(包括將 PCB 傾倒在抽屜中)。

那么,您為什么要使用 SKiDL?以下是 SKiDL 為電子設計帶來的一些功能:

只需要一個文本編輯器和 Python。

具有強大、靈活的語法(因為它是 Python)。

允許對電子電路進行簡潔的描述(考慮不要通過多頁原理圖跟蹤信號)。

允許電子電路的文本描述(考慮對電路使用 diff 和 git)。

對常見錯誤(例如,未連接的設備 I/O 引腳)執行電氣規則檢查 (ERC)。

支持電子設計的線性/分層/混合描述。

促進設計重用(考慮使用 PyPi 和 Github 分發電子設計)。

可以創建其行為/結構以參數方式改變的智能電路模塊(考慮根據您所需的截止頻率自動調整組件值的濾波器)。

可以使用任何 ECAD 工具(只需要兩種方法:一種用于讀取零件庫,另一種用于輸出正確的網表格式)。

利用 Python 生態系統的所有優勢(因為它是 Python)。

免費軟件:MIT 許可證。

開源:https://github.com/devbisme/skidl

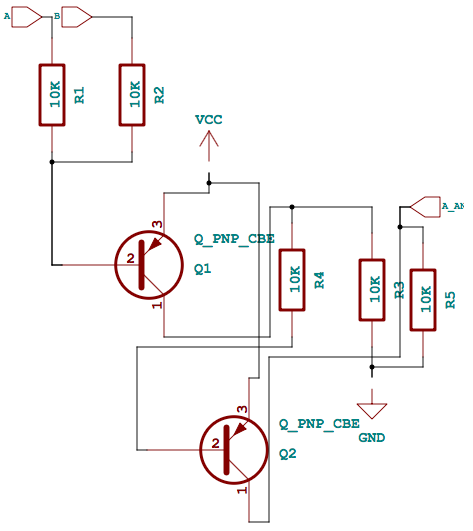

生成原理圖:

盡管 SKiDL 可以讓您避免繁瑣的原理圖繪制,但有些人仍然希望看到他們電路的圖形描述。為此,SKiDL 可以使用 1) graphviz DOT 語言或 2) 作為使用 SVG 的更傳統的示意圖將部件的互連顯示為有向圖。

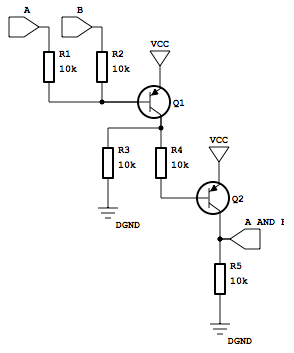

以下電路將用于說明這兩種方法:

The SKiDL script for this circuit is:

from skidl import *

# Create part templates.

q = Part(lib="Device.lib", name="Q_PNP_CBE", dest=TEMPLATE, symtx="V")

r = Part("Device", "R", dest=TEMPLATE)

# Create nets.

gnd, vcc = Net("GND"), Net("VCC")

a, b, a_and_b = Net("A"), Net("B"), Net("A_AND_B")

# Instantiate parts.

gndt = Part("power", "GND") # Ground terminal.

vcct = Part("power", "VCC") # Power terminal.

q1, q2 = q(2)

r1, r2, r3, r4, r5 = r(5, value="10K")

# Make connections between parts.

a & r1 & q1["B", "C"] & r4 & q2["B", "C"] & a_and_b & r5 & gnd

b & r2 & q1["B"]

q1["C"] & r3 & gnd

vcc += q1["E"], q2["E"], vcct

gnd += gndt

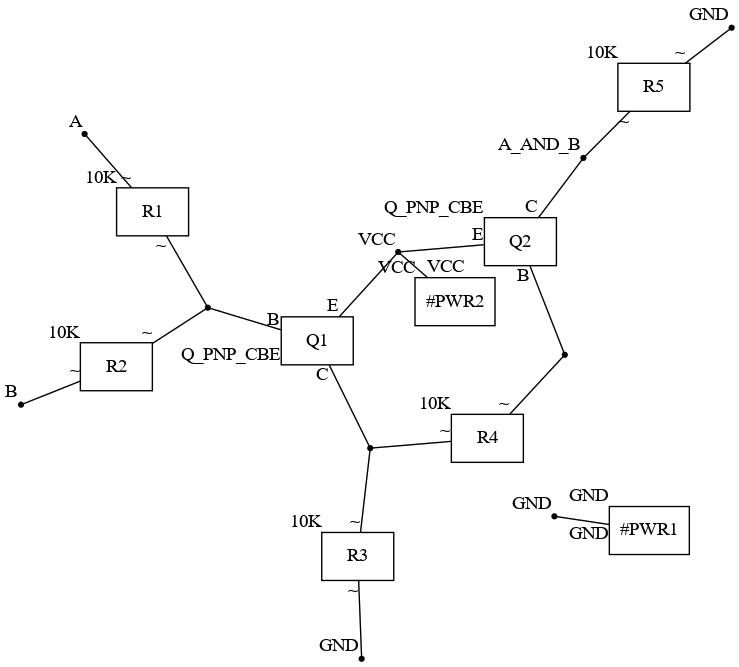

點圖

注意:查看 DOT 文件需要您在系統上安裝 graphviz。

要為電路生成 DOT 文件,只需將以下內容附加到腳本末尾:

generate_dot(file_='and_gate.dot')

運行腳本生成and_gate.dot文件后,您可以使用以下命令將其轉換為位圖文件:

dot -Tpng -Kneato -O and_gate.dot

生成的 and_gate.dot.png 文件如下所示:

-

FPGA

+關注

關注

1626文章

21673瀏覽量

601924 -

Verilog

+關注

關注

28文章

1345瀏覽量

109989 -

vhdl

+關注

關注

30文章

816瀏覽量

128081 -

python

+關注

關注

56文章

4782瀏覽量

84466

原文標題:開源工具SkiDL - 用Python來描述電路

文章出處:【微信號:xiaojiaoyafpga,微信公眾號:電子森林】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何幫助孩子高效學習Python:開源硬件實踐是最優選擇

時序邏輯電路的描述方法有哪些

如何實現Python復制文件操作

opencv-python和opencv一樣嗎

用pycharm進行python爬蟲的步驟

深度學習常用的Python庫

如何使用linux下gdb來調試python程序

eda工具軟件有哪些 EDA工具有什么優勢

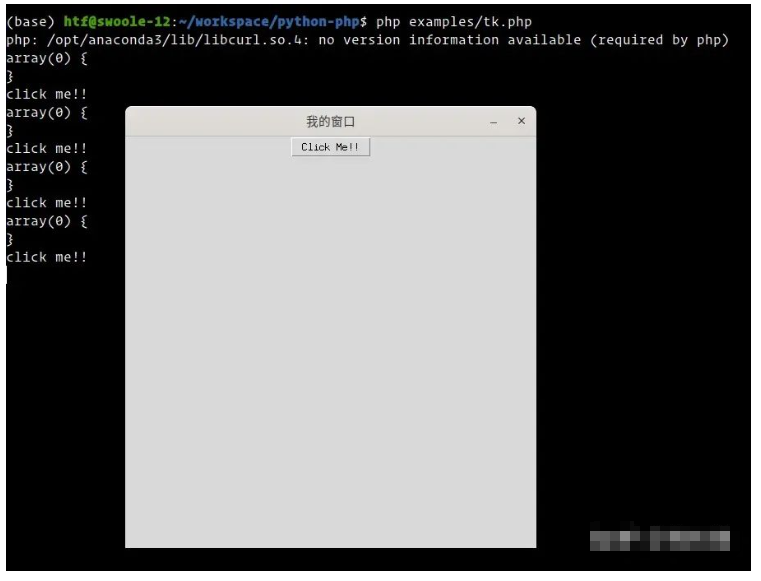

phpy:PHP與Python互調用庫

開源工具SkiDL - 用Python來描述電路

開源工具SkiDL - 用Python來描述電路

評論