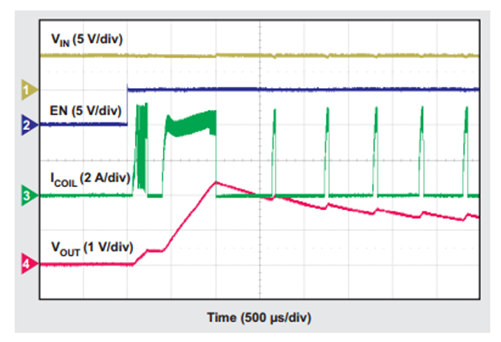

糟糕。我將現場可編程門陣列(FPGA)連接到我的DC/DC轉換器的輸出,現在DC/DC無法啟動。當使用示波器觀察電路時,我看到圖1所示的情形。輸出電壓未進入調壓模式。哪里發生故障了呢?

圖1:由于該FPGA具有較高的啟動負載和極高的去耦電容,DC/DC轉換器無法使其輸出電壓進入調壓模式

FPGA對其電源提出了一些獨特的挑戰。例如,FPGA供應商通常需要其輸入電源擁有數百或甚至數千微法拉(μF)的去耦電容,以便在FPGA產生的瞬變的不同頻率之間維持FPGA電源電壓所需的調節,并減少電源電壓上的紋波。許多FPGA還需要具有特定的啟動時間(不要太快,也不要太慢)和啟動單調性(VOUT在無任何向下移動的直線上達到其設定值)。

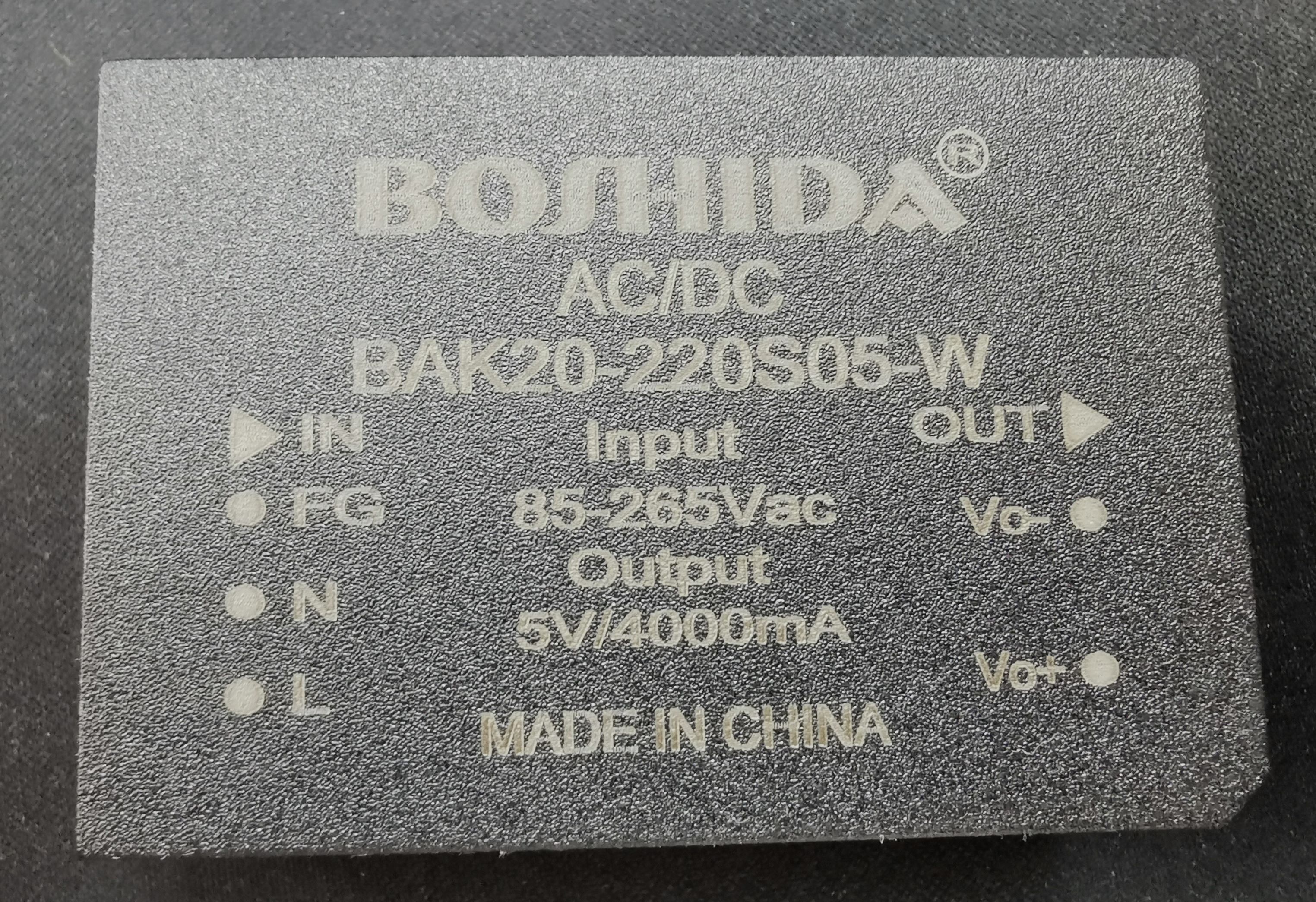

除FPGA相關的設計挑戰外,越來越多的FPGA設計人員還必須為其FPGA設計電源。作為FPGA專家,許多設計師在電源設計方面沒有經驗,因此需要一款極其簡易的電源,而電源模塊就是一個很好的選擇。

電源模塊通過集成許多或全部所需的無源組件來實現簡易性。選擇的組件數量越少,設計的速度就越快,也就越簡單。控制環路補償是首先要集成到電源模塊中的一項功能,但它會限制設計的穩定范圍,而使用大量電容后,內部補償的電源模塊可能會失去穩定性。有關穩定性的指導,請查閱器件數據表和應用說明。在TI許多TPS82xxx電源模塊中使用的DCS控制拓撲結構非常穩定,并支持各種輸出電容。

電源模塊非常小,意味著其使用的引腳較少。引腳數量少意味著器件更簡單,功能也偏少。電源模塊通常集成的另一項功能軟啟動(SS)時間。此時間設置在某些電源模塊內部,如TPS82085,但可使用其他電源模塊上的電容器(如TPS82130)進行編程。通常需要具有一個可編程啟動時間才能滿足特定的啟動時間要求,而且有了該時間也非常有助于啟動與所有電容連接的電源模塊。

時無法啟動。本應用說明介紹了詳細信息,以下對解決此問題的各種方法進行了簡要概括:

換為具有軟啟動引腳的DC/DC轉換器對軟啟動時間進行編程。

使用負荷開關將FPGA與DC/DC解耦。

審核編輯:何安淇

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601902 -

電源管理

+關注

關注

115文章

6155瀏覽量

144240

發布評論請先 登錄

相關推薦

分享一些常見的電路

通過fpga控制lmx2595evm,lmx2595evm的spi接口共有10個針腳,這10個針腳是一些什么信號?

FPGA做深度學習能走多遠?

當前主流的大模型對于底層推理芯片提出了哪些挑戰

關于一些有助于優化電源設計的新型材料

談一談FPGA設計中的功率計算

FPGA電路設計的一些技巧

咨詢一些關于LED燈具的問題

IIoT可以通過多種方式實現智能工廠(還有一些挑戰)

對SDV的一些反思

找一些有關通信電路的資料?

SOLIDWORKS 2024 應對工業設備設計的獨特挑戰

AI算力數據中心的一些挑戰

FPGA對其電源提出了一些獨特的挑戰

FPGA對其電源提出了一些獨特的挑戰

評論