也許你也會跟我一樣認為典型數據表中的某些規格難以理解,這是因為其中涵蓋了一些你不太熟悉的隱含慣例。對許多RF系統工程師而言,其中一種規格便是鎖相環(PLL)中的相位噪聲。當信號源被用作本機振蕩器(LO)或高速時鐘時,相位噪聲性能對滿足系統要求起到了重要作用。最初從數據表中推斷出該規格時似乎就像一個獨立的項目。下面我來講解一下如何通過讀取PLL的相位噪聲規格來對您的無線電或高速應用可達到的性能進行初步評估。

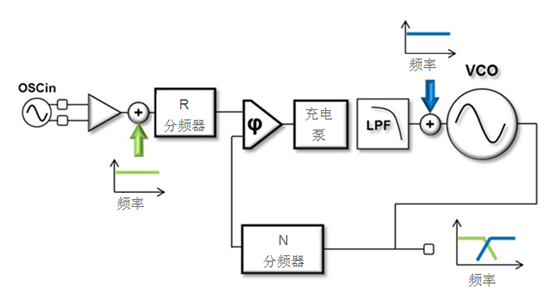

注意,PLL是一種控制回路,這種系統具備頻率響應功能。參考路徑中生成的噪聲受控于回路中對系統輸出的低通頻率響應,而壓控振蕩器(VCO)中生成的噪聲受控于回路中對系統輸出的高通頻率響應。參見圖1。

圖1:鎖相環中的兩個已建模的噪聲源(綠色和藍色)及其對系統輸出的頻率響應

環路帶寬內部(低通頻率響應)PLL產生的噪聲分為兩個部分——閃爍噪聲和白噪聲,但環路帶寬外部(高通頻率響應)的噪聲在數據表中通常表示為開環VCO性能。

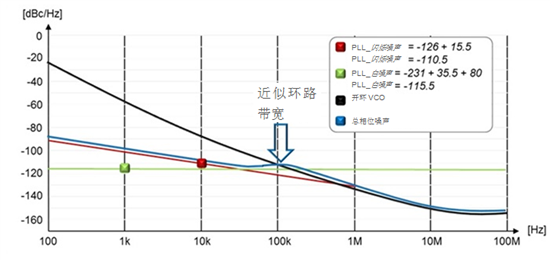

當這些規格被插入動態環路中時,就會對總相位噪聲造成影響。圖2解釋了這三種噪聲規格是如何定義一個近似選中環路帶寬的總相位噪聲的方法。請注意環路帶寬上方總相位噪聲與VCO的跟蹤調諧以及環路帶寬下方總相位噪聲與PLL的跟蹤調諧。

圖2:LMX2592預估相位噪聲曲線圖(帶100-MHz相位檢測器頻率的6-GHz輸出),借助(1)閃爍噪聲、(2)白噪聲和(3)~100-kHz環路帶寬用VCO開環數據

讓我們簡單回顧一下這三種規格:

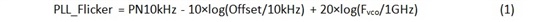

1)閃爍噪聲(圖2中的紅線)是鎖相環的一種特性,會在偏移較低時影響相位噪聲。這種噪聲會隨著偏移頻率的變化而變化,變化率為每10年10分貝。德州儀器對該噪聲進行了規定并將其標準化,使其適用于10-kHz偏移時的1-GHz載波。方程1解除了閃爍噪聲規范化:

其中,Fvco指VCO的頻率。

閃爍噪聲一般不受相位檢測器頻率的影響,只取決于輸出載波頻率。因此,輸出頻率增加一倍,噪聲將增加6分貝。

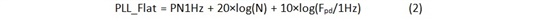

2)白噪聲(圖2中的綠線)亦稱為鎖相環的品質因數,為方便對比,對該噪聲標準化。與在1 Hz載波時的1-Hz帶寬[dBc/Hz]中的輸出信號相比,品質因數的單位是分貝。

其中,N指反饋(參見圖1)的分頻器,Fpd指相位檢測器的運行頻率。

該規格會影響中段偏移頻率的相位噪聲。從方程2中可以看出,相位檢測器頻率越高,環路內部的相位噪聲越佳,相位檢測器頻率每增加一倍,相位噪聲會改善3分貝。

3)開環VCO相位噪聲(圖2中的黑線)與偏移頻率之間的關系是每十年變化20分貝,但是距離載波更近時,會變為每十年變化30分貝。白噪聲一般通過15或20-MHz的偏移頻率傳遞,被稱為噪聲源的本底噪聲。鎖相環中VCO發出的噪聲會進入高通頻率響應。最后,相位噪聲通常會隨著輸出頻率的變化而變化,因此當頻率減半時,相位噪聲會改善6分貝。

現在,您可得出不同偏移頻率和輸出頻率時PLL的近似相位噪聲。您需要從數據表中獲得閃爍噪聲、白噪聲和開環VCO相位噪聲。然后利用公式1和公式2解除這些規格的標準化,然后假設尖銳環路濾波器為第一個近似值(如圖2中所示),即可得出閉環響應的近似值。

估算PLL相位噪聲起初看似很困難,但推斷數據表中所需的規格并使用此處概括的公式將有助于選擇出滿足您系統要求的最佳PLL。通過準確的模擬,德州儀器可以提供兩種計算PLL的相位噪聲的工具:WEBENCH? Clock Architect和PLLatinum? Sim。您可以了解LMX2592和德州儀器的其他RF PLL及合成器,也可以在本頁查看以上工具。

原文鏈接:

https://e2e.ti.com/blogs_/b/analogwire/archive/2016/03/02/understanding-datasheet-phase-noise-specifications-of-a-phase-locked-loop

編輯:jq

-

振蕩器

+關注

關注

28文章

3814瀏覽量

138912 -

分頻器

+關注

關注

43文章

447瀏覽量

49820 -

pll

+關注

關注

6文章

775瀏覽量

135054 -

VCO

+關注

關注

12文章

190瀏覽量

69154 -

相位噪聲

+關注

關注

2文章

180瀏覽量

22838

發布評論請先 登錄

相關推薦

鎖相環PLL的噪聲分析與優化 鎖相環PLL與相位噪聲的關系

opa1622 TINA仿真模型相位結果與數據表中不符是怎么回事?

LMK04816具有雙環PLL的三輸入低噪聲時鐘抖動消除器數據表

PLL1705/PLL1706雙通道PLL多時鐘發生器數據表

LMK04208具有雙環PLL的低噪聲時鐘抖動消除器數據表

帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘抖動清除器數據表

具有雙環路PLL的LMK04228超低噪聲且符合JESD204B標準的時鐘抖動清除器數據表

CDCM7005-SP高性能、低相位噪聲和低偏斜時鐘同步器數據表

如何根據基本的數據表規格估算出PLL的相位噪聲

如何根據基本的數據表規格估算出PLL的相位噪聲

評論