鑒于內核、存儲器、I/O 以及其它電軌的過多電壓電流要求,多核 DSP 實施需要智能電源管理。DSP 內核電壓電源的一個重要性能基準就是能夠根據DSP 使用情況及環境條件實時調節 VCORE。VCORE 命令一般以數字格式提供,電源應能隨時解讀。VCORE 電軌一般具有最大的電流規范,而能夠平衡效率與尺寸的小型電源解決方案也很重要。關鍵在于在 DSP 與模擬 PWM 級之間使用低成本接口來實現這一電壓識別 (VID) 功能。

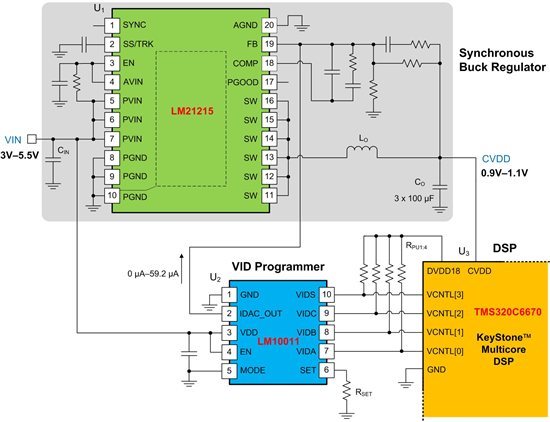

因此,下圖提供了將內核電軌標示為 CVDD 的多核 DSP 加以說明。同時,我也在《EDN》雜志上發表了一篇題為《通過調節穩壓器優化 DSP 功率預算》的文章,深入探討這一主題。

一個額定電流為 15A 的 500KHz 降壓轉換器負責為 CVDD 供電。該設計可使用連接至 VID 編程器的 4 線數字接口實現 VID 控制,其可直接連接至任何模擬功率級或控制器。點擊這里觀看 VID 編程器的視頻演示。

KeyStone DSP與VID功能同步降壓轉換器的原理圖

LM10011與模擬PWM功率級

LM10011 不僅可采集出現在 DSP VCNTL 接口上的 VID 信息,而且還可設置連接至功率級電路反饋 (FB) 引腳的電流 DAC 輸出。在 6 位模式下,既提供支持 940nA 分辨率的 64 種電流設置,又提供優于 1% 的誤差精度。在本例中,CVDD 由 DSP 判定為一個電壓介于 0.9V 至 1.1V 之間的電平,支持 6.4mV 的步進分辨率。無需電平轉換器或膠合邏輯,電阻器 RSET 可決定啟動時的 CVDD 電壓。LM10011 可與任何具有 FB 輸入的電壓、電流或 DCAP 模式 PWM 調節器連接。

歡迎大家盡情講述在您設計 DSP 電源解決方案時遇到的其它問題。

閱讀原文,請參見:http://e2e.ti.com/blogs_/b/powerhouse/archive/2013/10/03/how-to-optimize-your-dsp-power-budget.aspx

編輯:jq

-

dsp

+關注

關注

552文章

7962瀏覽量

348286 -

電源管理

+關注

關注

115文章

6155瀏覽量

144242

發布評論請先 登錄

相關推薦

功率因數優化方法 提高功率因數的好處

英飛凌與AWL-Electricity合作優化無線功率傳輸

DSP控制器的主要優勢是什么?

CRS編譯碼原理和在TI C6000 DSP上的優化實現

優化嵌入式DSP軟件的編譯器

美國科研經費削減,預算壓力增大

Cadence 擴充 Tensilica Vision 產品線,新增毫米波雷達加速器及針對汽車應用優化的新款 DSP

dsp是什么意思 dsp功放對音質到底有沒有提升

dsp是什么意思 dsp怎么調音質最好

高功率PCB中EMC的處理與優化策略

功率模塊銅線鍵合工藝參數優化設計方案

如何優化DSP功率預算

如何優化DSP功率預算

評論