本文闡述了直流偏置電源對敏感模擬應用中所使用運算放大器 (op amp) 產生的影響,此外還涉及了電源排序及直流電源對輸入失調電壓的影響。另外,本文還介紹了一種通過線性穩壓器(一般不具有追蹤能力)輕松實施追蹤分離電源的方法,以幫助最小化直流偏置電源帶來的一些不利影響。

在許多運算放大器電路中,直流偏置電源會影響運算放大器的性能,特別是在與高位計數模數轉換器 (ADC) 一起使用或者用于敏感傳感器電路的信號調節時。直流偏置電源電壓決定放大器的輸入共模電壓以及許多其他規范。

在上電期間,必須協調直流偏置電源的順序來防止運算放大器鎖閉。這樣會毀壞、損壞或者阻止運算放大器正常運行。本文解釋了追蹤電源對運算放大器的重要性,并介紹了一種利用通常不具有追蹤能力的線性穩壓器輕松實施一個追蹤分離電源的方法。

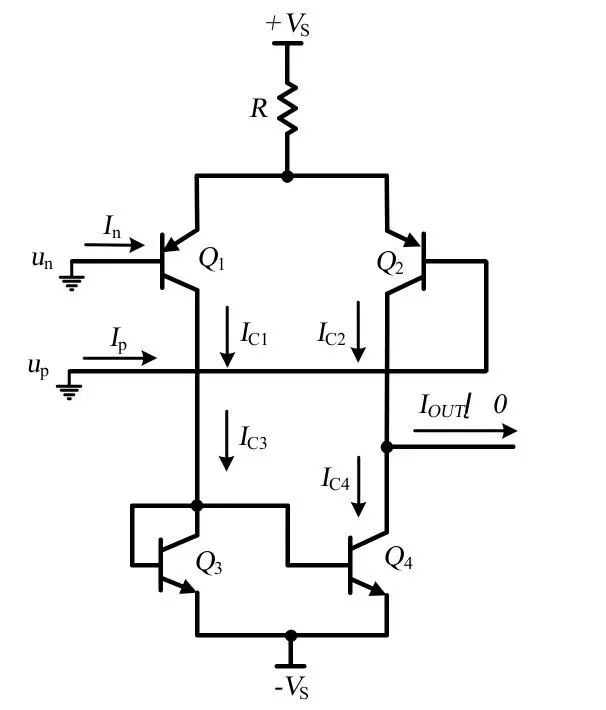

給一個運算放大器供電有兩種常見方法。第一種也是最簡單的一種方法是使用一個單一正電源,如圖 1 (a) 所示。第二種方法是使用一個分離(雙)電源(如圖1 (b) 所示),其同時具有一個正電壓和一個負電壓。這種分離電源在許多模擬電路中都非常有用,因為它允許包括零電壓電位的輸入信號或者在正與負之間搖擺的輸入信號。

不管使用哪一種方法,輸入共模電壓都由電源電壓決定。輸入共模電壓只是兩個電壓的算術平均數。方程式 1 可用于計算輸入共模電壓,其中 VP 為正電壓軌的值,而 VN 為負電壓軌的值。

就一個單電源系統而言,VN 始終為零,因為運算放大器的負電源軌連接到接地電位。

利用圖 1 所示數值,單電源運算放大器具有一個 7.5V 的輸入共模電壓,而分離電源運算放大器有一個 0V 的輸入共模電壓。

一些運算放大器可以工作在單電源結構也可以工作在分離電源結構中。一些運算放大器甚至可以同非對稱分離電源(VP 大小與 VN 不等)一起工作。所有情況下,設計人員都需要驗證運算放大器是否能夠支持期望的電源配置結構。

另外,許多運算放大器都具有使用分離電源的特點。因此,如果一個運算放大器專為單電源結構中分離電源運行而設計,則可能會存在一些性能差異。

使用對稱分離電源時,正負電壓必須互相追蹤,特別是在電路初次上電時。追蹤電源是一種調節其輸出電壓至另一個電壓或信號的電源。對于大多數運算放大器而言,正電源電壓與負電源電壓始終應該大小相等而極性相反。

另外,您也可以對負電源進行調節,使其與正電源大小相等而極性相反。兩種方法都會產生相同的上電波形。

如果兩個電源并非大小相等而極性相反,則運算放大器可在上電期間鎖閉。鎖閉可能會毀壞、損壞或者阻止運算放大器正常運行。

顯示了一個典型運算放大器電源電路的示意圖。此處,一個開關電源提供一個正 18V 和一個負 18V。兩低壓降 (LDO) 線性穩壓器進一步將 ±18V 調節至 ±15V。該 LDO 一般安裝在電源和運算放大器之間,旨在降低開關電源產生的高頻開關噪聲。LDO 具有較高的電源抑制(以比率表示,PSRR),其減弱了寬帶頻率下 LDO 輸入的噪聲。

這樣可幫助向運算放大器提供低噪聲電源。運算放大器還具有自己的 PSRR,其一般在 80dB 以上。然而,運算放大器僅在數千赫茲帶寬時具有高 PSRR,因此 LDO 用于提供高達數百千赫茲帶寬的高 PSRR。

圖 2 所示電路本身沒有追蹤能力。在上電期間,無法保證每個 LDO 與另一個 LDO 大小相等而極性相反。上電期間每個 LDO 的輸出電壓都由所有軟啟動電路、限流、負載電容、負載電流以及輸入電壓決定。

因此,在啟動時兩個電壓大小不同而極性也不相反是有可能的。另外,LDO 上電并提供穩態的 DC 輸出以后,它們仍然有可能大小不等,因為每個 LDO 都具有其自己的輸出電壓精度,而且反饋電阻會因其容差而稍微不同。

除上電期間的鎖閉問題以外,如果每個電源的最終工作 DC 電壓隨時間而變化,則電源會對系統性能產生影響。電源輸出會因線電壓、負載電流變化和溫度變化而不同。電源輸出會在其精度規范內有所不同,其一般為額定輸出電壓的 3% 到 5%。

盡管這些電源電壓的變化很小,但卻會改變運算放大器的輸入共模電壓點,其通常被建模為運算放大器輸入的額外補償電壓。因為運算放大器有高 PSRR,因此建模補償電壓等于輸入共模電壓變化值除以運算放大器的 PSRR。方程式 2可用于計算電源變化引起的運算放大器輸入的補償電壓。

方程式 2 所示 PSRR 以分貝表示,其可在大多數運算放大器產品說明書中找到。方程式 2 給出了以運算放大器輸入為參考的補償電壓。用方程式 2 所得結果乘以運算放大器增益,運算放大器輸出可參考補償電壓。

由于運算放大器的 PSRR 進一步降低了電源的微小變化,因此您可能會錯誤地得出如下結論:電源電壓的微小變化在系統中影響極小或者沒有影響。作為一個定量舉例,我們可對一個全差動運算放大器進行分析,其將信號緩沖至一個 24位 ADC。

顯示的是一個使用全差動運算放大器的簡化示意圖,例如:OPA1632,其配置為一個為 24 位 ADC(例如: ADS1271)提供信號的單位增益緩沖器。該電路是 ADC 評估電路板的簡化示意圖。運算放大器由 LDO 供電,其線壓、負載和溫度精度為 3%。LDO 的輸出電壓針對 ±15V 標稱值進行配置。

如果每個 LDO 的輸出電壓均恰好各是 +15V 和 -15V,則共模輸入電壓剛好為 0V。就本例而言,如果零伏在其輸入上,則我們自 ADC 讀取零計數。那么,電源大小相等而在運算放大器輸入上沒有信號的情況下,您會從 ADC 讀取零計數。

然而,假設正電壓 LDO 輸出增加 3%,仍然沒有超出 LDO 規范。使用 15V 輸出時,這 3% 的變化等同于電源電壓從 450mV 上升到 15.45V。根據數據表,運算放大器的典型 PSRR 為 97dB。

方程式 2 現在可用于計算運算放大器輸入的失調電壓。在運算放大器輸入有一個額外的 3.178μV 失調電壓。由于運算放大器被配置為一個單位增益緩沖器,因此該 3.178μV 也存在于輸出,并施加于ADC。ADC 的滿量程輸入范圍為 ±2.5V,因此每個 ADC 位相當于 298nV。

使用電源產生的補償電壓,ADC 現在讀取 11 個計數,而非零計數。電源在讀取 ADC 計數中引入了一個 DC 補償誤差。該誤差會因 LDO 輸出電壓而不同,而 LDO 輸出電壓又隨時間、溫度、負載電流和輸入電壓而變化。這便使得這種誤差難以通過校準去除掉,也讓 ADC 的低四位變得不確定。

提高 LDO 追蹤和精度(或者漂移)性能的一種簡單方法是將圖 2 所示電路修改為圖 4 所示電路。附加放大器 U1 和四個電阻需要針對 2 增益進行配置。額定值條件下,R3 和 R4 之間的節點應為零伏。因此,R1 的值必須等于 R2,而 R3 的值必須等于 R4。

每個 LDO 的反饋網絡都連接至接地。圖 4 中,反饋電阻連接至接地,且由 U1 的輸出驅動。現在,如果任何電源改變其輸出電壓,則差異出現在 U1 的非反相輸入上,并被增益至原來的 2 倍。由于 U1 的輸出同時驅動兩個 LDO 反饋網絡,因此同時對兩個 LDO 實施校正以強制其輸出大小相等。

必須注意圖 4 所示電路。U1 的輸出可驅動至接近或者等于為 U1 供電電源軌的電壓。如果使用輸入源的 ±18V 為 U1 供電,則輸出可驅動至高達 18V 的電壓。該 18V 輸出應用于 LDO 的反饋引腳,其可能超出其絕對最大電壓額定值。我們可以添加鉗位二極管,在 LDO 的高動態負載環境下、短路條件下或者上電期間保護 LDO 反饋引腳。

顯示的是加裝追蹤電路和保護二極管的 LDO 示意圖。為了讓示意圖更易于理解,U3 的每個電源軌的 10 μF 旁路電容器都已脫去不用。

所示電路使用一個如 TPS7A3001 等可調節、負輸出電壓 LDO 線性穩壓器,以及如 TPS7A4901 等可調節、正輸出電壓 LDO。U3、R7-R10 和 C3 均為增加的組件,用于追蹤。R1、R2、D1-D5 均為增加組件,用于將反饋引腳的電壓控制在其各自產品說明書額定的絕對最大電壓范圍內。

所有其他組件一般都是為了支持 LDO,例如:輸入和輸出電容以及反饋電阻。所示 LDO 可支持 ±36V 范圍的輸入電壓,但由于 TLE2141 運算放大器的建議電壓極限,該電路的輸入電壓降低至 ±22V。可以選擇更高電壓的運算放大器,以覆蓋 LDO 完整的 ±36V 輸入范圍。

在兩種 LDO 反饋控制方案中,追蹤電路都形成了一個附加電壓環路。所增加的運算放大器 U3 的帶寬需要由 C3 降低,以維持系統穩定性。U3 帶寬需要至少為最低 LDO 電壓環路的 1/10。這就意味著 U3 一般只會有幾千赫茲的帶寬。因此,它將不會加到系統的高頻 PSRR。LDO 的 PSRR 主要決定系統的高頻 PSRR。

總結

本文的討論明顯地說明了 DC 偏置電源如何影響運算放大器的一些性能參數。使用本文提供的方程式,可實際測得和計算得到這些影響的大小,以確定其在模擬系統中的影響。此外您還可以了解到,添加一些附加組件來為運算放大器構建一個追蹤電源可以減少輸入補償電壓的多少,可以建立正確序列來減少鎖閉問題的發生,還可以提高用于運算放大器 DC 偏置電源的線性穩壓器的整體電壓精度。

責任編輯:haq

-

放大器

+關注

關注

143文章

13547瀏覽量

213100 -

電流

+關注

關注

40文章

6751瀏覽量

131862 -

電源管理

+關注

關注

115文章

6154瀏覽量

144232 -

電壓

+關注

關注

45文章

5559瀏覽量

115586

發布評論請先 登錄

相關推薦

請問功率放大器和運算放大器的主要區別是什么?

使用運算放大器應注意哪幾個問題

運算放大器只輸出負級電壓嗎為什么

運算放大器的輸入電阻怎么算

什么是理想的運算放大器?運算放大器的基本應用

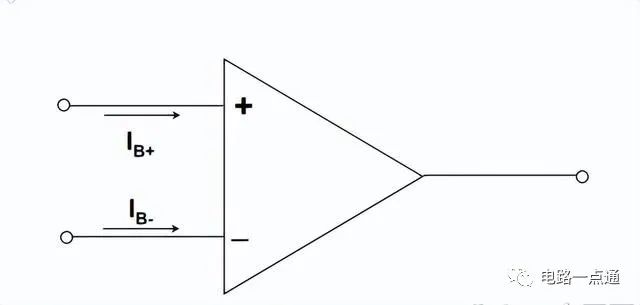

運算放大器的偏置電流是什么

直流偏置電源對敏感模擬應用中所使用運算放大器產生的影響

直流偏置電源對敏感模擬應用中所使用運算放大器產生的影響

評論