在本文中,我們將回顧在早期的DFT(可測試性設計)階段使用邊界掃描標準,以增強可測試性以優化您的測試策略。

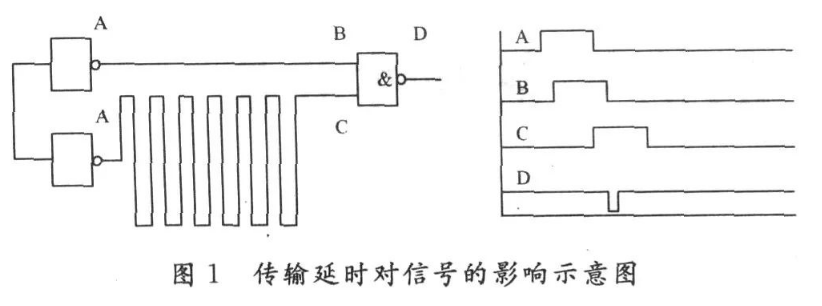

您是否面臨著在高工作頻率的器件下,高速電路板設計信號完整性問題?

由于高速走線的阻抗靈敏度,不可能添加測試探針。

沒有這些測試探針,就不可能對組件互連進行充分的測試。更小和更高的復雜性電路板,電子復雜性的增長使電子電路板密度增加,減少了增加測試接入點的空間。

遵循邊界掃描的可測試性設計指南將有助于您解決上述問題。

什么是“可測試性設計”或DFT ?

它是一個影響組件或系統設計的概念,以促進最大化測試,診斷最大的缺陷。

o 包含附加到設計中的測試電路

o 基于邊界掃描標準IEEE 1149.1

o 最大化缺陷檢測的測試工具和方法

DFT概念的跨度?

器件級一直到系統級

器件級的DFT

器件是系統的基本模塊,一個深思熟慮的DFT體系結構總是會為實現質量確定性帶來回報。

? 越來越多的芯片供應商提供啟用邊界掃描芯片

器件級DFT- 在IEEE 1149.1中

啟用的器件之間的缺陷檢測

通過啟用IEEE 1149.1器件能基本實現,檢測到與其他元器件連接的數字節點上電路板上的結構缺陷。

受限在檢測元器件的IO腳位上

僅限于其上的節點互連類型

器件級DFT- 檢測元器件

內部的缺陷(BIST)

芯片內部的缺陷檢測?

可以利用基本邊界掃描單元對芯片內的節點進行故障檢測。

基于陣列和基于掃描的測試架構,用于內部缺陷檢測。

基于掃描的測試邏輯,以BIST(內置自測)的形式,使測試更加有效和普及,可以隨時在產品生命周期的任何階段使用。

BIST使測試生成和測試應用具有成本效益。這使得增加元器件內部的測試覆蓋率成為可能。

增加所需的片上系統(system-on-chip)和包內系統(system-in-package)設計,以及在生命周期的多個階段(從芯片測試到系統測試)中利用靈活測試方法的架構。

提供在不同階段測試的靈活性,IP可以很容易地重復利用到不同的SOC。

在元器件上啟用DFT將有助于確保芯片無缺陷。

板級DFT

如果可用,最后一步是選擇IEEE 1149.X啟用元器件所需的功能。

設計團隊必須限定JTAG使能部件,以補充到他們的功能需求和規范中。

采購團隊對符合IEEE 1149.1標準的新元器件進行認證,有利于良好DFT的有效進程。

將邏輯電平相同的芯片連接在一起。

良好的做法:

相同邏輯的元器件被鏈接到一起。

最好將電源管理芯片排除在邊界掃描鏈之外,因為這可能會影響板子測試期間的穩定性。

在復雜的設計中,使用CPLD作為掃描路徑連接器(Scan Path Linker)將在測試中提供更好的邊界掃描鏈管理和靈活性。

每個電路(CPU區塊,數據處理區塊,IO管理,內存等)的掃描路徑將有助于獨立控制TAP信號。

由多個板組成的系統的動態配置,使得邊界掃描鏈可以在所有板堆疊后作為一個系統進行測試。

檢測由板對板連接器問題引起的任何缺陷。

對于多板配置可編程元器件,提供在產品生命周期的任何階段運行測試的選項。

o 環境室內測試

o 部署后的現場測試

DFT對測試策略的影響

從器件級到系統級的良好DFT可以在產品生命周期的任何階段提供測試的靈活性。

在電路板或系統的設計階段,早期的邊界掃描電路進行設計審核能確保:

在流程的早期識別缺陷

最大限度地檢測缺陷,減少誤判

減少報廢成本,從而增加投資回報率

減少RMA物流成本

提升品牌價值

責任編輯:haq

-

測試

+關注

關注

8文章

5173瀏覽量

126482 -

電路板

+關注

關注

140文章

4908瀏覽量

97445

原文標題:我們的產品測試還好嗎?

文章出處:【微信號:是德科技KEYSIGHT,微信公眾號:是德科技KEYSIGHT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCIe信號完整性問題解決方案

高速電路設計與信號完整性分析

超常材料應用于電路板進行電源完整性、信號完整性、電磁兼容性研究

高速PCB設計,信號完整性問題你一定要清楚!

構建系統思維:信號完整性,看這一篇就夠了!

要畫好PCB,先學好信號完整性!

分析高速數字PCB設計信號完整性解決方法

如何解決高工作頻率的器件高速電路板設計信號完整性問題

如何解決高工作頻率的器件高速電路板設計信號完整性問題

評論