差分阻抗的概念和實現有時都會被誤解。此外,達到特定差分阻抗的通道設計通常以隨意的方式完成。有時,我回顧舊設計并思考我如何設計走線以達到差分阻抗規范,然后我意識到如果我對差分阻抗有更好的理解,也許我可以做得更好,并為自己省去一些麻煩。

差分阻抗的概念本身是一種數學結構,它不能完全捕捉差分走線中每個信號的行為。差分阻抗是另一個重要值的捷徑,奇模阻抗,反之亦然。那么我們需要針對哪些設計以及如何確保信號在接收器處正確解碼?繼續閱讀以更深入地了解如何根據差分阻抗規范進行設計以及它對您的設計意味著什么。

差分阻抗定義

差分阻抗與差分信號的基本特性有關。所有差分信號都由接收器組件解釋為差分信號(因此稱為“差分”)。考慮差分信號的一種方式是:它是一種傳播的電磁干擾,涉及兩個不同的信號,理想情況下沿著一對走線一起發送。當我們說“電磁干擾”時,我們指的是兩條軌跡周圍的電場和磁場分布。畢竟,這就是 PCB 中導體的全部意義所在:引導和傳輸布局周圍的電磁場。

因此,看看這對信號產生的電磁干擾如何沿兩條跡線傳播是很有趣的。為此,我們需要:

- 電磁場所經歷的傳輸線阻抗

- 這種干擾的傳播常數

如果您知道這些值之一,那么您就可以計算出另一個值。設計特定差分阻抗的重點是確保我們注入通道的電磁場被解釋為在通道負載端接收到的相同(或幾乎相同)的電磁場。

這里應該有趣的是如何使用每個跟蹤生成的字段。我的意思是,我們關心兩個信號(它們的場)之間的差異,或者它們的總和,這取決于接收器的功能。因此,就 Telegrapher 方程而言,我們想看看這兩個信號的差異的傳播,這是一個數學要求很高的主題,需要定義跡線之間的互電容和電感。

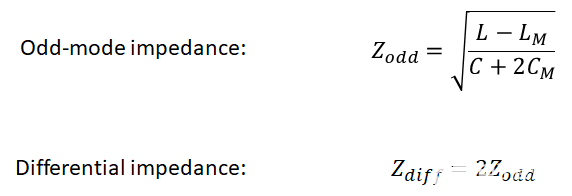

差分阻抗公式

計算差分阻抗是計算另一個重要量的練習,即奇模阻抗。當兩條走線作為差分對布線并用差分信號驅動時,單條走線的阻抗將是奇模阻抗值。

根據奇模阻抗定義差分阻抗。

不幸的是,對于差分阻抗,或更具體地說,奇模阻抗,沒有很多好的分析模型。如果您查看 Brian C. Wadell 的傳輸線設計手冊,您會發現確定一對微帶線的阻抗需要使用 70 個公式(參見第 4.5 節)。這不是印刷錯誤,它確實需要總計計算一對微帶線的奇模或偶模阻抗的 70 個公式。如果您想使用共面排列或不對稱軌跡,您將需要更少的公式,但您需要計算橢圓積分,這是我從未做過的事情,并且會采用像 MATLAB 或 Mathematica 這樣的應用程序。

您可以直接從麥克斯韋方程中獲得互感或互電容,盡管這些結果是許多研究論文的主題,而且結果并不總是那么容易使用。它們往往涉及一組具有多個參數的丑陋公式。這就是為什么您會在網上看到如此多的差分阻抗計算器僅使用 IPC-2141A 公式的原因,這些公式是使用較少公式的近似值。

您應該使用特征阻抗還是奇模阻抗?

簡而言之,奇模阻抗是用于端接的值。關于奇模阻抗,我希望很久以前就有人告訴我一些非常重要的事情需要注意:

- 走線的奇模阻抗并不總是與走線的特征阻抗相同。

如果你翻轉這個,我們可以重述上面的內容如下:

- 特定奇模阻抗所需的走線寬度并不總是與特定特征阻抗所需的走線寬度相同。

換句話說,您的信號標準的差分阻抗規范列出了特定的差分阻抗,您需要通過設計奇模阻抗來達到這一點。因此,通常為接收器的并聯端接引用的值通常是奇模阻抗的兩倍,但走線的每一端只關心每條走線的奇模阻抗,而不必關心差分阻抗。

根據間距和電介質厚度,您可能能夠將特征阻抗走線寬度設置為接近與奇模阻抗走線寬度相同的值。

計算寬度和間距

如果您計算出走線達到特征阻抗目標(即50 歐姆)所需的寬度,然后將該寬度插入差分阻抗計算器中,您會發現您不會總是得到有用的間距結果; 間距可能太小(<4 密耳)并且可能超出了非常薄的電介質的制造能力。相反,對于較厚的電介質,間距最終可能會非常大。實際上,在2 層標準厚度 PCB 上,在標準核心上,微帶達到 50 歐姆阻抗所需的走線寬度約為 105 歐姆。為了使單個跡線具有等于特征阻抗的奇模阻抗,您的場解算器會告訴您需要將跡線分開大量。如果您使用場解算器,您會發現當間距約為 10 英寸時,它可能會停止收斂!顯然,這也沒有用。

一般來說,有許多走線間距和寬度組合可以讓您達到差分阻抗規格。您真正設計的是奇模阻抗,而不是差分阻抗,差分阻抗只是定義奇模阻抗的規范。那么,我們不禁要問,在沒有公式的情況下,我們如何確定奇模阻抗以及客觀上“最佳”的走線寬度和間距組合?

比較差分微帶線的寬度和間距

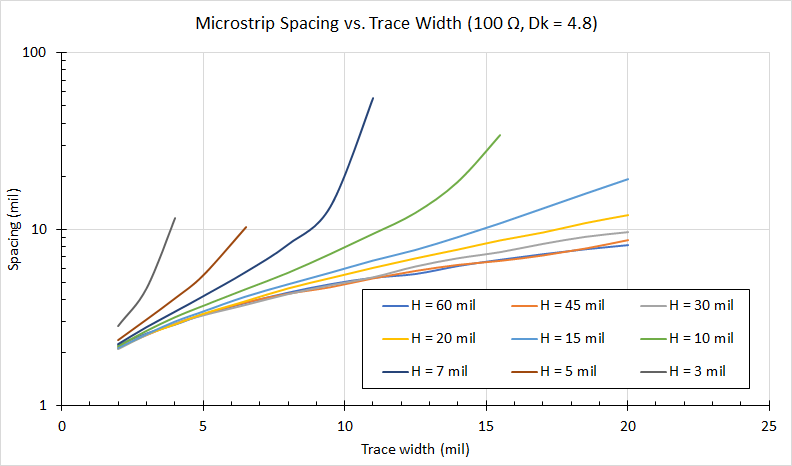

要了解走線寬度和間距的哪種組合會提供所需的差分阻抗,讓我們看一些仿真結果。在下面的示例中,我將運行以下過程

- 計算差分微帶線對中特定走線寬度所需的走線間距,目標是達到 100 歐姆的目標差分阻抗。

- 掃描多個電介質厚度值(到微帶參考平面的距離)。

- 對于每個電介質厚度值,請注意 50 歐姆特性阻抗所需的走線寬度。

我將在 Altium Designer 中使用層堆棧管理器執行這些操作,以便用戶可以復制它們。在下圖中,我展示了不同走線寬度和電介質厚度的差分微帶線所需的一組間距值(下面標記為 H,針對 100 歐姆差分阻抗目標和 Dk = 4.8 繪制,不考慮色散或粗糙度)。這里的想法是確定給定寬度所需的間距,目標是達到特定的差分阻抗值。

圖 1. 間距和寬度值對將在不同厚度的 Dk = 4.8 基板上提供 100 歐姆的差分阻抗。

請注意,為清楚起見,y 軸采用對數刻度。我們可以為其他 Dk 值和差分阻抗值生成一組新曲線。這些曲線應該說明電介質厚度的作用;隨著微帶線與其接地平面的距離增加,達到 100 歐姆阻抗所需的寬度與間距比對接地距離的依賴程度降低(參見 60 密耳和 45 密耳阻抗曲線)。

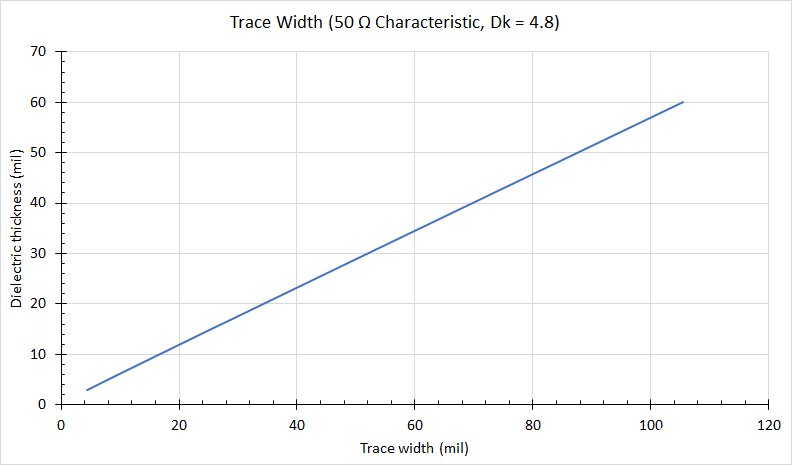

上面顯示的寬度值與 50 歐姆特性阻抗所需的值相比如何?下圖顯示了這些值。這是一個很好的線性模型,它說明了在較寬的走線寬度處發生的飽和;當軌跡很寬時,寬厚比變得恒定。

圖 2. Dk = 4.8 襯底上特性阻抗為 50 歐姆時的電介質厚度與走線寬度的關系。

現在根據上面顯示的特征阻抗和走線寬度/間距對的值,我們可以確定導致 50 歐姆奇模阻抗的走線寬度也產生 50 歐姆特征阻抗的間距。

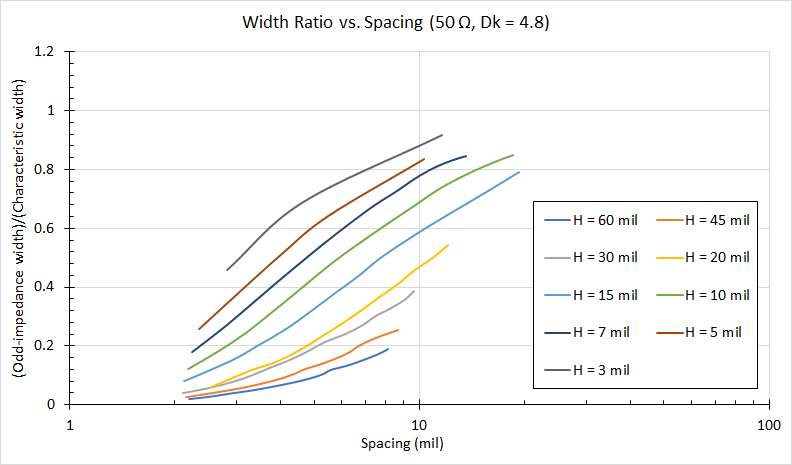

圖 3. 不同厚度的 Dk = 4.8 基板上 100 歐姆差分阻抗的間距和寬度比對。

這個圖可能看起來很復雜,但它有一個簡單的解釋。每條曲線在 y 軸上與 1 相交的間距值將導致差分對中的走線寬度等于走線不是差分對的一部分時的走線寬度,同時仍提供相同的阻抗。換句話說,隔離的走線和成對的走線在每個電介質厚度的特定間距值下將具有相同的寬度和 50 歐姆阻抗。

不幸的是,奇模阻抗和特性阻抗永遠不相等;這只會發生在大間距限制中,或者當成對被無限遠的距離分開時!y = 1 的值是此圖上的漸近線。如果電介質很薄(<15 密耳),那么對于差分對中給定的走線間距,您將更接近于使走線寬度重合。

舉個例子,如果我們采用圖 3 中 5 密耳的電介質,我們計算奇模阻抗的走線寬度,我們將得到 6.184 密耳。如果我然后使用它來計算特征阻抗,我會得到 55 歐姆的值,或者只有 10% 的偏差。這是在某些信號標準中您可以接受的阻抗偏差的最高端。例如,USB SuperSpeed 更寬容,允許差分阻抗(因此奇模阻抗)有很大的變化。

使用間距和走線寬度為您帶來優勢

您可能想知道,具有同時適用于特征阻抗和奇模阻抗的單一走線寬度真的那么重要嗎?這有三個很好的理由:

- 它將設計差分通道的問題從涉及 2 個變量的問題轉換為涉及 1 個變量:間距。

- 當您僅設計適用于差分和單端阻抗的單一跡線寬度時,制造商更容易確保受控阻抗。根據您設計中的容差,您可以使用一種寬度來滿足單端和差分規格的容差。

- 您可以在路由差分通道時解耦走線,甚至非常靠近接收器,而且您不必擔心反射,因為從接收器看,走線的每一端都將匹配每個端口的輸入阻抗.

請注意,這在較薄的電介質上更容易,在厚電介質上,特征跡線寬度和奇模跡線寬度之間的對應關系不會幾乎相同。如果您想在使用較厚的電介質時有更多的回旋余地,您還可以選擇另一種樣式,例如共面差分對。

當您需要使用定義的差分阻抗進行設計和布線時,請使用Altium Designer ? 中最好的一組 PCB 布線、布局和仿真功能。集成的設計規則引擎和層堆棧管理器為您提供設計特定差分對阻抗所需的一切,并在 PCB 中快速布線。當您完成設計并希望將文件發布給您的制造商時,Altium 365 ?平臺可以輕松地協作和共享您的項目。

編輯:fqj

-

接收器

+關注

關注

14文章

2458瀏覽量

71796 -

電磁干擾

+關注

關注

36文章

2285瀏覽量

105312 -

差分信號

+關注

關注

3文章

367瀏覽量

27649 -

差分阻抗

+關注

關注

1文章

26瀏覽量

10357

發布評論請先 登錄

相關推薦

如何按照差分阻抗規范來進行設計

如何按照差分阻抗規范來進行設計

評論