阻抗匹配(Impedance matching)是微波電子學里的一部分,主要用于傳輸線上,來達至所有高頻的微波信號皆能傳至負載點的目的,不會有信號反射回來源點,從而提升能源效益。

大體上,阻抗匹配有兩種,一種是透過改變阻抗力(lumped-circuit matching),另一種則是調整傳輸線的波長(transmission line matching)。

要匹配一組線路,首先把負載點的阻抗值除以傳輸線的特性阻抗值來標準化,然后把數值劃在史密夫圖表上。

改變阻抗力

把電容或電感與負載串聯起來,即可增加或減少負載的阻抗值,在圖表上的點會沿著代表實數電阻的圓圈走動。假如把電容或電感接地,首先圖表上的點會以圖中心旋轉180度,然后才沿電阻圈走動,再沿中心旋轉180度。重覆以上方法直至電阻值變成1,即可直接把阻抗力變為零完成匹配。

調整傳輸線

由負載點至來源點加長傳輸線,在圖表上的圓點會沿著圖中心以逆時針方向走動,直至走到電阻值為1的圓圈上,即可加電容或電感把阻抗力調整為零,完成匹配。

阻抗匹配則傳輸功率大,對于一個電源來講,單它的內阻即是負載時,輸出功率最大,此時阻抗匹配。最大功率傳輸定理,假如是高頻的話,就是無反射波。對于普通的寬頻放大器,輸出阻抗50Ω,功率傳輸電路中需要考慮阻抗匹配,可是假如信號波長遠遠大于電纜長度,即纜長可以忽略的話,就無須考慮阻抗匹配了。阻抗匹配是指在能量傳輸時,要求負載阻抗要和傳輸線的特征阻抗相等,此時的傳輸不會產生反射,這表明所有能量都被負載吸收了。反之則在傳輸中有能量損失。高速PCB布線時,為了防止信號的反射,要求是線路的阻抗為50歐姆。這是個大約的數字,一般規定同軸電纜基帶50歐姆,頻帶75歐姆,雙絞線則為100歐姆,只是取個整而已,為了匹配方便。

阻抗從字面上看就與電阻不一樣,其中只有一個阻字是相同的,而另一個抗字呢?簡單地說,阻抗就是電阻加電抗,所以才叫阻抗;周延一點地說,阻抗就是電阻、電容抗及電感抗在向量上的和。在直流電的世界中,物體對電流阻礙的作用叫做電阻,世界上所有的物質都有電阻,只是電阻值的大小差異而已。電阻小的物質稱作良導體,電阻很大的物質稱作非導體,而最近在高科技領域中稱的超導體,則是一種電阻值幾近于零的東西。但是在交流電的領域中則除了電阻會阻礙電流以外,電容及電感也會阻礙電流的活動,這種作用就稱之為電抗,意即抵抗電流的作用。電容及電感的電抗分別稱作電容抗及電感抗,簡稱容抗及感抗。它們的計量單位與電阻一樣是歐姆,而其值的大小則和交流電的頻率有關系,頻率愈高則容抗愈小感抗愈大,頻率愈低則容抗愈大而感抗愈小。此外,電容抗和電感抗還有相位角度的題目,具有向量上的關系式,因此才會說:阻抗是電阻與電抗在向量上的和。

阻抗匹配是指負載阻抗與激勵源內部阻抗互相適配,得到最大功率輸出的一種工作狀態。對于不同特性的電路,匹配條件是不一樣的。

在純電阻電路中,當負載電阻即是激勵源內阻時,則輸出功率為最大,這種工作狀態稱為匹配,否則稱為失配。

當激勵源內阻抗和負載阻抗含有電抗成份時,為使負載得到最大功率,負載阻抗與內阻必須滿足共扼關系,即電阻成份相等,電抗成份只數值相等而符號相反。這種匹配條件稱為共扼匹配。

一. 阻抗匹配的研究

在高速的設計中,阻抗的匹配與否關系到信號的質量優劣。阻抗匹配的技術可以說是豐富多樣,但是在具體的系統中怎樣才能比較公道的應用,需要衡量多個方面的因素。例如我們在系統中設計中,很多采用的都是源端的串連匹配。對于什么情況下需要匹配,采用什么方式的匹配,為什么采用這種方式。

例如:差分的匹配多數采用終端匹配;時鐘采用源端匹配。

1.1 串聯終端匹配

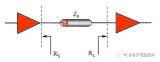

串聯終端匹配的理論出發點是在信號源端阻抗低于傳輸線特征阻抗的條件下,在信號的源端和傳輸線之間串接一個電阻R,使源真個輸出阻抗與傳輸線的特征阻抗相匹配,抑制從負載端反射回來的信號發生再次反射。

串聯終端匹配后的信號傳輸具有以下特點:

A 由于串聯匹配電阻的作用,驅動信號傳播時以其幅度的50%向負載端傳播;

B 信號在負載真個反射系數接近+1,因此反射信號的幅度接近原始信號幅度的50%;

C 反射信號與源端傳播的信號疊加,使負載端接受到的信號與原始信號的幅度近似相同;

D 負載端反射信號向源端傳播,到達源端后被匹配電阻吸收;

E 反射信號到達源端后,源端驅動電流降為0,直到下一次信號傳輸。

相對并聯匹配來說,串聯匹配不要求信號驅動用具有很大的電流驅動能力。

選擇串聯終端匹配電阻值的原則很簡單,就是要求匹配電阻值與驅動器的輸出阻抗之和與傳輸線的特征阻抗相等。理想的信號驅動器的輸出阻抗為零,實際的驅動器總是有比較小的輸出阻抗,而且在信號的電平發生變化時,輸出阻抗可能不同。比如電源電壓為+4.5V的CMOS驅動器,在低電平時典型的輸出阻抗為37Ω,在高電平時典型的輸出阻抗為45Ω;TTL驅動器和CMOS驅動一樣,其輸出阻抗會隨信號的電平大小變化而變化。因此,對TTL或CMOS電路來說,不可能有十分正確的匹配電阻,只能折衷考慮。

鏈狀拓撲結構的信號網路不適合使用串聯終端匹配,所有的負載必須接到傳輸線的末端。否則,接到傳輸線中間的負載接受到的波形就會像圖3.2.5中C點的電壓波形一樣。可以看出,有一段時間負載端信號幅度為原始信號幅度的一半。顯然這時候信號處在不定邏輯狀態,信號的噪聲容限很低。

串聯匹配是最常用的終端匹配方法。它的優點是功耗小,不會給驅動器帶來額外的直流負載,也不會在信號和地之間引進額外的阻抗;而且只需要一個電阻元件。

1.2 并聯終端匹配

并聯終端匹配的理論出發點是在信號源端阻抗很小的情況下,通過增加并聯電阻使負載端輸進阻抗與傳輸線的特征阻抗相匹配,達到消除負載端反射的目的。實現形式分為單電阻和雙電阻兩種形式。

并聯終端匹配后的信號傳輸具有以下特點:

A 驅動信號近似以滿幅度沿傳輸線傳播;

B 所有的反射都被匹配電阻吸收;

C 負載端接受到的信號幅度與源端發送的信號幅度近似相同。

在實際的電路系統中,芯片的輸進阻抗很高,因此對單電阻形式來說,負載真個并聯電阻值必須與傳輸線的特征阻抗相近或相等。假定傳輸線的特征阻抗為50Ω,則R值為50Ω。假如信號的高電平為5V,則信號的靜態電流將達到100mA。由于典型的TTL或CMOS電路的驅動能力很小,這種單電阻的并聯匹配方式很少出現在這些電路中。

雙電阻形式的并聯匹配,也被稱作戴維南終端匹配,要求的電流驅動能力比單電阻形式小。這是由于兩電阻的并聯值與傳輸線的特征阻抗相匹配,每個電阻都比傳輸線的特征阻抗大。考慮到芯片的驅動能力,兩個電阻值的選擇必須遵循三個原則:

⑴ 兩電阻的并聯值與傳輸線的特征阻抗相等;

⑵ 與電源連接的電阻值不能太小,以免信號為低電平時驅動電流過大;

⑶ 與地連接的電阻值不能太小,以免信號為高電平時驅動電流過大。

并聯終端匹配優點是簡單易行;顯而易見的缺點是會帶來直流功耗:單電阻方式的直流功耗與信號的占空比緊密相關?;雙電阻方式則無論信號是高電平還是低電平都有直流功耗。因而不適用于電池供電系統等對功耗要求高的系統。另外,單電阻方式由于驅動能力題目在一般的TTL、CMOS系統中沒有應用,而雙電阻方式需要兩個元件,這就對PCB的板面積提出了要求,因此不適適用于高密度印刷電路板。

二. 將信號的傳輸看成軟管送水澆花

2.1 數字系統之多層板信號線(Signal Line)中,當出現方波信號的傳輸時,可將之假想成為軟管(hose)送水澆花。一端于手握處加壓使其射出水柱,另一端接在水龍頭。當握管處所施壓的力道恰好,而讓水柱的射程正確灑落在目標區時,則施與受兩者皆歡而順利完成使命,難道一種得心應手的小小成就?

2.2 然而一旦用力過度水注射程太遠,不但騰空越過目標浪費水資源,甚至還可能因強力水壓無處宣泄,以致往來源反彈造成軟管自龍頭上的擺脫!不僅任務失敗橫生挫折,而且還大捅紕漏滿臉豆花呢!

2.3 反之,當握處之擠壓不足以致射程太近者,則照樣得不到想要的結果。過猶不及皆非所欲,唯有恰到好處才能正中下懷皆大歡喜。

2.4 上述簡單的生活細節,正可用以說明方波(Square Wave)信號(Signal)在多層板傳輸線(Transmission Line,系由信號線、介質層、及接地層三者所共同組成)中所進行的快速傳送。此時可將傳輸線(常見者有同軸電纜Coaxial Cable,與微帶線Microstrip Line或帶線Strip Line等)看成軟管,而握管處所施加的壓力,就比如板面上“接受端”(Receiver)元件所并聯到GND的電阻器一般,可用以調節其終點的特性阻抗 (Characteristic Impedance),使匹配接受端元件內部的需求。

三. 傳輸線之終端控管技術(Termination)

3.1由上可知當“信號”在傳輸線中飛奔旅行而到達終點,欲進進接受元件(如CPU或Memory等大小不同的IC)中工作時,則該信號線本身所具備的“特性阻抗”,必須要與終端元件內部的電子阻抗相互匹配才行,如此才不致任務失敗白忙一場。用術語說就是正確執行指令,減少噪聲干擾,避免錯誤動作”。一旦彼此未能匹配時,則必將會有少許能量回頭朝向“發送端”反彈,進而形成反射噪聲的煩惱。

3.2 當傳輸線本身的特性阻抗(Z0)被設計者訂定為28ohm時,則終端控管的接地的電阻器(Zt)也必須是28ohm,如此才能協助傳輸線對Z0的保持,使整體得以穩定在28ohm的設計數值。也唯有在此種Z0=Zt的匹配情形下,信號的傳輸才會最具效率,其“信號完整性”(Signal Integrity,為信號品質之專用術語)也才最好。

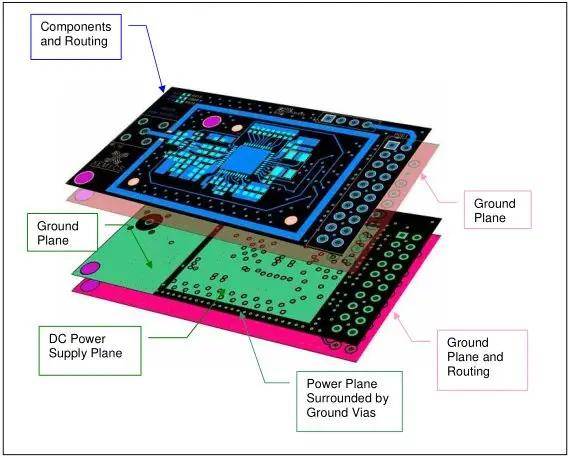

四. 特性阻抗(Characteristic Impedance)

4.1 當某信號方波,在傳輸線組合體的信號線中,以高準位(High Level)的正壓信號向前推進時,則距其最近的參考層(如接地層)中,理論上必有被該電場所感應出來的負壓信號伴隨前行(即是正壓信號反向的回回路徑 Return Path),如此將可完成整體性的回路(Loop)系統。該“信號”前行中若將其飛行時間暫短加以凍結,即可想象其所遭受到來自信號線、介質層與參考層等所共同呈現的瞬間阻抗值(Instantaneous Impedance),此即所謂的“特性阻抗”。是故該“特性阻抗”應與信號線之線寬(w)、線厚(t)、介質厚度(h)與介質常數(Dk)都扯上了關 系。

4.2 阻抗匹配不良的后果

由于高頻信號的“特性阻抗”(Z0)原詞甚長,故一般均簡稱之 為“阻抗”。讀者千萬要小心,此與低頻AC交流電(50Hz)的電線(并非傳輸線)中,所出現的阻抗值(Z)并不完全相同。數字系統當整條傳輸線的Z0都 能治理妥善,而控制在某一范圍內(±10﹪或±5﹪)者,此品質良好的傳輸線,將可使得噪聲減少,而誤動作也可避免。但當上述微帶線中Z0的四種變數(w、t、h、r)有任一項發生異常,例如信號線出現缺口時,將使得原來的Z0忽然上升(見上述公式中之Z0與W成反比的事實),而無法繼續維持應有的穩定均勻(Continuous)時,則其信號的能量必然會發生部分前進,而部分卻反彈反射的缺失。如此將無法避免噪聲及誤動作了。例如澆花的軟管忽然被踩住,造成軟管兩端都出現異常,正好可說明上述特性阻抗匹配不良的題目。

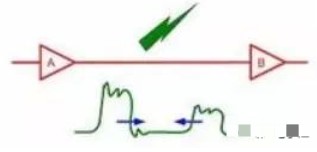

4.3 阻抗匹配不良造成噪聲上述部分信號能量的反彈,將造成原來良好品質的方波信號,立即出現異常的變形(即發生高準位向上的Overshoot,與低準位向下的Undershoot,以及二者后續的Ringing)。此等高頻噪聲嚴重時還會引發誤動作,而且當時脈速度愈快時噪聲愈多也愈輕易出錯。

原文標題:什么是阻抗匹配?

文章出處:【微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

并聯

+關注

關注

5文章

235瀏覽量

35337 -

負載

+關注

關注

2文章

560瀏覽量

34253 -

阻抗

+關注

關注

17文章

941瀏覽量

45834

原文標題:什么是阻抗匹配?

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

在阻抗匹配中50歐姆好像是一個很特殊的值,為什么呢?

PCB阻抗匹配過孔的多個因素你知道哪些?

什么是阻抗?為什么要做阻抗匹配?

高速差分信號阻抗匹配詳解

阻抗匹配的原理分析?

無源探頭的阻抗匹配如何操作

為什么要阻抗匹配?怎么進行阻抗匹配?

一文詳細了解阻抗匹配

一文詳細了解阻抗匹配

評論