寫在前面

IP是什么?簡單來講,IP就是Xilinx或者第三方開發者把自己的邏輯模塊封裝成一個黑盒子,然后拿出來給別人用。那什么又是黑盒子?黑盒子就是你看不到里面的東西,你只能看到外面的接口。也就是說IP是某類可以不了解內部構造,僅僅需要對對外接口操作即可以使用的某類特定功能模塊。

封裝成黑盒子的好處是顯而易見的-----你無需對復雜的內部結構了如執掌,只要能做到如何使用即可。可能有人會說了:那這豈不是不符合我們從小學習的“知其然,知其所以然”?不好意思,你是工程師,你不是科學家。老板只關心你把東西做出來、做好,不會關心這個東西你到底懂不懂。

說了這么多的意思就是。Aurora IP核這個東西我們會用就行了,不用糾結它具體是怎么實現的(當然知道肯定更好,無非就是個時間性價比的問題)。那么具體到一個FPGA IP類的黑盒子,我們需要了解哪些對外接口才能把它給用起來呢?無非就是三類:

- 時鐘:對于一個系統,時鐘架構是必不可少的,根據其復雜程度,時鐘數量、種類也會不同

- 復位:一個穩健的系統,各類復位信號也是不可缺少的(要能把IP初始化成功)

- 指示:輔以數個指示信號,可以實現更好的操作、調試等交互功能

1、時鐘

時鐘看手冊好像很多,實際上真的與我們密切相關的無非就是4個。

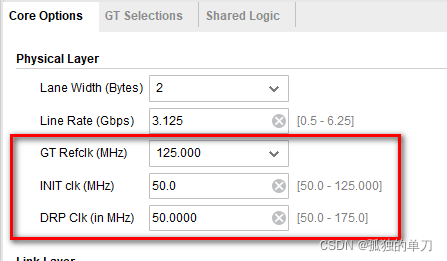

首先我們打開IP定制界面的第一頁Core Options,可以看到3個時鐘:

- GT Refclk :Aurora IP核是基于GT作為物理層實現的,所以時鐘GT Refclk就是GT的參考時鐘。GT的時鐘參考只能使用外部的差分時鐘,所以具體的值取決你板卡的硬件設計。默認125Mhz。

- INIT CLK :初始化階段的時鐘 ,在上電初始化階段,可以使用該時鐘來驅動一些邏輯。默認值:50Mhz。

- DRP CLK : DRP時鐘,動態重配置,一般沒用,默認值:50Mhz(通常一個內部模塊需要進行配置,使用兩種方法:端口控制和配置參數控制。一個常見的應用就是線速率切換。這時候就需要利用DRP端口來調整部分參數的值,然后復位GTX,使GTX工作在不同的線速率下。)。

上面這三個時鐘,是IP核工作所需要的時鐘,也是我們需要提供給IP核的。此外,還有一個時鐘是IP核提供給我們的:user_clk。這個時鐘,是IP核根據設置的線速率及Lane的位寬計算出來的用戶時鐘,用戶需要傳輸的數據必須是該時鐘域下的數據,否則會存在亞穩態風險。關于user_clk值的計算我們在下一章節再討論。

基本就能總結了:1、GT Refclk的值根據對應硬件設計的來;INIT CLK 和DRP CLK可以用PLL或者MMCM生成;3、user_clk是用戶時鐘域,我們的數據收發接口應該工作在此時鐘域下。

2、復位

復位信號一定要好好了解,不然你的IP為什么起不來你都不知道咋回事!

復位信號用于將Aurora 8B/10B核心設置為一個已知的啟動狀態。在復位時,IP核停止任何當前操作并重新初始化一個新通道。在雙工模塊上,復位信號復位通道的TX和RX兩側。

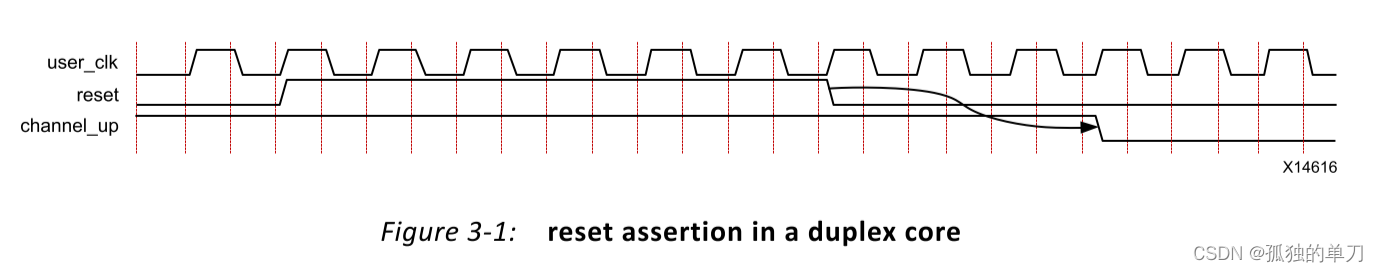

復位案例1:雙工模式下的reset復位

復位信號reset需要至少維持6個時鐘周期,然后3個周期后,channel_up信號被拉低,表示傳輸通道建立失效

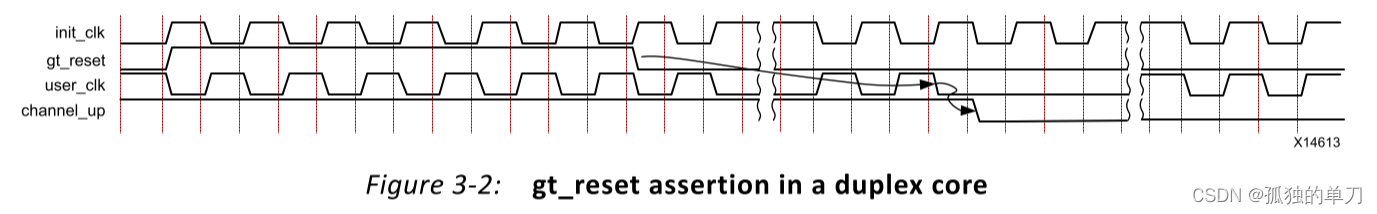

復位案例2:雙工模式下的gt_reset復位

復位信號gt_reset需要至少維持6個時鐘周期,然后一段時間后,user_clk也會失效(這是因為user_clk的時鐘來源是GT,gt_reset復位會從最底層的物理層復位),隨后channel_up信號被拉低,表示傳輸通道建立失效

單工模式的復位步驟就不講了,請參考手冊。

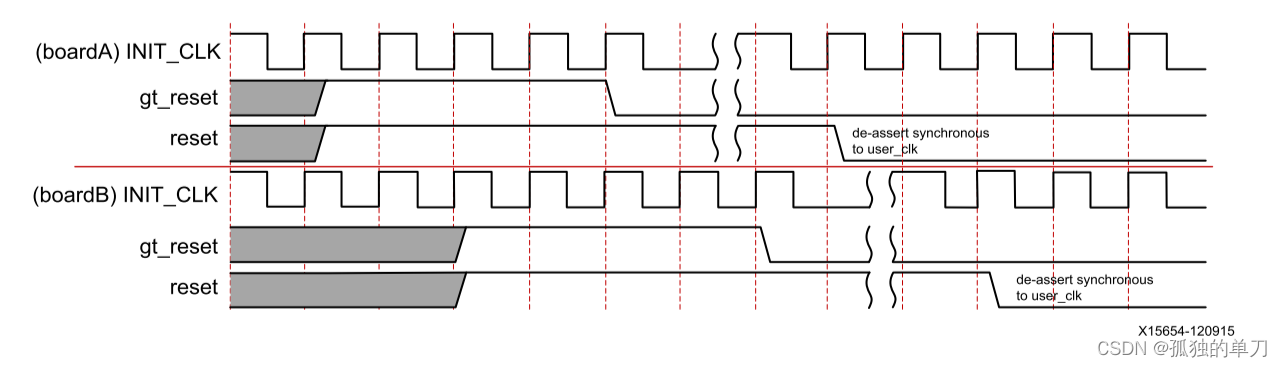

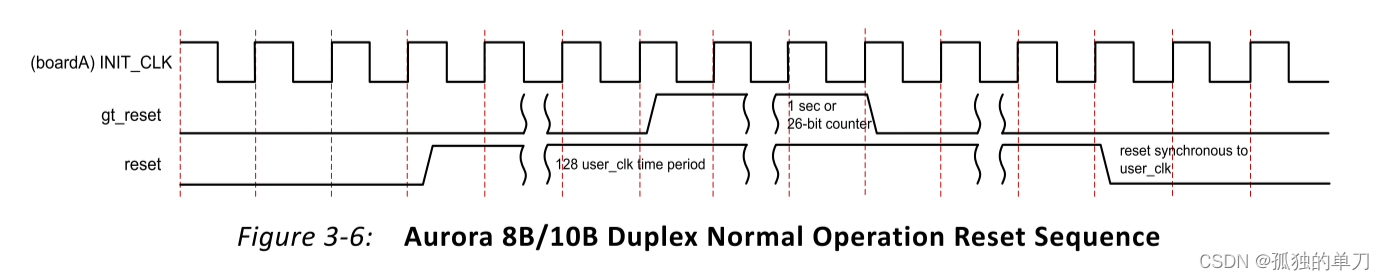

雙工模式下的上電時序

雙工模式下,給FPGA上電時,gt_reset和reset信號都必須保持為高電平,與此同時GT的參考時鐘gt_clk和初始化時鐘init_clk都必須保持穩定。

雙工模式下的正常操作復位時序

1. 在gt_reset斷言之前,reset信號必須穩定保持128個user_clk時鐘周期的斷言

2. gt_reset斷言保持一段時間(圖中所示為1s)

3. 在gt_reset取消斷言一段時間后,reset取消斷言

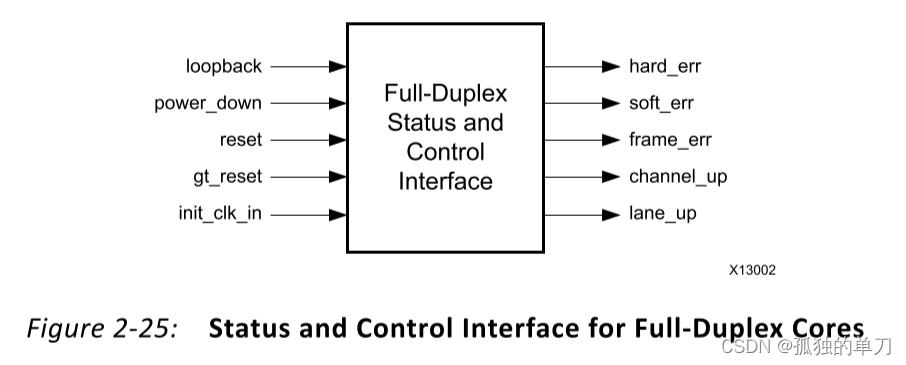

3、狀態指示

Aurora IP還提供了一系列的指示接口出來,方便我們進行調試:

- loopback:回環模式,實際使用一般接到0

- power down:高電平有效。當其為高時,GT會進入非工作、低功耗的模式(類似睡眠模式)。我們使用的時候一般直接拉低。

- lane_up:當對應的Lane初始化完成后,會斷言對應的lane_up

- channel_up:當Auroa 8b/10b 初始化完成后,并且當前已經可以進行數據的傳輸時,會斷言該信號

- hard_err:錯誤表征應信號,主要是硬件類錯誤

- soft_err:錯誤表征應信號,主要是軟件類錯誤

- frame_err:錯誤表征應信號,主要是幀類錯誤

4、其他

其他

除了上述部分外,還有一些不太常用的功能(自己看手冊吧):

- 流控:Flow Control(Native Flow Control、User Flow Control)

- 加擾/解擾:Scrambler/Descrambler

- 循環冗余校驗:Cyclic Redundancy Check,CRC

預告

下一節我們再來一起學習下Aurora IP核的example design(兩種接口一起)。

參考

Aurora 8B/10B Protocol Specification

Aurora 8B/10B v11.1 LogiCORE IP Product Guide

審核編輯:符乾江

-

時鐘

+關注

關注

10文章

1721瀏覽量

131378 -

AURORA

+關注

關注

0文章

25瀏覽量

5389

發布評論請先 登錄

相關推薦

在FPGA里面例化了8個jesd204B的ip核同步接收8塊AFE芯片的信號,怎么連接設備時鐘和sysref到AFE和FPGA?

【米爾-Xilinx XC7A100T FPGA開發板試用】+04.SFP之Aurora測試(zmj)

LMK05318B LOPL_DPLL狀態在外部輸入時鐘斷開又恢復時無法清除怎么辦?

光纜8d與8b區別

TAS5805的I2C地址配置的是7b:2D,8b:5A怎么出來是7b:2F,8b:5E?這個是什么原因?

線路故障指示器如何復位

具有電源正常狀態指示功能的TPS7B87-Q1 500mA、40V、低壓降穩壓器數據表

8b10b編碼verilog實現

山東易信推出高豐度核級10B酸及高純11BF3電子特氣新材料,計劃2022年應用

PCIE相關概念和帶寬計算方法

Aurora 8B/10B IP核(二)—時鐘、復位與狀態指示

Aurora 8B/10B IP核(二)—時鐘、復位與狀態指示

評論