一、Aurora協議

Aurora 是一個用于在點對點串行鏈路間移動數據的可擴展輕量級鏈路層協議。這為物理層提供透明接口,讓專有協議或業界標準協議上層能方便地使用高速收發器。雖然使用的邏輯資源非常少,但 Aurora 能提供低延遲高帶寬和高度可配置的特性集。在 Xilinx FPGA 上使用是免費的,而且在 ASIC 上能以名義成本通過單獨的許可證協議得到支持。

主要特性:

1. 高帶寬,僅受限于收發器的數據速率

2. 支持大量鍵合線路,實現較高的總帶寬

3. 支持全雙工和單工通道

4. 無限幀尺寸/靈活組幀

5. 小型邏輯封裝,采用標準的 AXI-ST 接口。

6. 內置流程控制和熱插拔支持

Aurora 廣泛用于需要背板、電路板間和芯片間連接的應用。細分市場包括有線通信、存儲、服務器、測試測量、工業、消費和醫療等。此外,Aurora 也可用作嵌入式處理器應用中的調試端口。

二、Xilinx平臺Aurora IP介紹

Xilinx提供了兩個Aurora核,分別是:Aurora 8B/10B 以及Aurora 64B/66B。

顧名思義,主要是8B/10B ,64B/66B的區別;8B/10B編碼可以平衡DC,有足夠的跳變來恢復時鐘,但是有20%的帶寬開銷。64B/66B編碼的前兩位表示同步頭,減小的開銷,但是卻不能保證0/1數量的平衡,因此需要進行加繞。

上面簡單介紹了8B/10B, 64B/66B;但是對于我們使用IP核來說,步驟其實是一樣的。這里以Aurora 8B/10B進行介紹。

三、Aurora IP組成結構

3.1總覽

看圖說話,我們簡單分析一下:

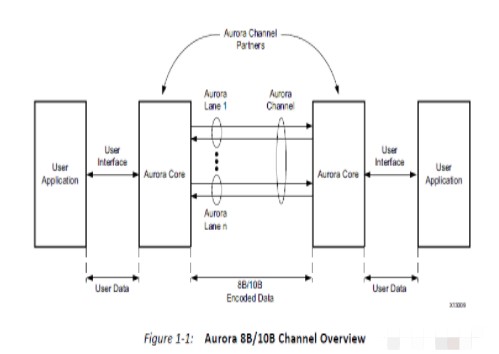

兩個Aurora核,建立一個Channel,這兩個核就稱為Aurora Channel Partners。但是,這個Channel又可以是多條lane,每條lane對應一個高速收發器GT。8B/10B編碼后的數據就是通過GT傳輸。所以,我們可以認識到,高速接口物理層都是基于GT。關于GT,可以參考:https://blog.csdn.net/m0_52840978/article/details/121455025?spm=1001.201... FPGA平臺GTX簡易使用教程(匯總篇)

那么,數據發送的過程呢?首先,用戶數據經過用戶接口傳給Aurora核,Aurora核通過Aurora Channel(可能多條lane)將編碼后的串行數據發送到另一端的Aurora核進行接收,解碼,串并轉換,最后將用戶數據給到用戶應用。

3.2框圖

我們繼續來看Aurora 8B/10B的框圖:

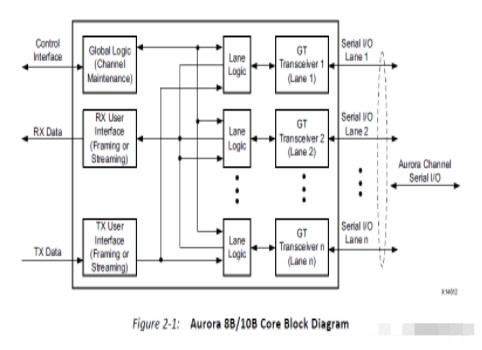

Aurora 8B/10B核的主要功能模塊包括:

1. Lane Logic: 每條lane都包含一個GT,Lane邏輯模塊實體驅動每個GT,并初始化每個GT收發器,處理編解碼及錯誤檢測等。

2. Global Logic: 全局邏輯模塊執行通道初始化的綁定和驗證階段。 在運行過程中,模塊生成Aurora協議所需的隨機空閑字符,并監控所有lane邏輯模塊的錯誤。

3. RX User Interface: 接收端用戶接口使用AXI4-S接口將數據從channel傳到用戶應用并可進行接收流控功能。

4. TX User Interface: 發送端用戶接口使用AXI4-S接口將數據從用戶應用傳到channel并進行發送流控功能。標準時鐘補償模塊嵌入在核中。這個模塊控制時鐘補償(CC)字符的周期性傳輸。

3.3頂層結構

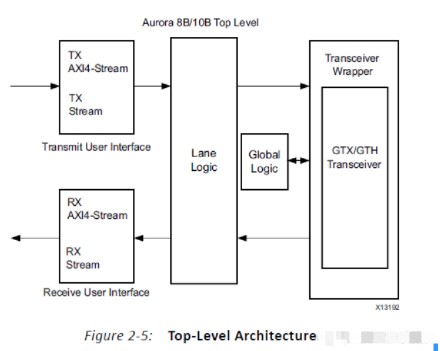

Aurora 8B/10B核的頂層文件實例化了lane logic模塊TX和RX 的AXI4-Stream模塊、全局邏輯模塊和收發器的封裝模塊在Example Design中也實例化了時鐘和復位電路、幀生成模塊和檢查模塊。

下圖是一個全雙工配置的Aurora 8B/10B:

審核編輯:湯梓紅

-

收發器

+關注

關注

10文章

3401瀏覽量

105872 -

Xilinx

+關注

關注

71文章

2164瀏覽量

121032 -

測量

+關注

關注

10文章

4780瀏覽量

111144

發布評論請先 登錄

相關推薦

思嵐科技SLAMTEC Aurora在智能割草機器人中的應用

【米爾-Xilinx XC7A100T FPGA開發板試用】+04.SFP之Aurora測試(zmj)

Zebra Aurora深度學習OCR算法榮獲CAIMRS頒發的自動化創新獎

映泰發布A620MH Aurora主板,支持DDR5內存,配備32條PCIe通道

英飛凌攜手Aurora Labs為汽車行業提供優化的預測性維護解決方案

英飛凌攜手Aurora Labs為汽車行業提供優化的預測性維護解決方案, 提升駕駛安全至全新水平

Xilinx平臺Aurora IP介紹(一)Aurora基礎知識

Xilinx平臺Aurora IP介紹(一)Aurora基礎知識

評論