?在FPGA的時序約束中,主時鐘約束是第一步就要做的,主時鐘通常有兩種情形:一種是時鐘由外部時鐘源提供,通過時鐘引腳進入FPGA,該時鐘引腳綁定的時鐘為主時鐘:另一種是高速收發器(GT)的時鐘RXOUTCLK或TXOUTCLK。對于7系列FPGA,需要對GT的這兩個時鐘手工約束:對于UltraScale FPGA,只需對GT的輸入時鐘約束即可,Vivado會自動對這兩個時鐘約束。

??對于進入到IP Core(比如MMCM)的主時鐘,只有我們在IP Core中指定了時鐘頻率,那么Vivado會自動產生一個約束文件來約束該輸入的主時鐘。

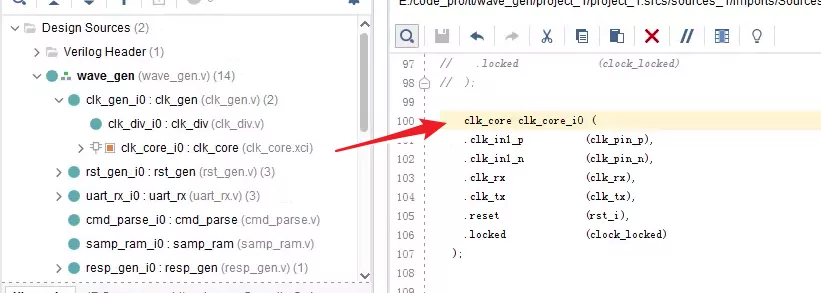

??我們以Vivado自帶的wave_gen工程為例,該工程中輸入一對差分的時鐘信號,進入到MMCM中,我們無需再對這個主時鐘添加約束。

可以看到,綜合后這個時鐘已經被約束了:

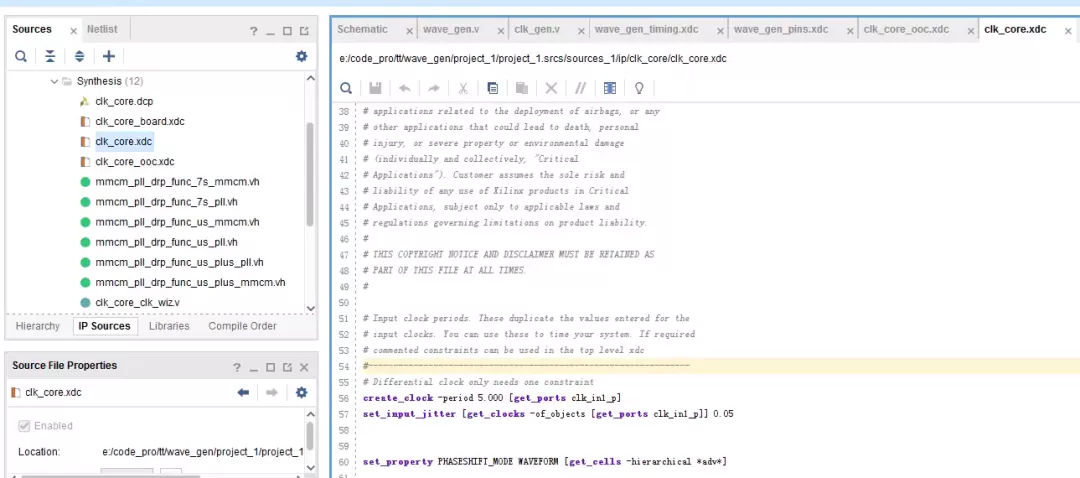

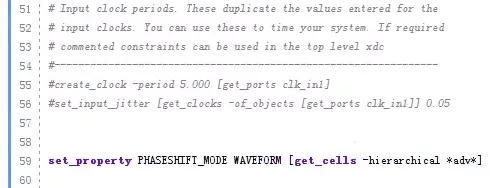

這是因為該ip生成的xdc文件中,已經包含了對這個主時鐘的約束,如下圖:

所以很多同學可能誤以為只要是進了IP Core的主時鐘,都不需要再手動添加約束了。

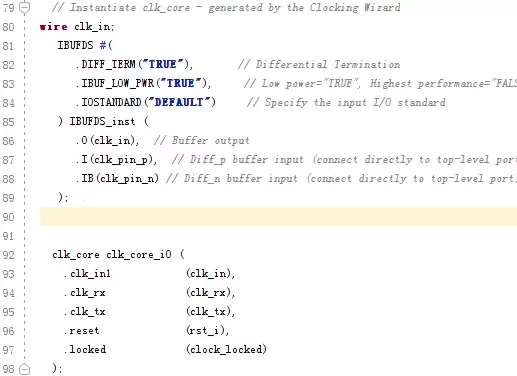

??但如果收入的差分時鐘先經過了IBUFDS,然后再以單獨的形式進入了MMCM:

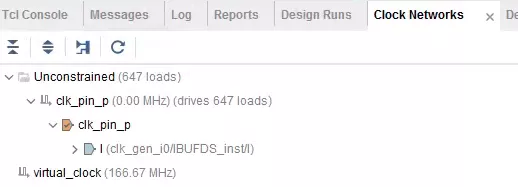

綜合后,可以看到該時鐘是沒有被約束的:

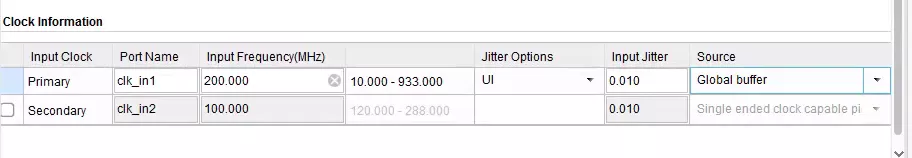

此時由于輸入時鐘并非來自管腳,所以Source選擇為Global Buffer

再看剛剛的clk_core.xdc文件,已經沒有產生主時鐘的約束了:

為什么會沒有這個約束了呢?因為輸入的時鐘并非來自管腳,IP Core并不知道從哪個pin輸入的,所以就無法添加主時鐘的約束,此時就需要我們再手動添加約束。

審核編輯:符乾江

-

FPGA

+關注

關注

1626文章

21675瀏覽量

601953 -

Vivado

+關注

關注

19文章

808瀏覽量

66339

發布評論請先 登錄

相關推薦

深控技術研發的 “不需要點表的工業網關” 在 CNC 采集方面的應用

不需要點表的工業網關應用案例:如何提升工業企業生產效率與質量?

不需要點表的 PLC 工業網關 在印刷 / 包裝行業的實施案例

C語言為什么不需要包含stdio.h

基于 “不需要點表的工業網關” 的工業自動化設備遠程監控解決方案

進入IP Core的時鐘,都不需要再手動添加約束嗎

進入IP Core的時鐘,都不需要再手動添加約束嗎

評論