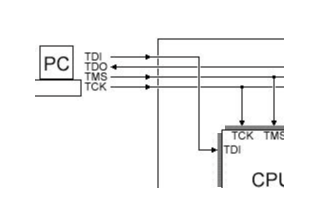

對FPGA進行上板調試時,使用最多的是SignalTap,但SignalTap主要用來抓取信號時序,當需要發送信號到FPGA時,Jtag Master可以發揮很好的作用,可以通過Jtag Master對FPGA進行讀寫測試,使用tcl腳本控制Jtag Master可以完成復雜的測試功能。使用jtag master進行調試時分為如下步驟:

- 將JTAG to Avalon Master Bridge Intel FPGA IP加入代碼

- 根據Avalon-MM總線時序編寫測試代碼

- 編寫tcl腳本

- 在System Console上運行tcl腳本進行調試

Jtag Master

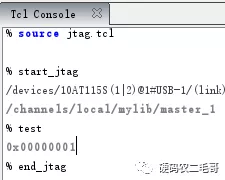

在邏輯代碼中加入JTAG to Avalon Master Bridge Intel FPGA IP ,IP路徑如下。

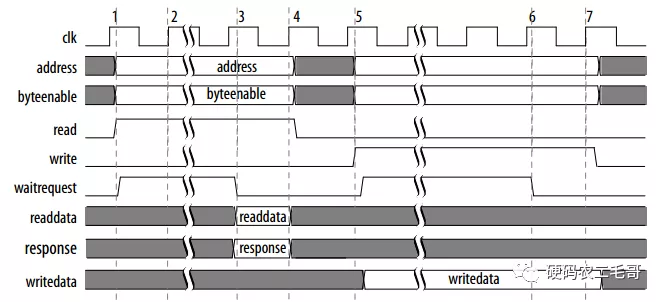

Avalon-MM總線時序

jtag_master模塊例化到fpga代碼中,使用Verilog根據Avalon-MM時序圖編寫讀寫代碼。master_read有效時將數據發送到master_readdata。master_write有效時,將master_writedata數據寫入FPGA。

jtag_master u0 (

.clk_clk (_connected_to_clk_clk_),

.clk_reset_reset (_connected_to_clk_reset_reset_),

.master_reset_reset (_connected_to_master_reset_reset_),

.master_address (_connected_to_master_address_),

.master_readdata (_connected_to_master_readdata_),

.master_read (_connected_to_master_read_),

.master_write (_connected_to_master_write_),

.master_writedata (_connected_to_master_writedata_),

.master_waitrequest (_connected_to_master_waitrequest_),

.master_readdatavalid (_connected_to_master_readdatavalid_),

.master_byteenable (_connected_to_master_byteenable_)

);

編寫TCL腳本

global claimed_path_jtag

#啟動jtag master服務

proc start_jtag {} {

set service_type "master"

set jtag_path [lindex [get_service_paths $service_type] 0]

puts $jtag_path

set ::claimed_path_jtag [claim_service $service_type $jtag_path mylib]

}

# 下載函數

proc config {sof_file} {

set device_index 0

set device [lindex [get_service_paths device] $device_index]

puts "download..."

device_download_sof $device $sof_file

}

#關閉jtag master服務

proc end_jtag {} {

close_service master $::claimed_path_jtag

}

#寫函數

proc jtag_write {addr data} {

master_write_32 $::claimed_path_jtag $addr $data

}

#讀函數

proc jtag_read {addr} {

set result [master_read_32 $::claimed_path_jtag $addr 1]

return $result

}

#測試讀寫

proc test { } {

#地址0中寫入1

jtag_write 0x0 0x1

#讀取地址0

jtag_read 0x0

}

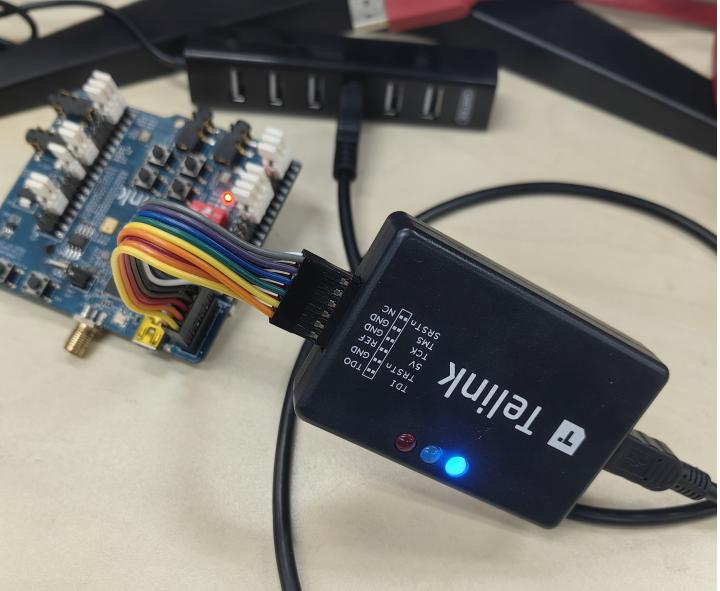

上電測試

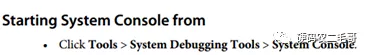

打開System Console

運行如下指令

source jtag.tcl //tcl 腳本

config output_files/test.sof //下載文件

start_jtag //打開jatg master服務

test //測試讀寫函數

end_jtag //關閉jatg master服務

審核編輯:符乾江

-

FPGA

+關注

關注

1626文章

21666瀏覽量

601837 -

程序

+關注

關注

116文章

3777瀏覽量

80849

發布評論請先 登錄

相關推薦

【GD32 MCU 入門教程】二、GD32 MCU 燒錄說明 (2)SWD/JTAG在線下載

如何使用JTAG來調試ESP-12模塊?

STM32F407調試接口報錯SWD/JTAG Communic怎么解決?

FPGA的JTAG口很脆弱?以后要多加小心了

RISCV soft JTAG調試_v1.2

RISCV soft JTAG調試_v1.1

如何使用linux下gdb來調試python程序

關于JTAG口,你了解多少?

jtag接口和swd接口區別

JTAG如何工作?是誰動了我的JTAG口?

使用Jtag Master來調試FPGA程序

使用Jtag Master來調試FPGA程序

評論