1、綜合-優化資源

當選擇為none,綜合器優化的最少,當選擇為full時,綜合器優化的最多,選擇rebuilt時,工具自動選擇一個折中的方案,對當前工程做優化。如果在rebuilt的選項不希望一些信號被優化,則可以調用原語進行約束。

對于模塊,想保留該模塊的層次結構

(* keep_hierarchy=“yes” )

對于信號,在實際使用中,最好作用于寄存器,有的wire即使約束,也會被優化。

( keep=“true” )

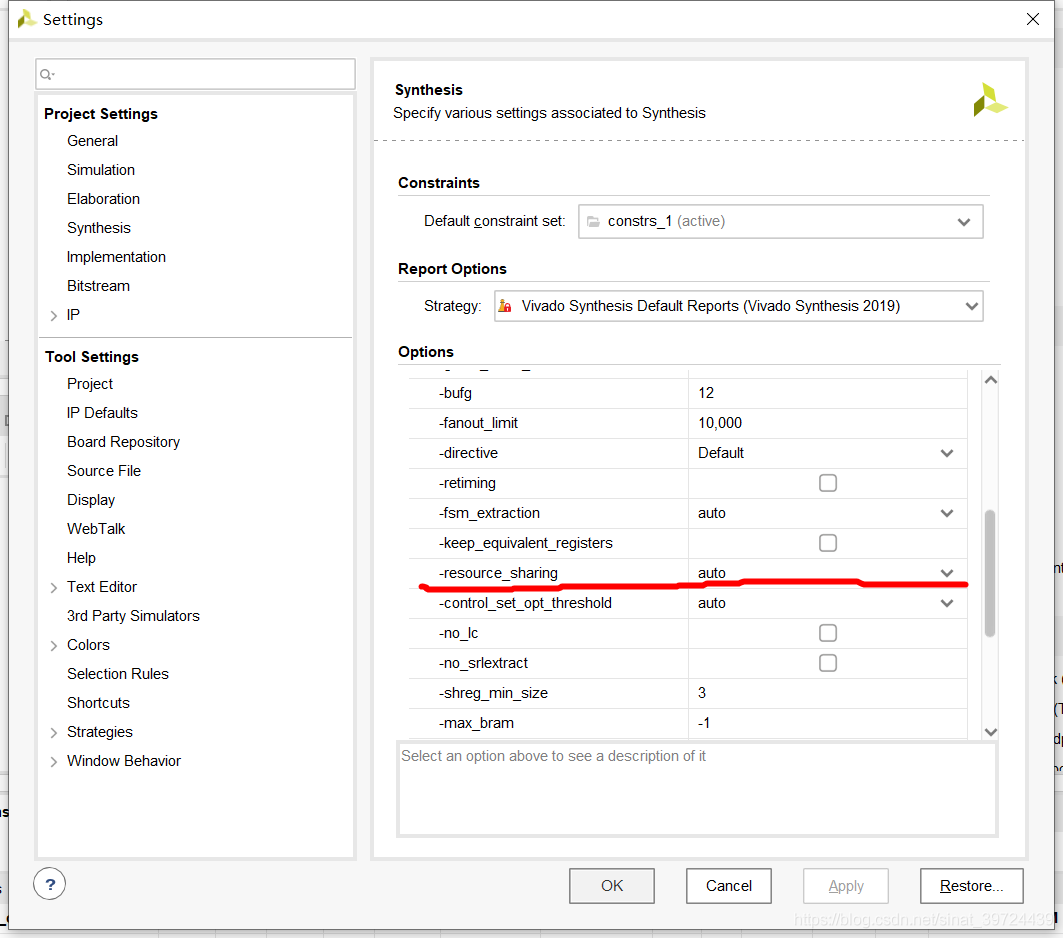

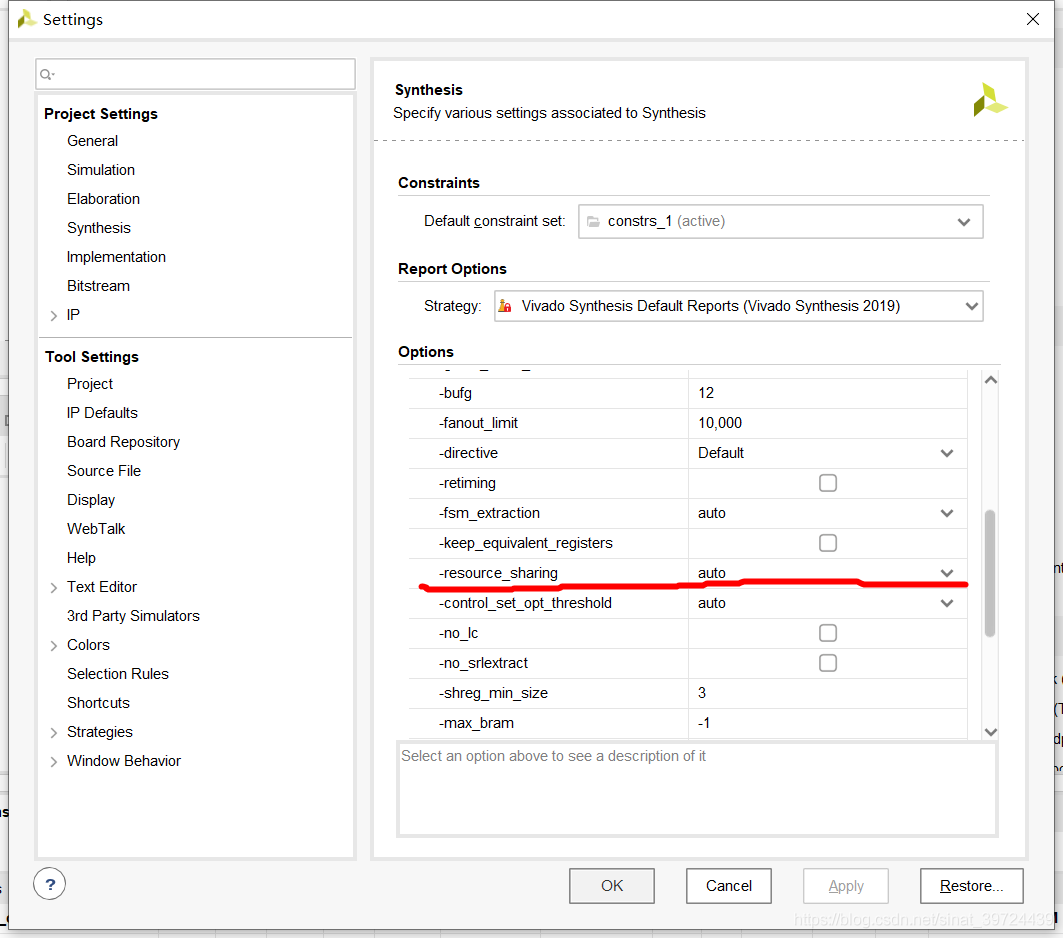

2、綜合-資源共享

當選擇為on時,使能資源共享,當選擇為off時,關閉資源共享,當選擇為auto時,綜合器會根據時序的余量自動選擇是否啟動資源共享。

注意,此此選項只對當前代碼中加減乘有影響。

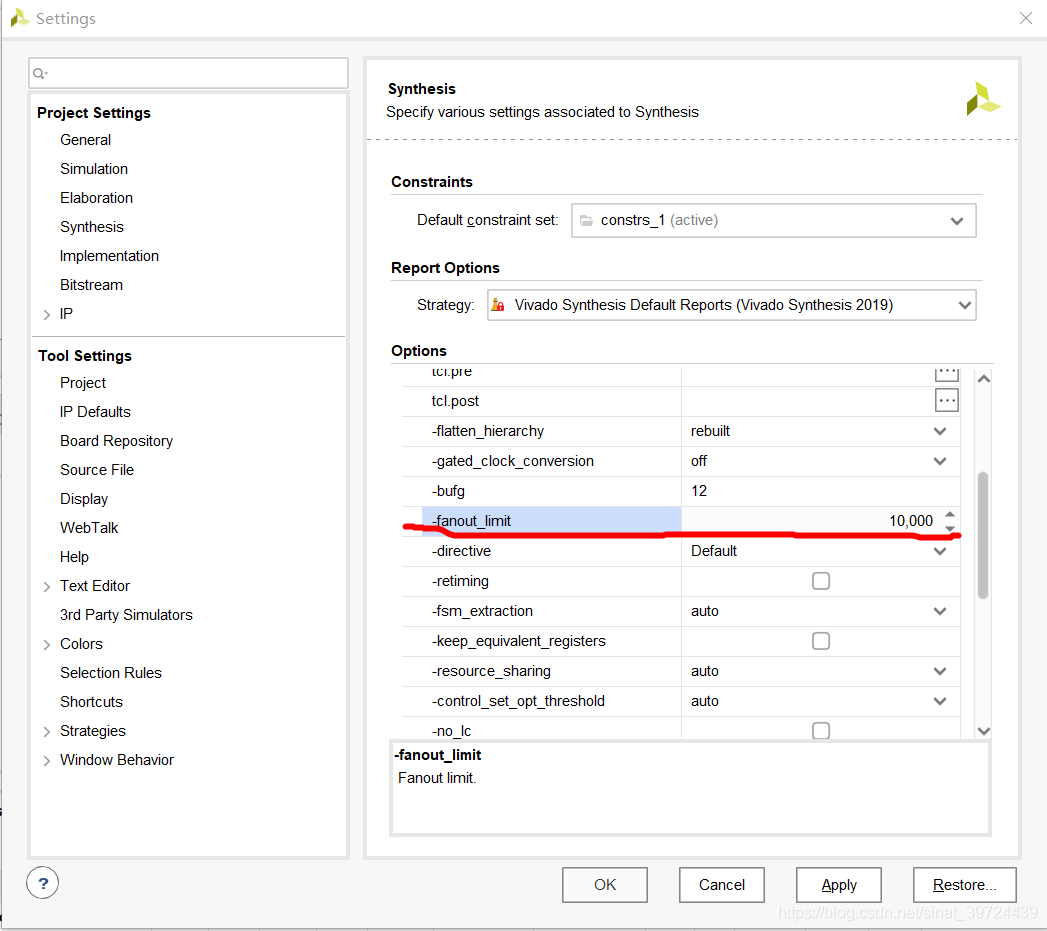

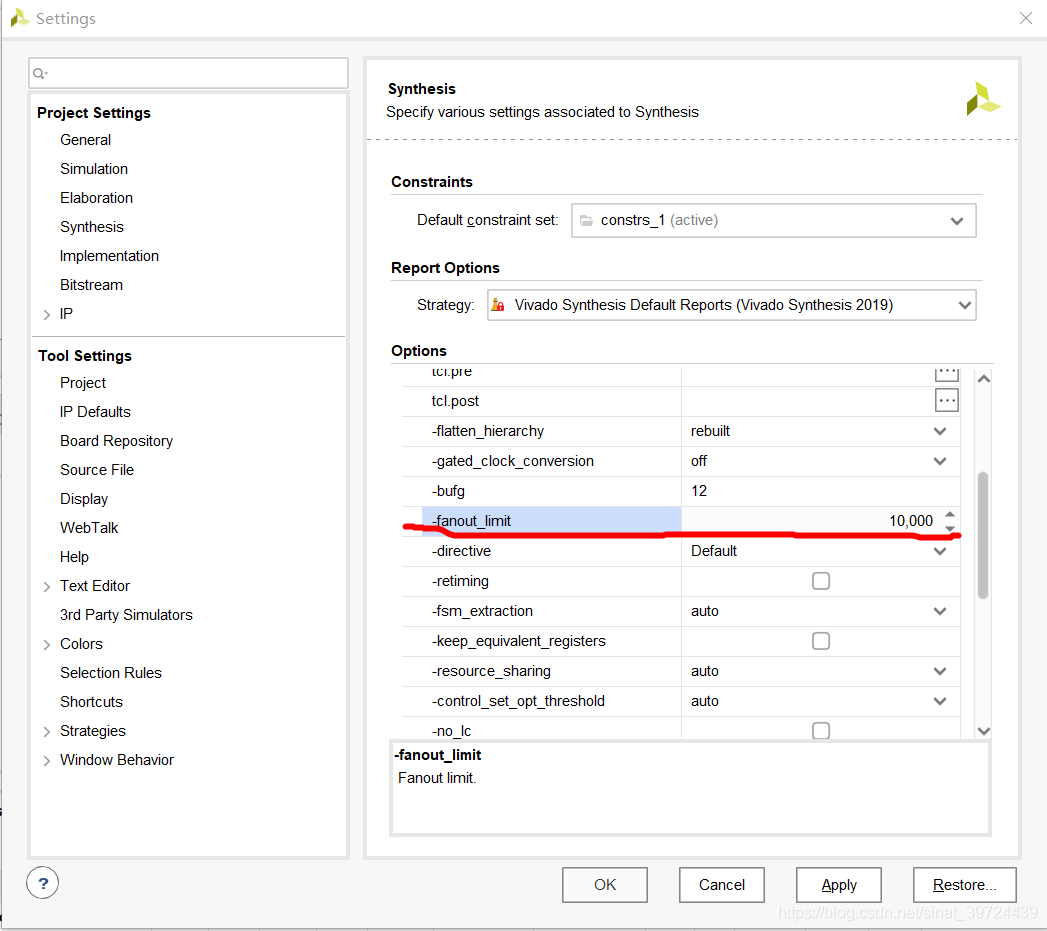

3、綜合-扇出限制

默認是10000,這只是一個籠統的全局設置,對復位無效。

對于單一信號的扇出約束,使用約束

( max_fanout= *)

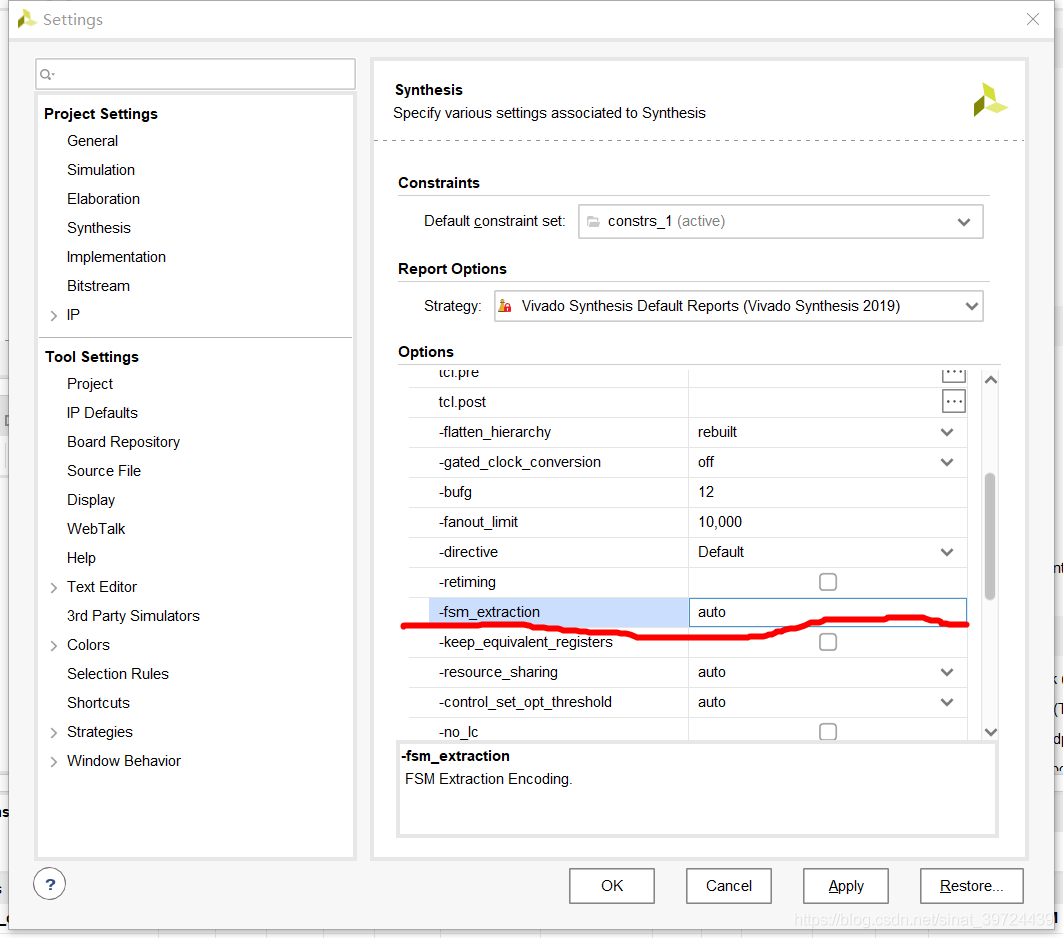

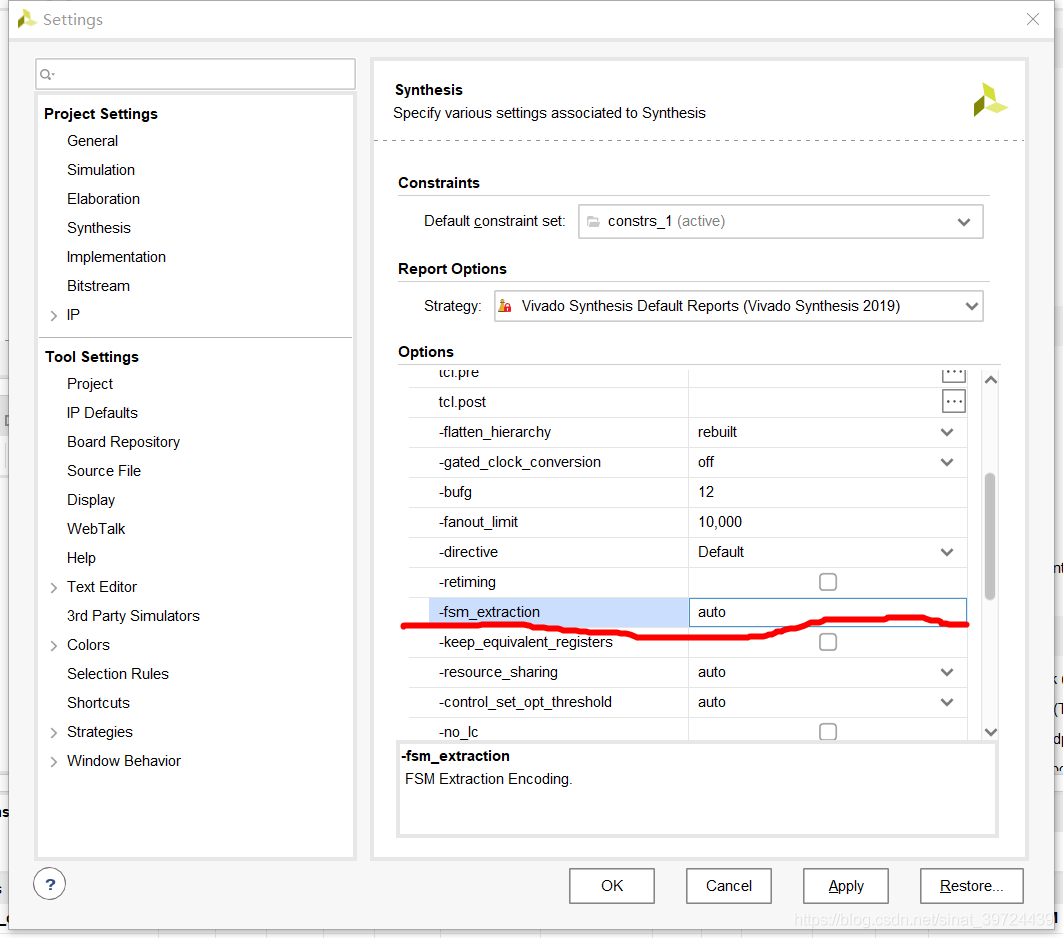

4、狀態機的編碼方式

當選擇為auto時,綜合器會根據當前的代碼,自動選擇最有的編碼方式。

審核編輯:湯梓紅

![]()

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

相關推薦

AMD Alveo 加速卡使用有兩種流程,AMD Vitis Software Platform flow 和 AMD Vivado Design Tool flow。比較常見的是 Vitis

![的頭像]() 發表于

發表于 11-13 10:14

?106次閱讀

有時我們對時序約束進行了一些調整,希望能夠快速看到對應的時序報告,而又不希望重新布局布線。這時,我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時序約束。如果調整

![的頭像]() 發表于

發表于 10-24 15:08

?212次閱讀

網關的設置規則涉及多個方面,包括硬件安裝、網絡連接、基本配置、高級配置以及安全設置等。以下是一篇關于網關設置規則的詳細指南,旨在幫助用戶正確配置和管理網關設備。

![的頭像]() 發表于

發表于 09-30 11:48

?1221次閱讀

從綜合角度看,Vivado 2024.1對SystemVerilog和VHDL-2019的一些特性開始支持。先看SystemVerilog。

![的頭像]() 發表于

發表于 09-18 10:34

?653次閱讀

Vivado 2024.1已正式發布,今天我們就來看看新版本帶來了哪些新特性。

![的頭像]() 發表于

發表于 09-18 10:30

?982次閱讀

,用戶可直接在simulink下綜合出網表和約束文件,打包至.dcp文件中,用戶可在vivado下直接加載dcp文件調用模型。

4、直接在vivado中添加模型文件(推薦)。

Viv

發表于 04-17 17:29

Xilinx Vivado開發環境編譯HDL時,對時鐘信號設置了編譯規則,如果時鐘由于硬件設計原因分配到了普通IO上,而非_SRCC或者_MRCC專用時鐘管腳上時,編譯器就會提示錯誤。

![的頭像]() 發表于

發表于 04-15 11:38

?4794次閱讀

電纜隧道作為城市電力供應、信息傳輸和能源輸送的重要通道,其安全和穩定性對城市的正常運行至關重要。因此,一個高效、智能的電纜隧道綜合監控管理平臺的規劃設置就顯得尤為關鍵。本文深圳鼎信智慧科技將詳細探討

![的頭像]() 發表于

發表于 04-09 18:01

?485次閱讀

將設置設計的輸出路徑,設置設計輸出路徑的步驟如下所示。 第一步:如圖4.3所示,在“Vivado%”提示符后輸入命令“set outputDir ./gate_Created_Data/top_output”。

發表于 04-03 09:34

?1440次閱讀

要求

1.ISP路由器只能配置IP地址,之后不進行任何配置

2.內部整個網絡基于192.168.1.0/24進行地址劃分

3.R1/2之間啟動OSPF協議,單區域

4.PC1-4自動獲取IP地址

5.PC1不能telnetR1,PC1外的其余內網PC可以telnet

![的頭像]() 發表于

發表于 03-21 11:43

?535次閱讀

摘要:城市綜合管廊的供配電系統設計多種多樣,通過對綜合管廊自用負荷的分析及安全運行的因素考慮,并結合綜合管廊設計案例,簡要總結綜合管廊供配電

發表于 01-19 17:32

在Vivado中禁止自動生成BUFG(Buffered Clock Gate)可以通過以下步驟實現。 首先,讓我們簡要了解一下什么是BUFG。BUFG是一個時鐘緩沖器,用于緩沖輸入時鐘信號,使其更穩

![的頭像]() 發表于

發表于 01-05 14:31

?1974次閱讀

有些時候在寫完代碼之后呢,Vivado時序報紅,Timing一欄有很多時序問題。

![的頭像]() 發表于

發表于 01-05 10:18

?1923次閱讀

vivado出現安裝問題剛開始還以為是安裝路徑包含中文空格了,重裝的注意了一下,發現還是這個問題。。。。后來又一頓操作猛如虎,終于發現了問題。出這個問題的原因是vivado壓縮包解壓的路徑包含中文了把解壓文件放到不含中文的地方,再重新安裝,安裝路徑也不能含中文。然后。。。

發表于 12-22 10:56

?0次下載

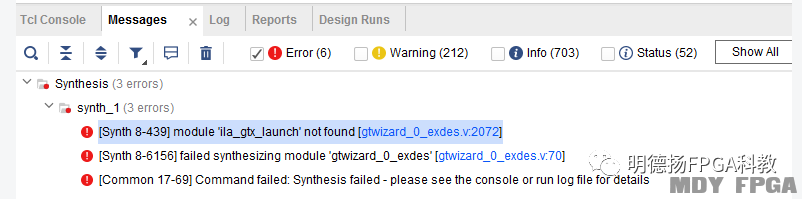

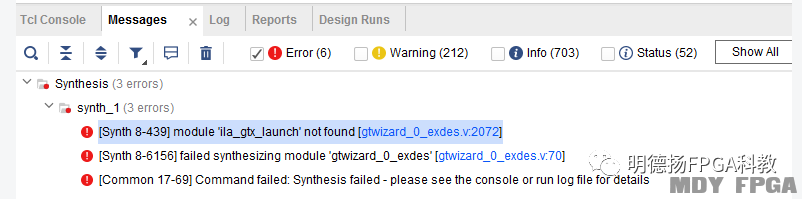

【關鍵問題!!!!重要!!!】VIVADO會在MESSAGE窗口出提示很多錯誤和警告信息!

![的頭像]() 發表于

發表于 12-15 10:11

?1790次閱讀

關于Vivado綜合設置使用總結

關于Vivado綜合設置使用總結

評論